擁有更佳的電性參數,并且得益于12英寸制程的穩定性,良率優異,為數字電源、數字音頻功放等芯片應用提供了更具競爭力的制造方案。 作為全球領先的特色工藝純晶圓代工企業,華虹半導體擁有先進的模擬及電源管理IC工藝平臺,涵蓋0.5微米到90納米工藝節點,

2021-06-04 09:36:17 7273

7273 據國際物理系統研討會(ISPD)上專家表示:實現14納米芯片生產可能會比原先想象的更困難;14納米節點給設計師帶來了許多挑戰。這些困難和挑戰何在?詳見本文...

2013-04-08 09:30:51 3956

3956 Cadence設計系統公司(Cadence Design Systems, Inc.)(納斯達克代碼:CDNS)今日宣布與TSMC簽訂了一項長期合作協議,共同開發16納米FinFET技術,以其適用于

2013-04-09 11:00:05 1123

1123 楷登電子今日正式發布Cadence? Virtuoso?定制 IC設計平臺的技術升級和擴展,進一步提高電子系統和 IC設計的生產力。新技術涉及Virtuoso 系列幾乎所有產品,旨在為系統工程師提供更穩健的設計環境和生態系統,助其實現并分析復雜芯片、封裝、電路板和系統。

2018-04-11 16:40:16 10275

10275 技術節點的每次進步都要求對制造工藝變化進行更嚴格的控制。最先進的工藝現在可以達到僅7 nm的fin寬度,比30個硅原子稍大一點。半導體制造已經跨越了從納米級到原子級工藝的門檻。

2020-06-02 18:04:46 3006

3006

這是一個業界用于打造差異化定制芯片的領先平臺,可借助生成式 AI 技術顯著提升設計生產力; Virtuoso Studio 與 Cadence 最前沿的技術和最新的底層架構集成,助力設計工程師在

2023-04-20 15:52:13 1036

1036

3nm 時代來臨了!Cadence 在 2023 年 TSMC 北美技術研討會期間發布了面向臺積電 3nm 工藝(N3E)的 112G 超長距離(112G-ELR)SerDes IP 展示,這是

2023-05-19 16:25:12 1405

1405

有參考價值的信息。 英特爾路線圖 從7nm到1.4nm 首先將目光放到最遠,英特爾預計其工藝制程節點將以2年一個階段的速度向前推進。從2019年推出10nm工藝開始(實際產品在市場上非常少見

2020-07-07 11:38:14

(Microcontroller Unit, MCU)市場,最新推出95納米單絕緣柵非易失性嵌入式存儲器(95納米5V SG eNVM)工藝平臺。在保證產品穩定性能的同時,95納米5V SG eNVM工藝平臺以其低功耗、低成本

2017-08-31 10:25:23

各位大佬好,我正在學習IC設計,對于Cadence Virtuoso這個軟件有一些入門級的小問題:我從AnaglogLib拷貝NMOS管和PMOS管到自己的library下面,打開他們的CDF參數看

2017-10-16 00:26:33

Cadence設計系統公司發布了Cadence Allegro系統互連設計平臺針對印刷電路板(PCB)設計進行的全新產品和技術增強。改進后的平臺為約束驅動設計提供了重要的新功能,向IC、封裝和板

2018-11-23 17:02:55

結合了 3D 探索流程,利用 2D 設計網表根據用戶輸入創建多個 3D 堆疊場景,自動選擇最佳的最終 3D 堆疊配置。此外,平臺數據庫支持所有 3D 設計類型,讓工程師可以同時在多個工藝節點創建

2021-10-14 11:19:57

cadence virtuoso教程? 1990-2006 Cadence Design Systems, Inc. All rights reserved.Printed

2012-08-10 18:37:59

PDK 套件支持我們先進的一流 IPD1 和 IPD2 工藝。此款 PDK 套件配備完全可擴展的布局參數單元 (Pcell)、先進布局實用程序以及準確的電磁 (EM) 仿真功能。此套件可應客戶要求供下載

2018-10-26 08:54:41

納米定位平臺跟納米平臺的區別是什么?

2015-07-19 09:42:13

工藝節點中設計,但是 FD-SOI 技術提供最低的功率,同時可以承受輻射效應。與體 CMOS 工藝相比,28 納米 FD-SOI 芯片的功耗將降低 70%。射頻數據轉換器需要同時具有高帶寬和低功耗,以

2023-02-07 14:11:25

`7納米芯片一直被視為芯片業“皇冠上的珍珠”,令全球芯片企業趨之若鶩。在大家熱火朝天地競相布局7納米工藝時,全球第二大的芯片大廠GlobalFoundries(格羅方德,格芯,以下簡稱GF)突然宣布

2018-09-05 14:38:53

LS2088A的工藝節點是什么?

2023-03-17 07:12:36

:不同代工廠、不同工藝節點、不同工藝平臺、不同工藝版本等 基于器件/工藝評估的設計輔助功能 模型庫的質量和精度驗證 內嵌超過200多個檢查項的預先配置的模板 并行處理引擎,支持內嵌和外置SPICE

2020-07-01 09:34:29

STM32WL MCU 的生產工藝(nm)是多少?我們正在考慮設計一個系統,該系統必須在可能的輻射環境中運行,而工藝的納米尺寸將對此產生影響。

2022-12-26 07:15:25

`書籍:《炬豐科技-半導體工藝》文章:GaN 納米線制造和單光子發射器器件應用的蝕刻工藝編號:JFSJ-21-045作者:炬豐科技網址:http://www.wetsemi.com

2021-07-08 13:11:24

什么是納米?為什么制程更小更節能?為何制程工藝的飛躍幾乎都是每2年一次?

2021-02-01 07:54:00

系統,為廣大國內外用戶降低設計門檻。另外,該系統采用的是跨平臺開發,既適用于UNIX也適用于Windows操作系統,兼容其他MEMS CAD工具軟件,如L-EDIT、ANSYS等,還支持用戶自主擴展其他功能模塊。

2019-06-25 06:41:25

關于黑孔化工藝流程和工藝說明,看完你就懂了

2021-04-23 06:42:18

一半,而性能提高兩倍。通過選擇一個高性能低功耗的工藝技術,一個覆蓋所有產品系列的、統一的、可擴展的架構,以及創新的工具,賽靈思將最大限度地發揮 28 納米技術的價值, 為客戶提供具備 ASIC 級功能

2019-08-09 07:27:00

小白求助,cadence里通過Library Path Editor添加工藝庫文件最后一步是點擊File下面的save,但是它是灰色的點不了,不知道該如何解決,求大佬指點一二,感激不盡。

2021-06-25 06:26:01

FPGA在系統中表現出的特性是由芯片制造的半導體工藝決定的,當然它們之間的關系比較復雜。過去,在每一節點會改進工藝的各個方面,每一新器件的最佳工藝選擇是尺寸最小的最新工藝。現在,情況已不再如此。

2019-09-17 07:40:28

英特爾聯合創始人戈登·摩爾在半世紀前提出的摩爾定律,是指每代制程工藝都要讓芯片上的晶體管數量翻一番。縱觀芯片每代創新歷史,業界一直遵循這一定律,并按前一代制程工藝縮小約 0.7倍來對新制程節點命名

2019-07-17 06:27:10

表示將在2015年年底開始量產10nm晶圓,但在10納米工藝制程上遇到了瓶頸及一系列因素,致該計劃最終一拖再拖,英特爾公司首席執行官Brian Krzanich曾表示,下一代先進制程大約要等到2017

2016-01-25 09:38:11

請問各位大佬,Cadence610能同時裝兩個工藝庫嗎,例如TSMC和SMIC同時裝上?

2021-06-25 07:42:12

納米磁性薄膜材料的濕法工藝馮則坤,何華輝關鍵詞:納米薄膜,磁性材料,電鍍摘 要:介紹了納米磁性薄膜材料特性、類型,綜述了近年來興起的濕法工藝及其用濕法

2010-02-07 16:42:46 37

37 臺積電率先量產40納米工藝

臺積電公司日前表示,40納米泛用型(40G)及40納米低耗電(40LP)工藝正式進入量產,成為專業集成電路制造服務領域唯一量產40納米工藝的公司

2008-11-22 18:27:07 1112

1112 隨著微電子技術的進步,超大規模集成電路(VLSI)的特征尺寸已經步入納米范圍。納米級工藝存在著很多不同于以往微米、亞微米工藝的特點,因此為制造和設計都帶來了很多難題,諸

2011-05-28 16:36:27 0

0 ARM處理器部門主管西蒙·賽加斯(Simon Segars)周一在Computex大展上表示,采用20納米工藝生產的ARM芯片最快將于明年底發布

2012-06-05 08:57:19 1108

1108 ARM處理器部門主管西蒙·賽加斯(SimonSegars)周一在Computex大展上表示,采用20納米工藝生產的ARM芯片最快將于明年底發布。賽加斯說:“整個行業都推進下一代技術,只要在經濟和技

2012-06-06 08:55:04 1665

1665 Cadence與三星的合作為移動消費電子產品帶來了新的工藝進展,使得20納米及未來工藝節點設計成為可能。

2012-06-10 10:43:54 1438

1438 隨著芯片微縮,開發先進工藝技術的成本也越來越高。TSMC對外發言人孫又文表示,臺積電會繼續先進工藝技術節點的投入和開發,今年年底臺積電將推出20nm工藝

2012-08-30 14:34:30 2301

2301 全球電子設計創新領先企業Cadence設計系統公司日前宣布TSMC已選擇Cadence解決方案作為其20納米的設計架構。Cadence解決方案包括Virtuoso定制/模擬以及Encounter RTL-to-Signoff平臺。

2012-10-22 16:48:03 1286

1286 該14納米產品體系與芯片是ARM、Cadence與IBM之間在14納米及以上高級工藝節點上開發系統級芯片(SoC)多年努力的重要里程碑。使用FinFET技術以14納米標準設計的SoC能夠大幅降低功耗。 這

2012-11-16 14:35:55 1642

1642 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)近日宣布,GLOBALFOUNDRIES已攜手Cadence?,為其20和14納米制程提供模式分類數據

2013-05-13 10:20:02 1094

1094 為專注于解決先進節點設計的日益復雜性,全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS) 今天宣布,臺積電已與Cadence在Virtuoso定制和模擬設計平臺擴大合作以設計和驗證其尖端IP。

2013-07-10 13:07:23 1201

1201 全球電子創新設計Cadence公司與上海華力微電子,15日共同宣布了華力微電子基于Cadence Encounter數字技術交付55納米平臺的參考設計流程。華力微電子首次在其已建立55納米工藝上實現了從RTL到GDSII的完整流程。

2013-08-16 11:08:11 2474

2474 中芯國際新款40納米 Reference Flow5.1結合了最先進的Cadence CCOpt和GigaOpt工藝以及Tempus 時序簽收解決方案, 新款RTL-to-GDSII數字流程支持Cadence的分層低功耗流程和最新版本的通用功率格式(CPF).

2013-09-05 10:45:03 2485

2485 2016年3月22日,中國上海——楷登電子(美國 Cadence 公司,NASDAQ: CDNS)今日宣布,用于10納米 FinFET工藝的數字、定制/模擬和簽核工具通過臺積電(TSMC)V1.0設計參考手冊(DRM)及SPICE認證。

2016-03-22 13:54:54 1453

1453 FastSPICE? (AFS) 平臺。除此之外,Calibre 和 Analog FastSPICE 平臺已可應用在基于TSMC 7 納米 FinFET 工藝最新設計規則手冊 (DRM) 和 SPICE 模型的初期設計開發和 IP 設計。

2016-03-24 11:13:19 1110

1110 4月15日,中國上海—楷登電子(美國 Cadence 公司,NASDAQ: CDNS)今日宣布Cadence? Virtuoso? 版圖依賴效應(Layout-Dependent Effects

2016-04-15 10:09:07 2638

2638 “我們與 Cadence 密切合作開發參考流程,幫助我們的客戶加快其差異化的低功耗、高性能芯片的設計,”中芯國際設計服務中心資深副總裁湯天申博士表示,“Cadence創新的數字實現工具與中芯國際28納米工藝的緊密結合,能夠幫助設計團隊將28納米設計達到更低的功耗以及更快的量產化。”

2016-06-08 16:09:56 3225

3225 節點FinFET技術,7LPP和8LPP工藝技術不僅進一步優化了功耗、性能和面積特性,擴展能力也更為出色。目前,客戶已經可以應用下一代技術開始早期設計。

2017-06-02 16:04:34 1668

1668 中國上海,2017年6月12日 – 楷登電子(美國Cadence公司,NASDAQ: CDNS)今日發布全新Cadence? Virtuoso? System Design Platform

2017-06-13 14:26:28 3882

3882 賽靈思、Arm、Cadence和臺積公司今日宣布一項合作,將共同構建首款基于臺積7納米FinFET工藝的支持芯片間緩存一致性(CCIX)的加速器測試芯片,并計劃在2018年交付

2017-09-23 10:32:12 4604

4604 賽靈思、Arm、Cadence和臺積公司今日宣布計劃在 2018 年交付 7 納米 FinFET 工藝芯片。這一測試芯片旨在從硅芯片層面證明 CCIX 能夠支持多核高性能 Arm CPU 和 FPGA 加速器實現一致性互聯。

2017-09-25 11:20:20 7378

7378 7納米工藝將成為明年的重點制程工藝,但受成本太高的原因,據悉明年僅三星蘋果兩家手機繼續采用7納米處理器。高通沒有采用臺積電最新的7納米工藝,會繼續延用三星電子的10納米工藝。

2017-12-14 08:59:36 6647

6647 據國外媒體報道,芯片代工商 臺積電 的CEO魏哲家日前透露,他們的7納米工藝已投入生產,更先進的5納米工藝最快會在明年底投產。

2018-08-01 16:48:34 3903

3903 據國外媒體援引業內人士的觀點指出,由于10納米以下芯片的生產工作需要大量資本投入,大量芯片制造商紛紛基于成本考慮選擇將業務重點繼續放在現有14/12納米工藝上,同時減緩了自己對更先進納米工藝的投資腳步。

2018-09-09 09:35:33 4847

4847 解決方案。這次Credo的第三個硅驗證的7納米112G SerDes架構現允許系統級芯片(SoC)的研發來采用臺積公司先進的7納米工藝節點。

2018-10-30 11:11:12 5979

5979 IRIS為IC設計人員提供了一種在主流設計環境中運行復雜的3D EM分析的簡單方法。IRIS基于加速矩量法(MoM)的全波電磁求解器引擎已在多個先進工藝節點上驗證了其準確性。Virtuoso無縫集成

2018-11-20 14:22:14 4779

4779 目前來看,在資本與技術拉高進入門檻下,GlobalFoundries(GF)退場、代工并非本業的英特爾則放棄代工業務,7納米以下先進工藝代工戰場已成為臺積電、三星晶圓代工雙雄對戰競況。

2018-12-21 10:55:44 3504

3504 最近,三星以及臺積電在先進半導體制程打得相當火熱,彼此都想要在晶圓代工中搶得先機以爭取訂單,幾乎成了14納米與16納米之爭,然而14納米與16納米這兩個數字的究竟意義為何,指的又是哪個部位?而在縮小工藝后又將來帶來什么好處與難題?以下我們將就納米工藝做簡單的說明。

2019-04-29 10:35:44 10662

10662

即將到來的“N6”工藝節點將使用與“N7”節點相同的設計規則,使客戶更容易轉換到更新,更密集的節點。

2019-05-06 15:27:00 2691

2691 三星的3nm工藝節點采用的GAAFET晶體管是什么?

2019-05-17 15:38:54 12185

12185

5月29日,在今天的臺北國際電腦展上,聯發科對外發布全新5G移動平臺,該款多模 5G系統單芯片(SoC)采用7nm工藝制造。

2019-05-29 17:01:15 3730

3730 柏燕民表示,中興的5G芯片已經發展到了第三代產品,基于7納米工藝,相關產品將在下半發布

2019-06-28 10:27:40 3883

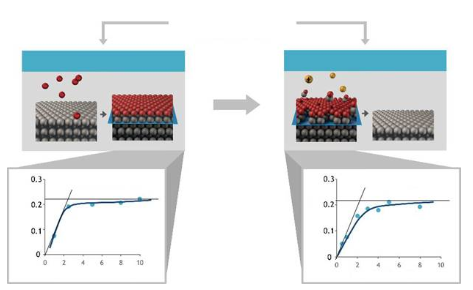

3883 集成電路設計自動化軟件領導企業新思(Synopsys)近日宣布,面向三星7LPP(7nm Low Power Plus)和更先進工藝的良率學習平臺設計取得最大突破,也為三星后續5nm、4nm、3nm工藝的量產和良品率奠定了堅實基礎。

2019-07-08 15:56:45 3656

3656 英特爾預計其制造工藝節點技術將保持2年一飛躍的節奏,從2019年的10納米工藝開始,到2021年轉向7納米EUV(極紫外光刻),然后在2023年采用5納米,2025年3納米,2027年2納米,最終到2029年的1.4納米。

2019-12-11 10:31:20 3933

3933 12月11日消息,據外媒報道,在今年的IEEE國際電子設備會議(IEDM)上,芯片巨頭英特爾發布了2019年到2029年未來十年制造工藝擴展路線圖,包括2029年推出1.4納米制造工藝。

2019-12-11 14:37:11 3912

3912 12月11日消息,據外媒報道,在今年的IEEE國際電子設備會議(IEDM)上,芯片巨頭英特爾發布了2019年到2029年未來十年制造工藝擴展路線圖,包括2029年推出1.4納米制造工藝。

2019-12-12 15:21:11 3237

3237 作為中國半導體行業最薄弱但也是最重要的環節,芯片工藝一直是國內的痛點,所以國內最大的晶圓代工廠中芯國際任重而道遠。此前中芯國際已經表態14nm工藝已經試產,今年就會迎來一輪爆發,年底的產能將達到目前的3-5倍,同時今年內還有可能試產更先進的7nm工藝。

2020-01-07 09:54:45 6543

6543 在摩爾定律邁向5納米之際,人們的目光多被幾家半導體公司間的先進工藝之爭所吸引。然而,邏輯芯片的制造工藝極其復雜多樣,5納米、7納米等標準工藝只是一部分,晶圓代工廠可以發展的制造工藝平臺還有很多,如

2020-06-10 14:35:25 2474

2474 作為中國大陸技術最先進、規模最大的晶圓代工企業,中芯國際的制程工藝發展一直備受關注。歷經20年,其制程工藝從0.18微米技術節點發展至如今的N+1工藝。

2020-10-20 16:50:10 8031

8031 12月9日,美國芯片巨頭高通已經悄然成為臺積電7納米半導體制造工藝節點的最大客戶,并已經向蘋果發運1.76億個5G調制解調器。

2020-12-10 14:10:16 1809

1809 性能、功耗和面積 (PPA) 目標受多個靜態指標影響,包括時鐘和數據路徑時序、版圖規劃以及特定電壓水平下的功耗。這些指標會進一步推動技術庫的表征,設計優化和簽核收斂。 先進工藝節點設計,尤其是高性能

2021-05-06 11:12:01 2951

2951 Cadence 數字和定制/模擬先進工藝節點解決方案支持 Cadence 智能系統設計(Intelligent System Design)戰略,旨在系統級芯片(SoC)上實現卓越設計,如需了解更多信息,請訪問:

2021-10-26 14:44:47 4148

4148 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence? 數字全流程獲得了 GlobalFoundries (GF) 12LP/12LP+ 工藝平臺認證,以推動移動和消費市場的航空航天、超大規模計算、人工智能、移動和消費電子應用的設計。

2022-05-24 16:33:23 2260

2260 就晶體管數量和復雜性而言,先進工藝節點的設計尺寸正在迅速增加。因此,Veloce Strato 仿真平臺可擴展到 150 億門。

2022-06-29 15:23:24 987

987 5納米芯片相比7納米芯片的工藝技術要求更高、更好更低、性能更好。芯片工藝中5nm和7nm的兩個數值,代表的是芯片晶體管導電溝道的長度。

2022-06-29 17:00:39 30825

30825 在芯片設計和制造中,納米表示的是芯片中晶體管與晶體管之間的距離,在體積相同大小的情況下,7納米工藝的芯片容納的晶體管的數量,幾乎是14納米工藝芯片的2倍。

2022-07-06 16:35:55 136833

136833 工藝認證,支持新的設計規則手冊(DRM)和 FINFLEX 技術。通過持續的合作,兩家公司還提供了相應的 N4P 和 N3E 工藝設計套件(PDKs),可加快移動、人工智能和超大規模計算先進節點

2022-10-27 11:01:37 2277

2277 中芯國際南方廠2019年實現了14nm工藝的量產,該生產線總投資90.59億美元,產能3.5萬片/月,代表作麒麟710A;但在2020年中芯國際被納入了實體清單,被卡在10nm(含)工藝節點。

2023-03-14 10:45:24 50489

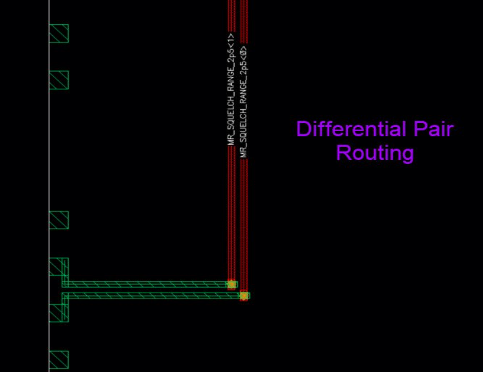

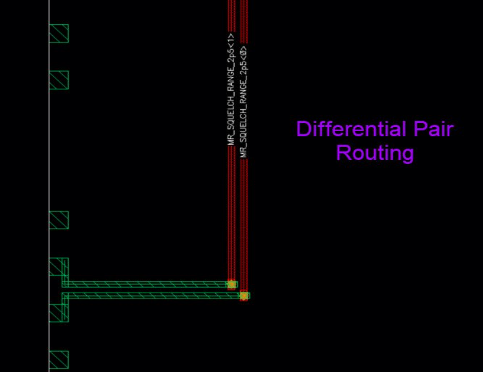

50489 交互式路由允許您在自動路由之前完成關鍵網絡,并在自動路由后完成未布線的不完整網絡。Virtuoso 交互式和輔助路由功能允許您在 Virtuoso 環境中以交互方式路由連接,以滿足關鍵的設計約束和規則。在所有工藝節點上啟用交互式和自動布線功能,包括最先進的工藝技術。

2023-04-20 10:58:23 4447

4447

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布推出基于 Cadence Virtuoso Design Platform 的節點到節點設計遷移流程,能兼容所有的臺積電先進節點

2023-05-06 15:02:15 1934

1934 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 數字和定制/模擬設計流程已通過 TSMC N3E 和 N2 先進工藝的設計規則手冊(DRM)認證。兩家公司還發布

2023-05-09 10:09:23 2046

2046 3nm 時代來臨了!Cadence 在 2023 年 TSMC 北美技術研討會期間發布了面向臺積電 3nm 工藝(N3E)的 112G 超長距離(112G-ELR)SerDes IP 展示,這是 Cadence 112G-ELR SerDes IP 系列產品的新成員。

2023-05-19 15:23:07 1735

1735

了新一代定制設計平臺 Cadence Virtuoso Studio ,該平臺采用全新的底層架構,以獨特的方法來管理設計流程,可將當今大型設計的設計同步吞吐量提升 3 倍,是面臨大型復雜項目和有短時間

2023-06-13 12:15:02 3455

3455

,2023 年 6 月 30 日——楷登電子(美國? Cadence ?公司,NASDAQ:CDNS)近日宣布,基于 AI 的 Cadence?Virtuoso?Studio 設計工具和解決方案已獲得 Samsung Foundry 認證。 雙方的共同客戶可以放心利用 Virtuoso Studio 和

2023-06-30 10:08:30 2222

2222 先進節點經過優化 中國上海, 2023 年 7 月 4 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,搭載最新生成式 AI 技術的 Cadence ?Virtuoso

2023-07-04 10:10:01 1516

1516 已經過 SF2 和 SF3 流程認證 ●? Cadence 數字全流程針對先進節點實現了最佳 PPA 結果 ● Cadence 定制/模擬工具,包括基于 AI 的 Virtuoso Studio,已

2023-07-05 10:10:01 1140

1140 已經過 SF2 和 SF3 流程認證 ●?Cadence 數字全流程針對先進節點實現了最佳 PPA 結果 ●Cadence 定制/模擬工具,包括基于 AI 的 Virtuoso Studio,已針對

2023-07-05 10:12:14 1322

1322 3nm 時代來臨了!Cadence 在 2023 年 TSMC 北美技術研討會期間發布了面向臺積電 3nm 工藝(N3E)的 112G 超長距離(112G-ELR)SerDes IP 展示,這是 Cadence 112G-ELR SerDes IP 系列產品的新成員。

2023-07-10 09:26:20 1241

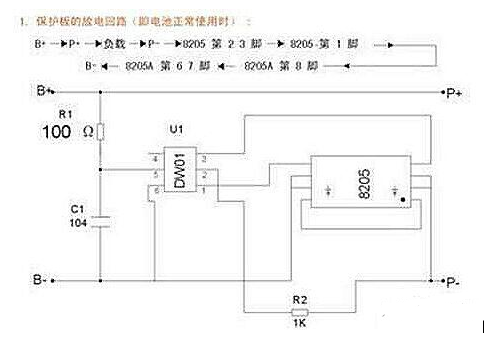

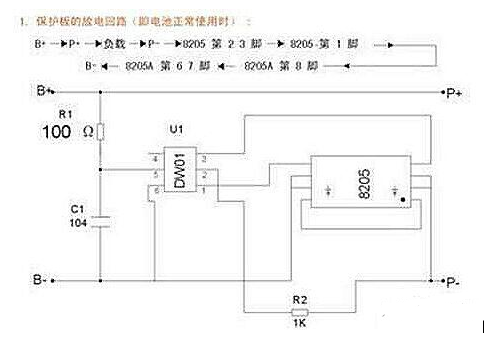

1241 電池保護IC(Integrated Circuit)的納米工藝并沒有固定的規定或標準。電池保護IC的制造工藝通常與集成電路制造工藝一樣,采用從較大的微米級工藝(如180nm、90nm、65nm等)逐漸進化到更先進的納米級工藝(如45nm、28nm、14nm等)。

2023-07-11 15:42:37 3464

3464

了新一代定制設計平臺 Cadence Virtuoso Studio ,該平臺采用全新的底層架構,以獨特的方法來管理設計流程,可將當今大型設計的設計同步吞吐量提升 3 倍,是面臨大型復雜項目和有短時間

2023-09-01 12:20:01 1452

1452

Cadence Virtuoso定制設計平臺的一套全面的集成電流(IC)設計系統,能夠在多個工藝節點上加速定制IC的精確芯片設計,其定制設計平臺為模擬、射頻及混合信號IC提供了極其方便、快捷而精確的設計方式。

2023-09-11 15:14:16 12455

12455

? //?? 中國上海,2023 年 9 月 27 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布擴展基于 Cadence ?Virtuoso ?Studio 的節點到節點設計遷移

2023-09-27 10:10:04 1634

1634 來源:IMEC 設計探路PDK降低了學術界和工業界接觸最先進半導體技術的門檻 在2024年IEEE國際固態電路會議 (ISSCC) 上,世界領先的納米電子和數字技術研究與創新中心imec推出了其

2024-02-22 18:24:00 1476

1476 如今,一顆芯片可以集成數十億個晶體管,晶體管排列越緊密,所需的工藝節點就越小,某些制造工藝已經達到 5 納米甚至更小的節點。

2024-04-11 15:02:16 1668

1668

近日,安森美(onsemi,納斯達克股票代號:ON)宣布推出Treo平臺,這是一個采用先進的65nm節點的BCD(Bipolar–CMOS-DMOS)工藝技術構建的模擬和混合信號平臺。該平臺為安森美

2024-11-12 11:03:21 1375

1375 本文介紹了7納米工藝面臨的各種挑戰與解決方案。 一、什么是7納米工藝? 在談論7納米工藝之前,我們先了解一下“納米”是什么意思。納米(nm)是一個長度單位,1納米等于10的負九次方米。對于半導體芯片

2024-12-17 11:32:21 2561

2561 當前全球半導體工藝水平已進入納米級突破階段,各大廠商在制程節點、材料創新、封裝技術和能效優化等方面展開激烈競爭。以下是目前最先進的半導體工藝水平的詳細介紹: 一、制程工藝突破 英特爾18A(約

2025-10-15 13:58:16 1420

1420

電子發燒友App

電子發燒友App

評論