集成電路設(shè)計自動化軟件領(lǐng)導(dǎo)企業(yè)新思(Synopsys)近日宣布,面向三星7LPP(7nm Low Power Plus)和更先進工藝的良率學(xué)習(xí)平臺設(shè)計取得最大突破,也為三星后續(xù)5nm、4nm、3nm工藝的量產(chǎn)和良品率奠定了堅實基礎(chǔ)。

量產(chǎn)探索平臺(Yield Explorer)是一種復(fù)雜的芯片量產(chǎn)良品率學(xué)習(xí)平臺,可用來分析芯片設(shè)計、晶圓廠生產(chǎn)、產(chǎn)品測試三大方面的數(shù)據(jù),以便幫助工程師找到缺點、改進良品率、提高產(chǎn)能。

現(xiàn)代芯片設(shè)計和生產(chǎn)是極為復(fù)雜的過程,往往涉及幾千個步驟,需要花費數(shù)月時間,而芯片的最終良品率取決于整體設(shè)計、性能和功耗需求等,因此要想提高芯片生產(chǎn)的成功率,需要對各種因素進行細(xì)致的分析。

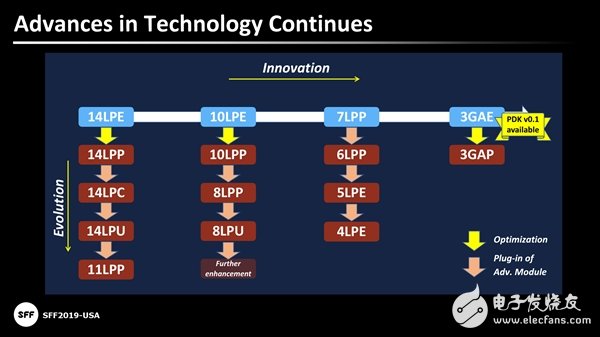

根據(jù)路線圖,三星工藝近期有14nm、10nm、7nm、3nm三個重要節(jié)點,其中14nm會演化出11nm,10nm會演化出8nm,7nm則會演化出6nm、5nm、4nm。

而每種工藝往往又會根據(jù)性能、功耗的不同而分為多個版本,比如14nm分成了14LPE、14LPP、14LPC、14LPU,3nm則分成3GAE、3GAP,預(yù)計會采用全新的材料。

目前,三星已經(jīng)完成5nm工藝的設(shè)計工作,正在加速推進投入量產(chǎn),4nm則將在今年下半年完成開發(fā),新思的新平臺將在其中發(fā)揮巨大作用。

-

芯片

+關(guān)注

關(guān)注

463文章

54281瀏覽量

468319 -

三星電子

+關(guān)注

關(guān)注

34文章

15896瀏覽量

183191 -

新思

+關(guān)注

關(guān)注

0文章

21瀏覽量

30115

發(fā)布評論請先 登錄

濕法清洗和干法清洗,哪種工藝更適合先進制程的硅片

三星2nm良率提升至50%,2027年前實現(xiàn)晶圓代工業(yè)務(wù)盈利可期

Flip Chip水溶性助焊膏:高良率 · 低空洞 · 易清洗 · 適用于先進封裝

革新半導(dǎo)體清洗工藝:RCA濕法設(shè)備助力高良率芯片制造

晶圓邊緣曝光(WEE)關(guān)鍵技術(shù)突破:工藝難點與 ALE 光源解決方案

在電子制造的高精度領(lǐng)域中,芯片引腳的處理工藝

目前最先進的半導(dǎo)體工藝水平介紹

華大九天Vision平臺重塑晶圓制造良率優(yōu)化新標(biāo)桿

國內(nèi)最大!長飛先進武漢基地投產(chǎn),明治傳感助力半導(dǎo)體智造升級

新思科技與三星深化合作加速AI和Multi-Die設(shè)計

三星Galaxy Z Fold7搭載高通驍龍8至尊版移動平臺

三星電子全力推進2納米制程,力爭在2025年內(nèi)實現(xiàn)良率70%

革新焊接工藝,MiniLED焊錫膏開啟精密制造超高良率時代

三星在4nm邏輯芯片上實現(xiàn)40%以上的測試良率

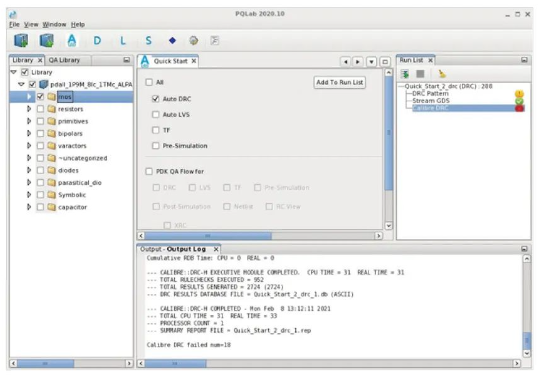

概倫電子先進PDK驗證平臺PQLab介紹

新思宣布先進工藝良率學(xué)習(xí)平臺設(shè)計取得最大突破 為三星后續(xù)先進工藝奠定基礎(chǔ)

新思宣布先進工藝良率學(xué)習(xí)平臺設(shè)計取得最大突破 為三星后續(xù)先進工藝奠定基礎(chǔ)

評論