本文介紹一種在嵌入式數字信號處理器(DSP)OMAP5912上使用簡單的數字電源實現系統低功耗設計的方法。

2011-11-30 00:50:00 1963

1963

Cadence宣布業內首個DDR4 Design IP解決方案在28納米級芯片上得到驗證

2012-09-10 09:53:24 1949

1949 賽靈思的20納米產品以備受市場肯定的28納米制程突破性技術為基礎,提供超越一個技術世代的系統效能、功耗和可編程系統整合度,繼續超越下一代!

2012-12-03 09:48:01 1204

1204 Cadence設計系統公司(Cadence Design Systems, Inc.)(納斯達克代碼:CDNS)今日宣布與TSMC簽訂了一項長期合作協議,共同開發16納米FinFET技術,以其適用于

2013-04-09 11:00:05 1123

1123 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS),近日推出新版本Incisive Enterprise Simulator,該版本將復雜SoC的低功耗驗證效率提高了30

2013-05-14 10:31:40 2667

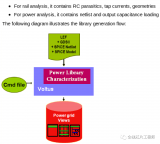

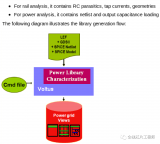

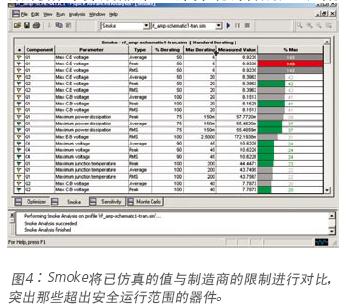

2667 Cadence功耗分析首先需生成power grid library

2023-09-06 09:47:50 2992

2992

全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS)今天宣布,全球領先的晶圓廠之一中國中芯國際[0.40 2.56%]集成電路制造有限公司(SMIC)推出一款采用Cadence Encounter數字技術和SMIC

2012-04-11 09:44:30 1189

1189 Cadence設計系統公司發布了Cadence Allegro系統互連設計平臺針對印刷電路板(PCB)設計進行的全新產品和技術增強。改進后的平臺為約束驅動設計提供了重要的新功能,向IC、封裝和板

2018-11-23 17:02:55

。” Cadence推出的RFSiP套件為無線通信應用的RFSiPs設計提供了自動化和加速設計流程的最新產品和技術。它同時提供了基于802.11b/g無線局域網設計的成熟的SiP實施方法,能夠低風險地實現

2008-06-27 10:24:12

Cadence仿真流程Cadence仿真流程[/hide][此貼子已經被作者于2009-8-16 13:47:51編輯過]

2009-08-16 13:47:03

授權使用正確的低功耗分析和最優化引擎,這些功能要求集成在整個設計流程中。此外,在65納米芯片設計中,約有50%的設計工作是混合信號設計。傳統的模擬設計流程與數字工作處于完全隔離的狀態,如何把模擬和數字

2019-05-20 05:00:10

數據透傳是選擇低功耗WiFi模塊還是低功耗藍牙模塊好?

2021-01-04 06:55:35

物聯網的興起帶動越來越多的公司選用無線互聯產品,在無線互聯中低功耗藍牙(BLE)是不可缺少的用來支持相互連接的產品之一,因為低功耗藍牙無需網關就可以直接與智能終端通信,有比較好的人機交互體驗,特別是藍牙MESH發布,可以讓更多結點在同一個網絡互通。 許多工程師不清楚如何選型;有什么技巧嗎?

2021-03-06 08:22:49

本帖最后由 eehome 于 2013-1-5 10:02 編輯

數字語音解碼器的低功耗設計方案

2012-08-20 12:50:40

Port Pins,它說“有時在數字輸入時將數字輸入配置為模擬輸入是適當的和可能的必須進入低功耗狀態。“我不太理解這一點,關于數字輸入必須如何進入低功耗狀態。”請你闡述一下這一點好嗎?如果有一些例子的話會很有幫助的。謝謝!

2020-04-30 09:25:33

,通過發行所謂的“虛擬資產”、“數字資產”、“虛擬貨幣”等方式吸收資金,已經侵害到公眾的合法權益了。五部委聯合發布風險提示,讓無數人拍手叫好!有網友甚至吐出心聲:確實該整頓了,這些打著“給大眾迅速賺大錢

2018-08-29 13:36:47

今天更新一篇數字IC低功耗設計方法總結,內容參考的是郭煒老師的書:《SoC設計方法與實現(第3版)》,希望能給大家帶來幫助~

2021-07-29 06:38:58

芯片設計解決方案供應公司微捷碼(Magma)設計自動化有限公司近日宣布,已和專為消費性應用提供超低功耗65納米FPGA(現場可編程門陣列)技術的先驅者SiliconBlue科技公司正式簽定技術合作

2019-07-26 07:29:40

現在電子產品一般都有要求低功耗,不同的MCU,進入低功耗的處理流程可能不一樣,但是大致的流程還是一樣。現對MCU進入低功耗的處理流程大致如下:(1)關閉MCU之外的外設電源,例如:RS485、CAN

2021-11-01 08:10:03

一半,而性能提高兩倍。通過選擇一個高性能低功耗的工藝技術,一個覆蓋所有產品系列的、統一的、可擴展的架構,以及創新的工具,賽靈思將最大限度地發揮 28 納米技術的價值, 為客戶提供具備 ASIC 級功能

2019-08-09 07:27:00

為什么需要低功耗設計?如何實現數字IC低功耗的設計?

2021-11-01 06:37:46

如何配置和使用Lierda NB861 MB261 MB961模組的低功耗模式,并如何通過相關低功耗配置AT指令操作流程來指導用戶完成低功耗應用的開發呢?

2024-06-04 06:46:40

單位。中科院計算技術研究所:負責設計驗證及測試綜合 SIG,與中科鑒芯(北京)科技有限責任公司聯合發布故障仿真器 v1.0;中科院微電子研究所:負責器件模型與參數提取 SIG、工藝模型及 PDK SIG

2022-06-24 15:17:14

2月19日,在新華社新媒體中心與搜狗公司戰略合作簽約儀式上,搜狗公司與新華社新媒體中心聯合發布了全球首個站立式AI合成主播,新的AI合成主播將從過去的“坐著播新聞”升級成結合肢體動作的“站立

2019-02-25 09:28:26

Cadence 仿真流程:第一章 在Allegro 中準備好進行SI 仿真的PCB 板圖1)在Cadence 中進行SI 分析可以通過幾種方

2008-07-12 08:56:05 0

0

低功耗數字VLSI設計:概覽:

2009-07-25 16:44:42 0

0 cadence 視頻教程 (第28課):adence SPB 15.7 視頻教程,手把手教你學習cadence軟件使用方法。本套視頻教程是于博士信號完整性研究網于爭博士主講。從一個工程師的角度出發講解軟件的操

2009-09-16 19:02:12 0

0 Tensilica 日前宣布與Cadence 合作,根據Tensilica 的330HiFi 音頻處理器和388VDO 視頻引擎,為其多媒體子系統建立一個通用功耗格式(CPF)的低功耗參考設計流程。Cadence 和Tensilica公司的工

2009-12-04 13:54:39 32

32

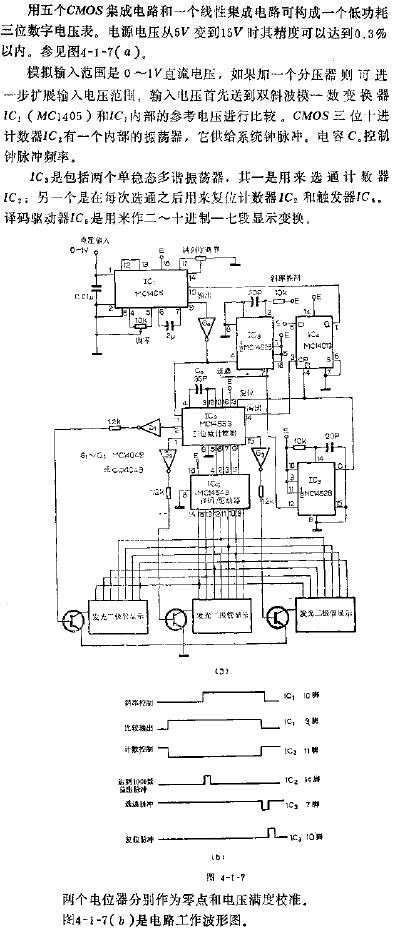

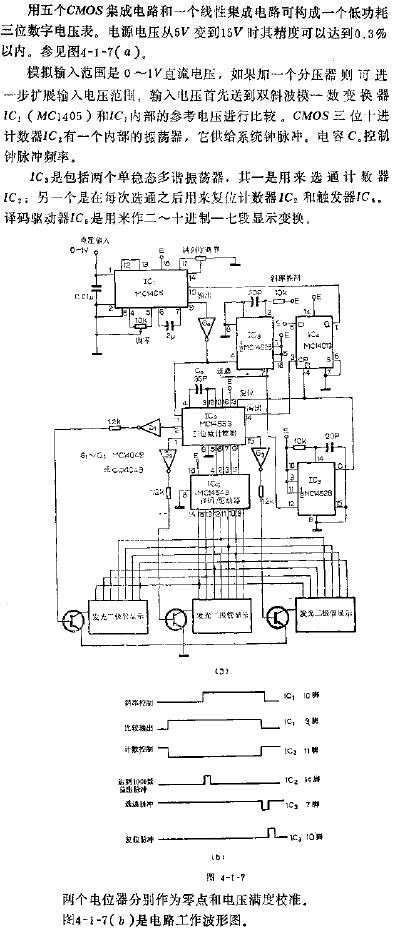

低功耗數字電壓表

2009-04-10 10:15:58 813

813

中芯國際(SMIC)和Cadence 共同推出用于65納米的低功耗解決方案Reference Flow 4.0

完全集成的能效型流程令快速、輕松地設計低功耗尖端器件成為可能

2009-10-31 07:48:01 1606

1606 高速低功耗數字光電耦合器(Avago)

Avago Technologies(安華高科技)宣布,推出二款面向油電混合動力車(HEV, Hybrid Electronic Vehicles)應用所設計的車用級高速低功耗數字CMOS光

2009-11-02 09:05:26 877

877 中芯國際(SMIC)和Cadence共同推出用于65納米的低功耗解決方案Reference Flow 4.0

全球電子設計創新領先企業Cadence設計系統公司今天宣布推出一款全面的低功耗設計流程,面向

2009-11-04 17:05:17 935

935 SIG發布新版低功耗藍牙規范

藍牙技術聯盟(Bluetooth Special Interest Group,SIG)日前推出采用低功耗版本藍牙核心規范4.0版本的升級版藍牙低功耗無線技術,將為具備低成本、

2009-12-30 08:52:37 1517

1517 統一工藝和架構,賽靈思28納米FPGA成就高性能和低功耗的完美融合

賽靈思公司(Xilinx)近日宣布,為推進可編程勢在必行之必然趨勢,正對系統工程師在全球發布賽靈思

2010-03-02 08:48:51 962

962 根據貫穿整個IC實現流程的集成化低功耗設計技術策略

降低功耗是現代芯片設計最具挑戰性需求之一。采用單點工具流程時,往往只有到了設計流程后期階段才會去考慮降

2010-04-21 10:54:28 1117

1117

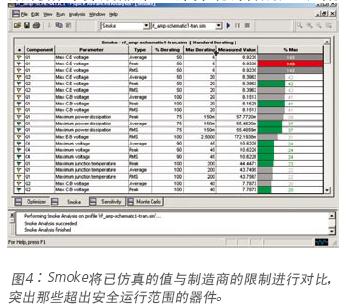

Cadence PCB設計仿真技術

Cadence PCB設計仿真技術提供了一個全功能的模擬仿真器,并支持數字元件幫助解決幾乎所有的設計挑戰,從高頻系統到低功耗I

2010-04-29 08:41:58 4819

4819

ADAU1761低功耗數字音頻處理CODEC方案 ADI 公司的ADAU1761 是低功耗集成了數字音頻處理的立體聲CODEC,支持立體聲48kHz 錄音,1.8V 播放時的功耗為14mW.立體聲

2011-01-24 16:03:06 170

170 微捷碼(Magma®)設計自動化有限公司日前宣布,一款經過驗證的支持Common Platform™聯盟32/28納米低功耗工藝技術的層次化RTL-to-GDSII參考流程正式面市。

2011-01-26 09:44:09 1299

1299 本文基于IEEEl801標準Uni-fied Power Format(UPF),采用Synopsys和Mentor Graphics的EDA工具實現了包括可測性設計在內的“從RTL到GDSII”的完整低功耗流程設計。本論文第1部分描述了低功耗技術和術語

2011-03-11 11:33:55 2382

2382

Synopsys和華虹NEC共同合作的結晶,它將Synopsys Eclypse? 低功耗解決方案加入到之前為設計師所提供的各種參考流程之中。

2011-04-25 10:36:57 1107

1107 即將上市的這種新流程支持Cadence的硅實現方法,專注于獨一無二且普遍深入的設計意圖、提取與從RTL到GDSII,然后到封裝。硅實現是EDA360構想的一個關鍵組成部分。

2011-06-28 09:44:23 678

678 三星電子有限公司使用Cadence統一數字流程,從RTL到GDSII,成功實現了20納米測試芯片的流片

2011-07-27 08:47:49 1339

1339 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS),宣布Giantec Semiconductor Corp.已采用Cadence? Virtuoso?統一定制/模擬(IC6.1)以及Encounter?統一數字流程生產其混合信號芯片。

2011-09-27 11:06:26 1765

1765 全球電子設計創新領先企業Cadence設計系統公司日前宣布推出最新版Cadence Encounter RTL-to-GDSII流程.

2012-03-10 09:44:06 981

981 Cadence 設計系統公司日前宣布,汽車零部件生產商Denso公司在改用了Cadence定制/模擬與數字流程之后,在低功耗混合信號IC設計方面實現了質量與效率的大幅提升。將Cadence Encounter RTL-to-G

2012-09-04 09:31:59 1157

1157 全球電子設計創新領先企業Cadence設計系統公司日前宣布TSMC已選擇Cadence解決方案作為其20納米的設計架構。Cadence解決方案包括Virtuoso定制/模擬以及Encounter RTL-to-Signoff平臺。

2012-10-22 16:48:03 1286

1286 該14納米產品體系與芯片是ARM、Cadence與IBM之間在14納米及以上高級工藝節點上開發系統級芯片(SoC)多年努力的重要里程碑。使用FinFET技術以14納米標準設計的SoC能夠大幅降低功耗。 這

2012-11-16 14:35:55 1642

1642 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)近日宣布,GLOBALFOUNDRIES已攜手Cadence?,為其20和14納米制程提供模式分類數據

2013-05-13 10:20:02 1094

1094 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)今天宣布,歷經廣泛的基準測試后,半導體制造商聯華電子(NYSE:UMC;TWSE:2303)(UMC)已采用Cadence? “設計內”和“簽收”可制造性設計(DFM)流程對28納米設計進行物理簽收和電學變量優化。

2013-07-18 12:02:09 1266

1266 日前,聯華電子與SuVolta公司宣布聯合開發28納米工藝技術,該工藝將SuVolta的SuVolta的Deeply Depleted Channel晶體管技術集成到聯華電子的28納米High-K/Metal Gate高效能移動工藝。

2013-07-25 10:10:52 1458

1458 全球電子創新設計Cadence公司與上海華力微電子,15日共同宣布了華力微電子基于Cadence Encounter數字技術交付55納米平臺的參考設計流程。華力微電子首次在其已建立55納米工藝上實現了從RTL到GDSII的完整流程。

2013-08-16 11:08:11 2474

2474 中芯國際新款40納米 Reference Flow5.1結合了最先進的Cadence CCOpt和GigaOpt工藝以及Tempus 時序簽收解決方案, 新款RTL-to-GDSII數字流程支持Cadence的分層低功耗流程和最新版本的通用功率格式(CPF).

2013-09-05 10:45:03 2485

2485 ? 數字工具流程,應用于其新款SMIC Reference Flow 5.1,一款為低功耗設計的完整的RTL-GDSII 數字流程。Cadence流程結合了先進功能,以幫助客戶為40納米芯片設計提高功率、性能和面積。

2013-09-05 16:50:41 1083

1083 9月24日——全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS)今天宣布,Silicon Labs采用完整的Cadence? 混合信號低功耗設計流程,使其最新款節能型

2013-09-25 09:59:51 1221

1221 美國加州圣何塞,2014年9月30日 ─ 全球知名的電子設計創新領導者Cadence設計系統公司(NASDAQ: CDNS)今日宣布其豐富的IP組合與數字和定制/模擬設計工具可支持臺積電全新的超低功耗(ULP)技術平臺。

2014-10-08 19:24:35 1300

1300 詳細介紹Cadence的仿真流程

有需要的朋友下來看看

2015-12-08 14:49:11 0

0 , LDE) Analyzer 分析方案通過聯華電子認證,支援其28納米HPCU(High Performance Compact,高效能精簡型)制程技術。

2016-04-15 10:09:07 2638

2638 基于CCopt引擎的SMIC40nm低功耗工藝CortexA9的時鐘樹實現,該文基于 SMIC 40nm 低功耗工藝的 ARM Cortex A9 物理設計的實際情況,詳細闡述了如何使用 cadence 最新的時鐘同步優化技術,又稱為 CCopt 技術來實現統一的時鐘樹綜合和物理優化。

2017-09-28 09:08:51 7

7 臺積電業務開發副總經理金平中指出,臺積電的超低功耗平臺包括55納米超低功耗技術、40納米超低功耗技術、22納米超低功耗/超低漏電技術等,都已經被各種穿戴式產品和物聯網應用采用,同時,臺積電也把超低功耗

2017-12-11 15:03:29 2148

2148 CSDN與易觀聯合發布《2017-2018中國人工智能產業路線圖》

2018-03-22 14:29:32 5362

5362 浪潮與科大訊飛IPF2018聯合發布超強AI系統AI Booster 4月26日,在2018浪潮云數據中心合作伙伴大會(IPF2018)上,浪潮與科大訊飛聯合發布了面向于語音識別、翻譯等AI

2018-05-06 05:03:00 5630

5630 雙方聯合推出基于華潤上華110納米嵌入式閃存技術平臺的低功耗物聯網完整解決方案。

2018-08-15 08:52:50 4595

4595 近日,華虹集團旗下中國領先的12英寸晶圓代工企業上海華力與全球IC設計領導廠商---聯發科技股份有限公司(以下簡稱“聯發科技”)共同宣布,在兩家公司的互相信任及持續努力下,近日雙方合作成果之一---基于上海華力28納米低功耗工藝平臺的一顆無線通訊數據處理芯片成功進入量產階段。

2018-12-12 15:15:01 2733

2733 12月11日,華虹集團旗下中國領先的12英寸晶圓代工企業上海華力與全球IC設計領導廠商---聯發科技股份有限公司(以下簡稱“聯發科技”)共同宣布,在兩家公司的互相信任及持續努力下,近日雙方合作成果之一---基于上海華力28納米低功耗工藝平臺的一顆無線通訊數據處理芯片成功進入量產階段。

2018-12-14 15:47:30 3803

3803 華虹集團旗下中國領先的12英寸晶圓代工企業上海華力與全球IC設計領導廠商---聯發科技股份有限公司(以下簡稱“聯發科技”)共同宣布,在兩家公司的互相信任及持續努力下,近日雙方合作成果之一---基于上海華力28納米低功耗工藝平臺的一顆無線通訊數據處理芯片成功進入量產階段。

2019-01-01 15:13:00 4439

4439 華虹集團旗下上海華力與聯發科技股份有限公司共同宣布,在兩家公司的互相信任及持續努力下,近日雙方合作成果之一——基于上海華力28納米低功耗工藝平臺的一顆無線通訊數據處理芯片成功進入量產階段。

2019-01-07 14:15:45 3939

3939 中國移動、中國電信、中國聯通三家運營商聯合發布了《開放參考設計理念、進展及未來演進策略》白皮書

2019-06-27 17:14:11 4731

4731 采用極紫外(EUV)光刻技術的Cadence 數字全流程解決方案已通過Samsung Foundry 5nm早期低功耗版(5LPE)工藝認證。

2019-07-11 16:36:47 4272

4272 2020年9月28日] 2020北京國際汽車展覽會期間,上海海思與ADAYO華陽聯合發布AVM(Around View Monitor)智能環視方案。在行車和泊車時,通過全天候智慧視覺輔助,無死角監控,有效檢測障礙物并及時主動預警,消除駕駛員視野盲區,提升駕乘安全性。

2020-10-10 11:37:44 3905

3905 就在普京與拜登舉行會晤之際中俄聯合發布國際月球科研站路線圖;而且今天是神舟載人飛船發射成功的大好日子,我國空間站的建設加速推進正大邁步的走向世界前列。 中俄聯合發布國際月球科研站路線圖的時間是在全球

2021-06-17 12:04:40 12185

12185 01近日,致力于提供物聯網系統和智能產品解決方案的國家高新技術企業利爾達與ST意法半導體聯合發布低功耗藍牙模塊新品,該模塊采用意法半導體的STM32WB55* Bluetooth? LE (BLE

2021-08-31 11:17:47 2294

2294

現在電子產品一般都有要求低功耗,不同的MCU,進入低功耗的處理流程可能不一樣,但是大致的流程還是一樣。現對MCU進入低功耗的處理流程大致如下:(1)關閉MCU之外的外設電源,例如:RS485、CAN

2021-10-25 11:36:02 18

18 展銳賦能螞蟻鏈和廣和通聯合發布螞蟻鏈首批無線通信可信上鏈模組。

2021-11-19 20:29:52 1925

1925 近日,全球能源管理和自動化領域的數字化轉型專家施耐德電氣攜手CNBC Catalyst,聯合發布了名為《開啟可持續未來:數字解決方案成為可持續轉型關鍵》的報告(以下簡稱報告)。

2022-03-21 17:09:08 2180

2180 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence? 數字全流程獲得了 GlobalFoundries (GF) 12LP/12LP+ 工藝平臺認證,以推動移動和消費市場的航空航天、超大規模計算、人工智能、移動和消費電子應用的設計。

2022-05-24 16:33:23 2260

2260 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,其數字和定制 / 模擬設計流程已獲得 TSMC N3E 和 N4P 工藝認證,支持最新的設計規則手冊(DRM)。

2022-06-17 17:33:05 6035

6035 8月28日,由華為云、軟通動力信息技術(集團)股份有限公司(下稱“軟通動力”)等多家合作伙伴聯合發起的首屆828 B2B企業節正式啟動。作為此次盛事的聯合發起方,軟通動力出席啟動儀式并將全程參與到

2022-08-30 11:25:47 1438

1438 會上,云天勵飛與華為聯合發布基于昇騰AI的“AICE賦能行業解決方案”,以AI賦能城市千行百業,共筑產業生態,共創數智未來。

2022-09-05 11:03:41 1084

1084 電子發燒友網站提供《低功耗數字溫度計參考設計.zip》資料免費下載

2022-09-06 10:44:37 2

2 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 數字和定制/模擬設計流程已通過 TSMC N3E 和 N2 先進工藝的設計規則手冊(DRM)認證。兩家公司還發布

2023-05-09 10:09:23 2046

2046 中芯國際是中國大陸最大的半導體制造企業之一,主要業務是為其他半導體公司生產晶片。暫時中斷28納米芯片的生產擴大,將致力于提高12納米節點的生產能力。smic的決定是出于經濟上的原因。

2023-06-01 10:50:21 2239

2239 已經過 SF2 和 SF3 流程認證 ●? Cadence 數字全流程針對先進節點實現了最佳 PPA 結果 ● Cadence 定制/模擬工具,包括基于 AI 的 Virtuoso Studio,已

2023-07-05 10:10:01 1140

1140 已經過 SF2 和 SF3 流程認證 ●?Cadence 數字全流程針對先進節點實現了最佳 PPA 結果 ●Cadence 定制/模擬工具,包括基于 AI 的 Virtuoso Studio,已針對

2023-07-05 10:12:14 1322

1322 的 Cadence 流程,以十足把握交付各類 HPC 及消費電子應用 中國上海,2023 年 7 月 14 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布其數字和定制/模擬

2023-07-14 12:50:02 1450

1450

9月20日-22日,以“加速行業智能化”為主題的華為全聯接大會2023在上海召開。作為本屆大會唯一最高級別(鉆石級)的合作伙伴,軟通動力受邀參會,并出席行業輔助運營聯合發布儀式, 與華為及伙伴聯合發布

2023-09-24 21:55:01 1452

1452

內容提要 Cadence 數字全流程涵蓋關鍵的新技術,包括一款高精度且支持大規模擴展的寄生參數 3D 場求解器 Cadence Cerebrus 由 AI 驅動,支持 N2 制程,可大幅提高客戶

2023-10-10 16:05:04 1331

1331 內容提要 1 通過利用 Cadence AI 驅動云端數字全流程,Imagination 成功將其最新 5nm 節點的漏電功耗降低 20%,將總功耗降低 6%,同時改善了面積和性能 2

2023-10-18 15:50:01 818

818 “基于人工智能的cadence cerebrus和更廣泛的cadence數字進程是為復雜的下一代設計而設計的,例如5納米低功耗gpu的imagination。”

2023-10-20 10:04:07 1452

1452 清華、阿里安全、Real_AI聯合發布最新AI安全評估平臺

2023-01-13 09:07:31 1

1 Cadence近日宣布,其數字和定制/模擬流程在Intel的18A工藝技術上成功通過認證。這一里程碑式的成就意味著Cadence的設計IP將全面支持Intel的代工廠在這一關鍵節點上的工作,并提

2024-02-27 14:02:18 1331

1331 在2024年3月30日舉辦的2024國際星閃聯盟產業峰會上,國際星閃無線短距通信聯盟(簡稱“星閃聯盟”)與智慧車聯產業生態聯盟(簡稱“ICCE聯盟”)聯合發布了星閃數字車鑰匙標準。

2024-04-03 10:21:28 2919

2919

在2024年4月25日開幕的北京國際汽車展上,芯馳科技與HMI開發軟件提供商Qt Group聯合發布并展示了全新的智能座艙解決方案

2024-04-29 14:23:43 2415

2415

在數字中國建設峰會數字經濟論壇上,華為與國家發展改革委員會創新驅動發展中心(數字經濟研究發展中心)聯合發布《企業數字化轉型投入產出關系研究報告——數字化轉型助力高質量發展》(以下簡稱《報告》)。

2024-05-27 10:11:28 1096

1096

近日,以“數據賦能監管 守衛基金安全”為主題的聯合解決方案發布會在蘇州舉行,中軟國際有限公司(以下簡稱“中軟國際”)與華為技術有限公司(以下簡稱“華為”)聯合發布院端醫保風控一體機解決方案,實現醫保基金在院端的事前、事中、事后的全流程管控,全面助力醫院醫保基金管理質效提升。

2024-07-29 16:02:36 1842

1842

在第十一屆中國國際大數據產業博覽會“數字政府”交流活動上,國家數據發展研究院攜手華為技術有限公司(以下簡稱“華為”)聯合發布《AI CITY城市智能體前瞻研究報告》,旨在探索人工智能新時代下的AI CITY智能體應用和架構,為城市全域數字化轉型建設提供前瞻指引,為城市智慧化演進注入創新活力。

2025-09-01 10:37:01 1119

1119

電子發燒友App

電子發燒友App

評論