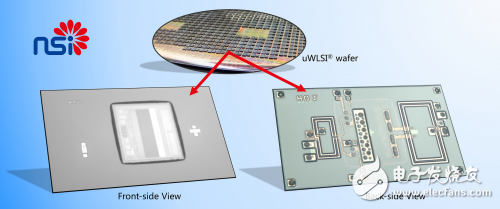

扇出型晶圓級封裝(FOWLP)的概念最早由德國英飛凌提出,自2016 年以來,業界一直致力于FOWLP 技術的發展。

2026-01-04 14:40:30 175

175

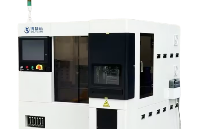

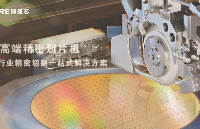

博捷芯劃片機針對射頻芯片制造中高精度切割的需求,提供了專業的解決方案,尤其在處理射頻芯片常用的化合物半導體等特殊材料方面表現突出。劃片機解決方案的核心優勢:切割精度與控制實現微米級定位精度,崩邊尺寸

2025-12-03 16:37:39 259

259

晶圓制造是現代半導體產業的核心環節,其工藝過程中對靜電控制、微電流檢測及高精度參數測量有著嚴苛要求。Keithley靜電計6514憑借超高靈敏度、低噪聲特性及多功能接口,在晶圓級測量中發揮著關鍵作用

2025-11-13 12:01:06 169

169

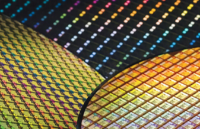

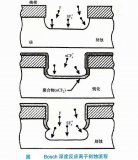

在超高純度晶圓制造過程中,盡管晶圓本身需達到11個9(99.999999999%)以上的純度標準以維持基礎半導體特性,但為實現集成電路的功能化構建,必須通過摻雜工藝在硅襯底表面局部引入特定雜質。

2025-10-29 14:21:31 620

620

在晶圓級封裝(WLP)中,Bump 凸點是芯片與基板互連的關鍵,主流實現方式有電鍍法、焊料印刷法、蒸發 / 濺射法、球放置法四類,差異顯著。選型需結合凸點密度、成本預算與應用特性,平衡性能與經濟性。

2025-10-23 14:49:14 1703

1703

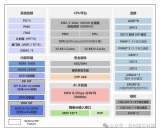

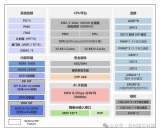

微電子技術的演進始終圍繞微型化、高效性、集成度與低成本四大核心驅動力展開,封裝技術亦隨之從傳統TSOP、CSP、WLP逐步邁向系統級集成的PoP、SiP及3D IC方向,最終目標是在最小面積內實現系統功能的最大化。

2025-10-21 17:38:28 1749

1749

在功率半導體封裝領域,晶圓級芯片規模封裝技術正引領著分立功率器件向更高集成度、更低損耗及更優熱性能方向演進。

2025-10-21 17:24:13 3873

3873

在當今數字化時代,顯示屏無處不在。然而,隨著設備小型化、高性能化的需求不斷增加,如何在有限的空間內實現更強大的顯示功能,成為了一個亟待解決的問題。力芯微LCD驅動IC:高集成度“芯”優勢讓顯示更簡單

2025-10-15 16:08:59 405

405

一、引言

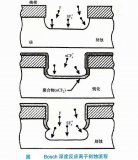

隨著半導體技術向小型化、高性能化發展,3D 集成封裝技術憑借其能有效提高芯片集成度、縮短信號傳輸距離等優勢,成為行業發展的重要方向 。玻璃晶圓因其良好的光學透明性、化學穩定性及機械強度

2025-10-14 15:24:56 316

316

恭喜昂瑞微二反掛網,這是射頻前端行業的重大事件!筆者曾有幸與昂瑞微團隊有過接觸與交流,今天也來說說對昂瑞微和射頻前端這個賽道的認識。 ? ? 射頻前端在通信技術領域中扮演著至關重要的角色,其既是實現

2025-10-13 15:49:49 1455

1455 晶圓級封裝(WLP)與多芯片組件(MCM)作為先進封裝的“雙引擎”,前者在晶圓未切割時即完成再布線與凸點制作,以“封裝即制造”實現芯片級尺寸、70 μm以下超細間距與電熱性能躍升;后者把多顆已驗證

2025-10-13 10:36:41 2088

2088

。 在射頻前端國產替代的浪潮中,不少企業憑借分立器件切入市場,實現了初步的規模擴張。然而,真正的競爭高地始終在于中高端模組市場——這里技術壁壘高、附加值大,也是國際廠商長期壟斷的領域。 昂瑞微則選擇了一條更難走

2025-10-12 15:03:08 427

427 、物聯網、衛星通信等關鍵領域實現從“跟跑”到“并跑”乃至“領跑”的跨越,為國產半導體突圍提供了可復制的創新范本。 技術突破:5G高集成度模組打破國際壟斷 在5G時代,射頻前端芯片是智能手機等移動終端的核心組件,其性能直接決定了通信

2025-10-11 09:49:36 874

874 度射頻前端模組領域實現關鍵技術突破,成為國內少數打破國際廠商壟斷格局的企業之一。此次IPO,昂瑞微擬公開發行不超過2,488.29萬股,募集資金約20.67億元,主要用于5G射頻前端芯片及模組的研發與產業化、射頻SoC芯片研發等核心項目。 核心看點一:

2025-10-09 18:22:50 4011

4011 正加速資本化進程。其中,深耕射頻前端芯片領域的昂瑞微備受市場關注。作為國內少數突破5G高端模組技術并實現大規模量產的廠商,昂瑞微的IPO進程標志著國產射頻前端行業進入新一輪價值重估周期。 一、 技術底蘊:從分立器件到高端模組的十年

2025-10-03 19:51:02 6011

6011 2025年3月28日,北京昂瑞微電子技術股份有限公司(以下簡稱“昂瑞微”)科創板IPO申請獲上交所受理。作為國家級專精特新重點“小巨人”企業,昂瑞微在射頻前端芯片領域取得了突破性進展,其5G高集成

2025-09-29 16:13:38 2131

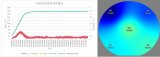

2131 WD4000晶圓BOW值彎曲度測量系統兼容不同材質不同粗糙度、可測量大翹曲wafer、測量晶圓雙面數據更準確。它通過非接觸測量,將晶圓的三維形貌進行重建,強大的測量分析軟件穩定計算晶圓厚度,TTV

2025-09-18 14:03:57

近日,廣立微自主研發的首臺專為碳化硅(SiC)和氮化鎵(GaN)功率器件設計的晶圓級老化測試系統——WLBI B5260M正式出廠。該設備的成功推出,將為產業鏈提供了高效、精準的晶圓級可靠性篩選解決方案,助推化合物半導體產業的成熟與發展。

2025-09-17 11:51:44 740

740

WD4000晶圓三維形貌膜厚測量系統通過非接觸測量,將晶圓的三維形貌進行重建,強大的測量分析軟件穩定計算晶圓厚度,TTV,BOW、WARP、在高效測量測同時有效防止晶圓產生劃痕缺陷。WD4000晶圓

2025-09-11 16:41:24

景的方方面面;其射頻前端模組,則通過全集成設計、尖端材料應用和系統級封裝優化,使之更加適合智能時代的應用需求,更好地支撐用戶體驗。

2025-09-11 15:33:30 757

757 全新EVG?40 D2W套刻精度計量系統實現每顆芯片100%測量,吞吐量達行業基準15倍 2025年9月8日,奧地利圣弗洛里安 ——全球領先的先進半導體工藝解決方案與技術提供商EV 集團(EVG

2025-09-11 15:22:57 708

708 起來,催生出了卓勝微、唯捷創芯、昂瑞微、飛驤科技、銳石創芯和慧智微等多家優秀的射頻前端廠商。2023年,隨著國內頭部手機廠商突破制裁,成功量產基于全國產芯片的旗艦機,國產射頻前端廠家也借機突破了包括難度最高的sub3G L-PAMiD模組在

2025-09-11 12:49:33 624

624 本文主要講述什么是晶圓級芯粒封裝中的分立式功率器件。 分立式功率器件作為電源管理系統的核心單元,涵蓋二極管、MOSFET、IGBT等關鍵產品,在個人計算機、服務器等終端設備功率密度需求攀升的當下,其封裝技術正加速向晶圓級芯片級封裝演進——通過縮小體積、提升集成效率,滿足設備小型化與高性能的雙重需求。

2025-09-05 09:45:40 3095

3095

MEMS晶圓級電鍍是一種在微機電系統制造過程中,整個硅晶圓表面通過電化學方法選擇性沉積金屬微結構的關鍵工藝。該技術的核心在于其晶圓級和圖形化特性:它能在同一時間對晶圓上的成千上萬個器件結構進行批量加工,極大地提高了生產效率和一致性,是實現MEMS器件低成本、批量化制造的核心技術之一。

2025-09-01 16:07:28 2073

2073

近期隨著卓勝微和唯捷創芯半年報公布,兩家頭部射頻前端公司扣非后凈利潤都出現不同程度的虧損,一時間關于射頻前端內卷和關于射頻卷到“血流成河”的文章不斷爆出,筆者采訪了多位未上市或者在上市準備階段的射頻

2025-08-29 10:39:01 574

574 晶圓處理前端模塊是現代半導體制造裝備中的重要組成部分,承擔著在超凈環境中安全傳輸晶圓的關鍵任務。這類設備不僅要維持極高的潔凈度標準,還必須實現精準可靠的晶圓轉移,以滿足現代半導體制造對工藝精度和生產

2025-08-26 09:57:53 391

391 EFEM(設備前端模塊)晶圓搬運系統是半導體制造過程中不可或缺的關鍵設備,其主要作用是在超凈環境下實現晶圓的安全、精準傳輸。這類系統不僅需要維持極高的潔凈度標準,還必須確保晶圓傳輸的精確性和穩定性

2025-08-26 09:57:19 813

813 WD4000晶圓厚度翹曲度測量系統兼容不同材質不同粗糙度、可測量大翹曲wafer、測量晶圓雙面數據更準確。它通過非接觸測量,將晶圓的三維形貌進行重建,強大的測量分析軟件穩定計算晶圓厚度,TTV

2025-08-25 11:29:30

景無線通訊:作為驅動放大器,提高通信基站、中繼器等設備的數據傳輸距離與質量。衛星通信:在C 波段 VSAT 系統中實現高頻信號放大,支持寬帶數據傳輸。機載雷達:為雷達發射機提供高功率、高效率的射頻信號,增強探測能力。無線電設備:用于高頻無線通訊收發器,實現信號調制與解調的關鍵功能。

2025-08-25 10:06:43

簡單來說,Die(發音為/da?/,中文常稱為裸片、裸晶、晶粒或晶片)是指從一整片圓形硅晶圓(Wafer)上,通過精密切割(Dicing)工藝分離下來的、單個含有完整集成電路(IC)功能的小方塊。

2025-08-21 10:46:54 3214

3214 芯碁微裝直寫光刻設備批量導入國內多家封測龍頭 ? 8月19日,芯碁微裝宣布,其面向中道領域的晶圓級及板級直寫光刻設備系列已獲得重大市場突破。公司已與多家國內頭部封測企業簽訂采購訂單,產品主要應用于

2025-08-21 10:33:00 1560

1560 WD4000晶圓顯微形貌測量系統通過非接觸測量,將晶圓的三維形貌進行重建,強大的測量分析軟件穩定計算晶圓厚度,TTV,BOW、WARP、在高效測量測同時有效防止晶圓產生劃痕缺陷。WD4000晶圓顯微

2025-08-20 11:26:59

WD4000晶圓膜厚測量系統通過非接觸測量,將晶圓的三維形貌進行重建,強大的測量分析軟件穩定計算晶圓厚度,TTV,BOW、WARP、在高效測量測同時有效防止晶圓產生劃痕缺陷。WD4000晶圓膜厚測量

2025-08-12 15:47:19

本文主要講述TSV工藝中的硅晶圓減薄與銅平坦化。 硅晶圓減薄與銅平坦化作為 TSV 三維集成技術的核心環節,主要應用于含銅 TSV 互連的減薄芯片制造流程,為該技術實現短互連長度、小尺寸、高集成度等特性提供了重要支撐。

2025-08-12 10:35:00 1543

1543

半導體制造國產化浪潮中,晶圓傳輸效率直接制約產線吞吐量。傳統機械臂傳輸存在振動大、精度低的缺陷,而直線電機驅動的EFEM(設備前端模塊)憑借高速平滑運動,將晶圓交接時間縮短至0.8秒內,同時定位精度提升至微米級,成為12英寸晶圓廠優選方案。

2025-08-06 14:43:38 697

697 近年來,隨著半導體行業受到的關注度和注入的資金不斷提升,國內射頻前端廠商也發展迅速,催生出如卓勝微、唯捷創芯、昂瑞微、飛驤、銳石創芯和慧智微等優秀廠商。這些企業崛起到一定規模后,資金實力逐漸雄厚

2025-08-05 15:28:01 799

799

層析圖像,實現Wafer厚度、翹曲度、平面度、線粗糙度、總體厚度變化(TTV)及分析反映表面質量的2D、3D參數。WD4000晶圓三維顯微形貌測量系統通過非接觸測量

2025-08-04 13:59:53

退火工藝是晶圓制造中的關鍵步驟,通過控制加熱和冷卻過程,退火能夠緩解應力、修復晶格缺陷、激活摻雜原子,并改善材料的電學和機械性質。這些改進對于確保晶圓在后續加工和最終應用中的性能和可靠性至關重要。退火工藝在晶圓制造過程中扮演著至關重要的角色。

2025-08-01 09:35:23 2024

2024

、藥物篩選、微流控、細胞分析等應用的微型器件。以下是劃片機在生物晶圓芯片高精度切割中的應用和關鍵考慮因素:1.核心應用:芯片單體化:將包含成百上千個獨立生物芯片單元

2025-07-28 16:10:29 709

709

層析圖像,實現Wafer厚度、翹曲度、平面度、線粗糙度、總體厚度變化(TTV)及分析反映表面質量的2D、3D參數。WD4000晶圓THK膜厚厚度測量系統通過非接觸

2025-07-25 10:53:07

晶圓清洗機中的晶圓夾持是確保晶圓在清洗過程中保持穩定、避免污染或損傷的關鍵環節。以下是晶圓夾持的設計原理、技術要點及實現方式: 1. 夾持方式分類 根據晶圓尺寸(如2英寸到12英寸)和工藝需求,夾持

2025-07-23 14:25:43 928

928 Wafer Acceptance Test (WAT) 是晶圓制造中確保產品質量和可靠性的關鍵步驟。它通過對晶圓上關鍵參數的測量和分析,幫助識別工藝中的問題,并為良率提升提供數據支持。在芯片項目的量產管理中,WAT是您保持產線穩定性和產品質量的重要工具。

2025-07-17 11:43:31 2774

2774 WD4000晶圓厚度THK幾何量測系統兼容不同材質不同粗糙度、可測量大翹曲wafer、測量晶圓雙面數據更準確。它通過非接觸測量,將晶圓的三維形貌進行重建,強大的測量分析軟件穩定計算晶圓厚度,TTV

2025-07-10 13:42:33

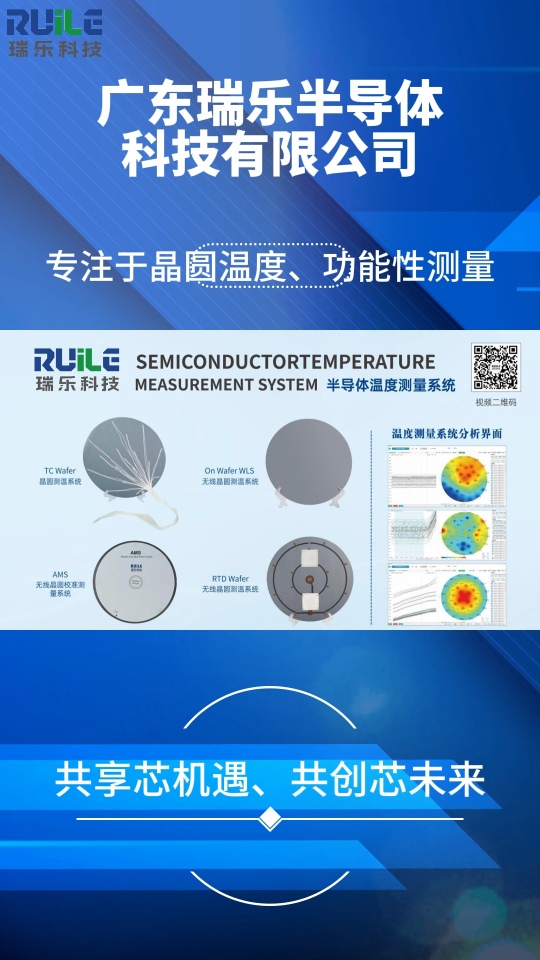

On Wafer WLS無線晶圓測溫系統通過自主研發的核心技術將傳感器嵌入晶圓集成,實時監控和記錄晶圓在制程過程中的溫度變化數據,為半導體制造過程提供一種高效可靠的方式來監測和優化關鍵

2025-06-27 10:37:30

TC Wafer 晶圓測溫系統通過利用自主研發的核心技術將耐高溫的熱電偶傳感器鑲嵌在晶圓表面,實時監控和記錄晶圓在制程過程中的溫度變化數據,為半導體制造過程提供一種高效可靠的方式來監測和優化關鍵

2025-06-27 10:16:41

RTD Wafer 晶圓測溫系統利用自主研發的核心技術將 RTD 傳感器集成到 晶圓表面,實時監控和記錄晶圓在制程過程中的溫度變化數據,為半導體 制造過程提供一種高效可靠的方式來監測和優化關鍵的工藝

2025-06-27 10:12:00

RTD Wafer 晶圓測溫系統利用自主研發的核心技術將 RTD 傳感器集成到晶圓表面,實時監控和記錄晶圓在制程過程中的溫度變化數據,為半導體 制造過程提供一種高效可靠的方式來監測和優化關鍵的工藝

2025-06-27 10:08:43

TCWafer晶圓測溫系統是一種革命性的溫度監測解決方案,專為半導體制造工藝中晶圓溫度的精確測量而設計。該系統通過將微型熱電偶傳感器(Thermocouple)直接鑲嵌于晶圓表面,實現了對晶圓溫度

2025-06-27 10:03:14 1396

1396

并購重組審核委員會審議通過,后續尚需取得中國證監會同意注冊的決定后方可實施。 芯聯集成是全球領先的集成電路晶圓代工企業之一,根據ChipInsights發布的《2024年全球專屬晶圓代工排行榜》,芯聯集成躋身2024年全球專屬晶圓代工榜單前十,中

2025-06-25 18:11:40 1062

1062

高反射率的物體表面,從納米到微米級別工件的厚度、粗糙度、平整度、微觀幾何輪廓、曲率等,實現砷化鎵、氮化鎵、磷化鎵、鍺、磷化銦、鈮酸鋰、藍寶石、硅、碳化硅、玻璃不同

2025-06-16 15:08:07

,首先介紹了 Ga2O3在射頻器件領域的優勢和面臨的挑戰,然后綜述了近年來 Ga2O3射頻器件在體摻雜溝道、AlGaO/Ga2O3調制 摻雜異質結以及與高導熱襯底異質集成方面取得的進展,并對研究結果進行了討論,最后展望了未來 Ga2O3射頻器 件的發展前景。

2025-06-11 14:30:06 2163

2163

晶圓級扇出封裝(FO-WLP)通過環氧樹脂模塑料(EMC)擴展芯片有效面積,突破了扇入型封裝的I/O密度限制,但其技術復雜度呈指數級增長。

2025-06-05 16:25:57 2143

2143

本文介紹了在射頻前端模塊(RF-FEM)中使用的集成無源元件(IPD)技術。

2025-06-03 18:26:51 1266

1266

在微電子行業飛速發展的背景下,封裝技術已成為連接芯片創新與系統應用的核心紐帶。其核心價值不僅體現于物理防護與電氣/光學互聯等基礎功能,更在于應對多元化市場需求的適應性突破,本文著力介紹晶圓級扇入封裝,分述如下。

2025-06-03 18:22:20 1054

1054

反應表面形貌的參數。可實現砷化鎵、氮化鎵、磷化鎵、鍺、磷化銦、鈮酸鋰、藍寶石、硅、碳化硅、玻璃不同材質晶圓的量測。兼容不同材質不同粗糙度、可測量大翹曲wafer、

2025-05-30 11:03:11

測應用。

(1)搭配中圖全自主研發的EFEM系統,可以適配loadport、smifport、carrier等多種形式,實現全自動上下料,實現在單系統內完成晶圓厚度、平坦度、粗糙度、膜厚等面型參數的高精度

2025-05-28 16:12:46

波濾波電路。其單芯片設計顯著簡化了外圍電路,適合對尺寸和功耗敏感的物聯網設備,如Zigbee、智能家居和工業自動化系統。 CMOS工藝優勢?: 低成本?:相比傳統砷化鎵(GaAs)工藝,CMOS更適合大規模量產,降低芯片成本。 高集成度?:可與其他數字電路(如微控制器)

2025-05-27 15:00:01 1773

1773

WD4000系列Wafer晶圓厚度量測系統采用白光光譜共焦多傳感器和白光干涉顯微測量雙向掃描技術,完成非接觸式掃描并建立表面3D層析圖像,實現Wafer厚度、翹曲度、平面度、線粗糙度、總體厚度變化

2025-05-27 13:54:33

、商業級:0℃ ~ +70℃、工業級:-40℃~+85℃;

適用于工業、AIoT、邊緣計算、智能移動終端以及其他多種數字多媒體等場景。

米爾基于瑞芯微 RK3576 開發板

總結:

米爾的多種系統方案

2025-05-23 16:07:10

相機與光學系統,可實現亞微米級缺陷檢測,提升半導體制造的良率和效率。SWIR相機晶圓隱裂檢測系統,使用紅外相機發揮波段長穿透性強的特性進行材質透檢捕捉內部隱裂缺陷

2025-05-23 16:03:17 647

647

WD4000晶圓Warp翹曲度量測系統采用高精度光譜共焦傳感技術、光干涉雙向掃描技術,完成非接觸式掃描并建立3D Mapping圖,實現晶圓厚度、TTV、LTV、Bow、Warp、TIR、SORI

2025-05-20 14:02:17

近日,極米Z6X Pro系列投影儀震撼登場,搭載北極芯微DTS6004模組芯片的傳感器,已成功導入該投影儀并推向市場。北極芯微dToF傳感器深度賦能,為投影儀注入“芯”動力,攜手開啟智能投影新體驗。

2025-05-14 15:49:57 1117

1117 我們看下一個先進封裝的關鍵概念——晶圓級封裝(Wafer Level Package,WLP)。

2025-05-14 10:32:30 1532

1532

在半導體制造流程中,晶圓在前端工藝階段需保持一定厚度,以確保其在流片過程中的結構穩定性,避免彎曲變形,并為芯片制造工藝提供操作便利。不同規格晶圓的原始厚度存在差異:4英寸晶圓厚度約為520微米,6

2025-05-09 13:55:51 1975

1975 圓片級封裝(WLP),也稱為晶圓級封裝,是一種直接在晶圓上完成大部分或全部封裝測試程序,再進行切割制成單顆組件的先進封裝技術 。WLP自2000年左右問世以來,已逐漸成為半導體封裝領域的主流技術,深刻改變了傳統封裝的流程與模式。

2025-05-08 15:09:36 2067

2067

隨著半導體工藝復雜度提升,可靠性要求與測試成本及時間之間的矛盾日益凸顯。晶圓級可靠性(Wafer Level Reliability, WLR)技術通過直接在未封裝晶圓上施加加速應力,實現快速

2025-05-07 20:34:21

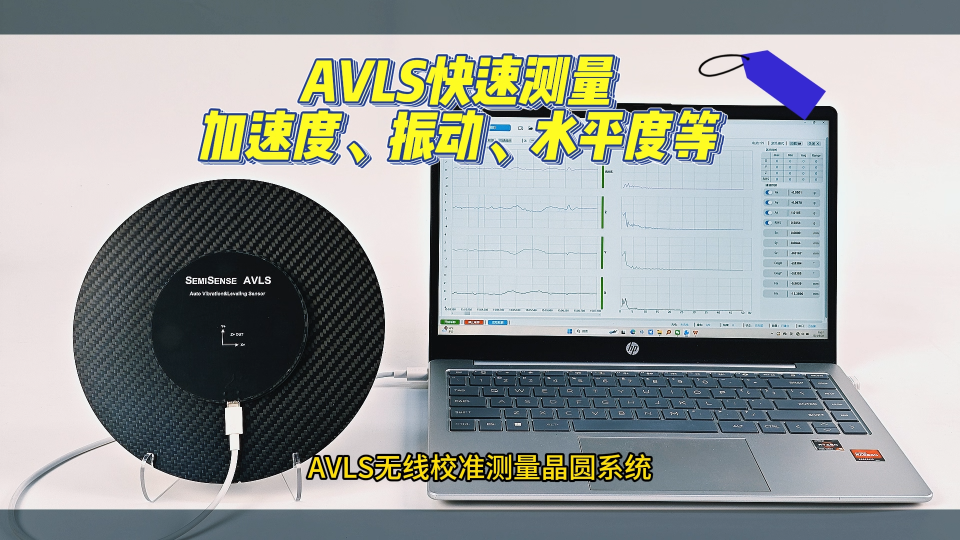

AVS 無線校準測量晶圓系統就像給晶圓運輸過程裝上了"全天候監護儀",推動先進邏輯芯片制造、存儲器生產及化合物半導體加工等關鍵制程的智能化質量管控,既保障價值百萬的晶圓安全,又能讓價值數千萬的設備發揮最大效能,實現降本增效。

2025-04-24 14:57:49 866

866

On Wafer WLS-WET無線晶圓測溫系統是半導體先進制程監控領域的重要創新成果。該系統通過自主研發的核心技術,將溫度傳感器嵌入晶圓集成,實現了晶圓本體與傳感單元的無縫融合。傳感器采用IC傳感器,具備±0.1℃的測量精度和10ms級快速響應特性,可實時捕捉濕法工藝中瞬態溫度場分布。

2025-04-22 11:34:40 670

670

本文介紹了半導體集成電路制造中的晶圓制備、晶圓制造和晶圓測試三個關鍵環節。

2025-04-15 17:14:37 2155

2155

WD4000晶圓表面形貌量測系統通過非接觸測量,將晶圓的三維形貌進行重建,強大的測量分析軟件穩定計算晶圓厚度,TTV,BOW、WARP、在高效測量測同時有效防止晶圓產生劃痕缺陷。

2025-04-11 11:11:00

在SEMICON China 2025展會期間,中微半導體設備(上海)股份有限公司(以下簡稱“中微公司”,股票代碼“688012.SH”)宣布其自主研發的12英寸晶圓邊緣刻蝕設備Primo

2025-03-28 09:21:19 1192

1192 隨著半導體工藝復雜度提升,可靠性要求與測試成本及時間之間的矛盾日益凸顯。晶圓級可靠性(Wafer Level Reliability, WLR)技術通過直接在未封裝晶圓上施加加速應力,實現快速、低成本的可靠性評估,成為工藝開發的關鍵工具。

2025-03-26 09:50:16 1548

1548

方案提供服務的領導者EV集團(EV Group,簡稱EVG)今日發布下一代GEMINI?自動化晶圓鍵合系統,專為300毫米(12英寸)晶圓量產設計。該系統的核心升級為全新開發的高精度強力鍵合模塊,在滿足全球

2025-03-20 09:07:58 889

889

WD4000系列晶圓微觀幾何輪廓測量系統采用高精度光譜共焦傳感技術、光干涉雙向掃描技術,完成非接觸式掃描并建立3D Mapping圖,實現晶圓厚度、TTV、LTV、Bow、Warp、TIR、SORI

2025-03-19 17:36:45

2024年,國芯科技與戰略合作伙伴深圳美電科技有限公司(以下簡稱“美電科技”)展開了深度合作。雙方以國芯科技首顆端側AI芯片CCR4001S為核心,攜手推出AI傳感器模組,迅速且緊密地圍繞該模組開展全方位、多維度的應用開發工作。如今,這款模組已成功實現應用。

2025-03-18 16:34:46 1008

1008

MEMS傳感器晶圓劃片機技術特點與應用分析MEMS(微機電系統)傳感器晶圓劃片機是用于切割MEMS傳感器晶圓的關鍵設備,需滿足高精度、低損傷及工藝適配性等要求。以下是相關技術特點、工藝難點及國產化

2025-03-13 16:17:45 859

859

異構集成封裝產業大會(浙江寧波)點此報名添加文末微信,加先進封裝群會議議程會議基本信息會議名稱:2025勢銀異質異構集成封裝產業大會指導單位:鎮海區人民政府(擬)

2025-03-13 09:41:36 1269

1269

高精度晶圓劃片機切割解決方案為實現高精度晶圓切割,需從設備精度、工藝穩定性、智能化控制等多維度優化,以下為關鍵實現路徑及技術支撐:一、核心精度控制技術?雙軸協同與高精度運動系統?雙工位同步切割技術

2025-03-11 17:27:52 797

797

CHA5659-98F/CHA5659-QXG是法國UMS公司推出的四級單片砷化鎵(GaAs)高功率放大器,專為36-43.5GHz毫米波頻段設計。該器件采用先進的0.15μm pHEMT工藝制造,在K波段衛星通信和點對點無線電系統中展現卓越性能。

2025-03-07 16:24:08 1114

1114

WD4000晶圓翹曲度幾何量測系統兼容不同材質不同粗糙度、可測量大翹曲wafer、測量晶圓雙面數據更準確。儀器通過非接觸測量,將晶圓的三維形貌進行重建,強大的測量分析軟件穩定計算晶圓厚度,TTV

2025-03-07 16:19:24

隨著半導體技術的飛速發展,晶圓級封裝(WLP)作為先進封裝技術的重要組成部分,正逐漸成為集成電路封裝的主流趨勢。在晶圓級封裝過程中,Bump工藝扮演著至關重要的角色。Bump,即凸塊,是晶圓級封裝中

2025-03-04 10:52:57 4978

4978

為一家專注于智能制造解決方案的高科技企業,通過技術創新與行業深耕,致力于為客戶提供高效、智能的制造系統,助力企業實現數字化轉型。在SMT加工中,故障排除是一個復雜但系統的過程,需要從多個角度入手,快速

2025-02-14 12:48:00

WD4000高精度晶圓厚度幾何量測系統兼容不同材質不同粗糙度、可測量大翹曲wafer、測量晶圓雙面數據更準確。它通過非接觸測量,將晶圓的三維形貌進行重建,強大的測量分析軟件穩定計算晶圓厚度,TTV

2025-02-11 14:01:06

近日,晶合集成發布公告,宣布與十五家外部投資者就向全資子公司皖芯集成增資事宜簽署了增資協議,且協議條款保持一致。這一舉動不僅彰顯了市場對晶合集成及其子公司皖芯集成的強烈信心,更預示著公司在半導體領域

2025-01-22 16:54:51 1786

1786 扇出型晶圓級中介層封裝( FOWLP)以及封裝堆疊(Package-on-Package, PoP)設計在移動應用中具有許多優勢,例如低功耗、短信號路徑、小外形尺寸以及多功能的異構集成。此外,它還

2025-01-22 14:57:52 4507

4507

(Ga2O3)晶相異質結(Phase Heterojunction)的新研究發表在《Advanced Materials》上。 論文第一作者為陸義博士 。文章首次在實驗中展示了β相和κ相Ga2O3之間

2025-01-22 14:12:07 1133

1133

瑞芯微Android系統電源指示燈怎么將藍色的燈改成綠色的

2025-01-10 15:19:17

。在此之前,皖芯集成的注冊資本僅為5000.01萬元。 本次增資完成后,晶合集成持有皖芯集成的股權比例變更為43.75%,仍為第一大股東。 據TrendForce公布的24Q1全球晶圓代工廠商營收排名,晶合集成位居全球前九,是中國大陸本土第三的晶圓代工廠商。

2025-01-07 17:33:09 778

778

隨著半導體技術的飛速發展,晶圓級封裝(Wafer Level Packaging, WLP)作為一種先進的封裝技術,正逐漸在集成電路封裝領域占據主導地位。晶圓級封裝技術以其高密度、高可靠性、小尺寸

2025-01-07 11:21:59 3190

3190

電子發燒友App

電子發燒友App

評論