文章來源:老虎說芯

原文作者:老虎說芯

本文主要講述晶圓制造中的Die是什么。

1. 什么是Die?(What is a Die?)

簡單來說,Die(發音為/da?/,中文常稱為裸片、裸晶、晶粒或晶片)是指從一整片圓形硅晶圓(Wafer)上,通過精密切割(Dicing)工藝分離下來的、單個含有完整集成電路(IC)功能的小方塊。

你可以把它想象成:

晶圓 (Wafer)是一張印滿了郵票的大版紙。

Die (晶粒)就是從這張大版紙上撕下來的那一枚枚獨立的郵票。

每一片Die都是一個未經封裝的、功能齊全的電路單元,比如一個CPU核心、一個GPU核心、一個存儲器模塊或一個射頻收發器。

關鍵點:

形態:通常是正方形或矩形,非常薄,表面有極其復雜的電路結構。

材質:主要由高純度單晶硅制成。

狀態:這是未封裝(Unpackaged)的狀態。它非常脆弱,直接暴露在空氣中容易受到污染和物理損傷。

單復數:它的單數是Die,復數是Dice或Dies。

2. Die的生命周期:從晶圓到芯片 (The Lifecycle of a Die)

要理解Die,最好的方式是了解它在整個生產流程中的位置。

第1步:晶圓制造 (Wafer Fabrication)

一切始于一塊高純度的硅晶圓(Wafer)。

在超凈間(Cleanroom)里,通過光刻(Photolithography)、蝕刻(Etching)、薄膜沉積(Deposition)、離子注入(Ion Implantation)等數百道復雜工序,在晶圓表面制作出成千上萬個完全相同的電路結構。

此時,所有的Die還都連在一起,共同存在于晶圓之上,形成一個網格狀陣列(Array)。

第2步:晶圓測試 (Wafer Probing / CP Test)

在切割之前,需要對晶圓上的每一個Die進行初步的電性測試。

這個過程叫做晶圓探針測試(Circuit Probing, 簡稱CP測試)。探針卡(Probe Card)上的細小探針會接觸到每個Die上的焊盤(Bond Pad),以檢測其功能是否正常。

測試不合格的Die會被標記下來(傳統上是點上墨點,現在通常是在電子地圖Wafer Map中記錄),在后續工序中被廢棄。這個步驟是為了盡早剔除次品,避免在無用的Die上浪費后續的封裝成本。

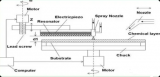

第3步:晶圓切割 (Wafer Dicing)

通過CP測試的晶圓會被送到切割機(Dicing Saw)上。

高速旋轉的鉆石切割刀會沿著Die之間的**切割道(Scribe Line)**進行精確切割,將一整片晶圓分離成數千個獨立的Die。

第4步:芯片封裝 (Packaging / Assembly)

從晶圓上取下的合格Die(此時稱為Good Die),會被送入封裝流程。

a. 固晶 (Die Attach):將Die的背面粘貼到封裝基板(Substrate)或引線框架(Leadframe)上。

b. 引線鍵合 (Wire Bonding / Flip-Chip):建立Die與外部世界的電氣連接。

引線鍵合 (Wire Bonding):用極細的金線或銅線,將Die上的焊盤(Bond Pad)連接到基板或引腳上。

倒裝焊 (Flip-Chip):Die的正面(有電路的一面)直接朝下,通過其上的焊球(Solder Bump)直接連接到基板上。這種方式路徑更短,性能更好,是高性能芯片的主流選擇。

c. 塑封 (Molding):用環氧樹脂(Epoxy)將Die、引線等所有內部結構包裹起來,形成我們常見的黑色“芯片”外觀。這起到了保護內部Die、散熱和方便安裝的作用。

經過封裝后,脆弱的Die就變成了堅固耐用的芯片(Chip)或IC,可以焊接到PCB板上使用了。

3. 為什么Die的概念對工程師如此重要?

不同領域的工程師關注Die的不同方面,它是連接設計和制造的橋梁。

對于IC設計工程師 (Design Engineer):

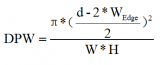

Die Size (晶粒面積)是成本的決定性因素。Die越小,一片晶圓上能生產出的Die就越多(Gross Die per Wafer),單個Die的成本就越低。因此,在滿足性能的前提下,優化布局布線以縮小Die Size是設計的核心目標之一。

焊盤布局 (Pad Layout)直接影響到后續的封裝方案和信號完整性。

對于工藝/制造工程師 (Process/Manufacturing Engineer):

良率 (Yield)是他們的生命線。良率 = (一片晶圓上合格的Die數量) / (總Die數量)。他們致力于通過優化生產工藝,減少缺陷,提高每一個Die的功能完好率。

對于封裝工程師 (Packaging Engineer):

Die是他們工作的起點。他們需要根據Die的尺寸、厚度、焊盤位置、功耗(散熱需求)來設計最合適的封裝方案,確保電氣性能、散熱性能和可靠性。

對于測試工程師 (Test Engineer):

他們需要針對Die的功能編寫測試程序,無論是在切割前的CP測試,還是封裝后的成品測試(Final Test, FT),都是為了確保Die的功能符合設計規范。

總而言之,Die是半導體價值鏈的絕對核心。它是在硅晶圓上制造的、包含完整電路功能的、未經封裝的裸露芯片。

它是設計的畫布:承載著電路設計的智慧。

它是制造的成果:體現了半導體工藝的極限。

它是成本的基石:其面積和良率直接決定了最終產品的價格。

它是性能的源泉:芯片的所有計算和處理能力都源于這塊小小的硅片。

-

芯片

+關注

關注

463文章

54007瀏覽量

465928 -

晶圓制造

+關注

關注

7文章

310瀏覽量

25281 -

晶粒

+關注

關注

0文章

30瀏覽量

4214

原文標題:深入理解晶圓制造中的Die

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

晶圓制造過程中哪些環節最易受污染

晶圓制造中的Die是什么

晶圓制造中的Die是什么

評論