文章來源:學(xué)習(xí)那些事

原文作者:小陳婆婆

本文主要講述WLP與MCM封裝。

晶圓級封裝(WLP)與多芯片組件(MCM)作為先進(jìn)封裝的“雙引擎”,前者在晶圓未切割時(shí)即完成再布線與凸點(diǎn)制作,以“封裝即制造”實(shí)現(xiàn)芯片級尺寸、70 μm以下超細(xì)間距與電熱性能躍升;后者把多顆已驗(yàn)證的LSI/VLSI裸片高密度集成于多層基板,用“拼裝式系統(tǒng)”突破單芯片復(fù)雜度瓶頸,在5G、AI、自動(dòng)駕駛等場景持續(xù)刷新集成度與能效紀(jì)錄。兩條技術(shù)路線一縱一橫,正攜手將集成電路產(chǎn)業(yè)推向后摩爾時(shí)代的“高密度、低功耗、系統(tǒng)級”新賽道。

晶圓級封裝(WLP)

晶圓級封裝(WLP)作為先進(jìn)封裝技術(shù)的核心分支,正隨著芯片特征尺寸的持續(xù)縮小與集成度飆升,演變?yōu)橥黄莆锢順O限的關(guān)鍵路徑。其核心邏輯在于通過晶圓級批量處理實(shí)現(xiàn)封裝與制造的深度融合——在晶圓未切割階段即完成薄膜再分布與凸點(diǎn)制作,使封裝尺寸與芯片尺寸趨同,既滿足高I/O密度需求(如70μm以下間距),又通過縮短互連路徑降低寄生參數(shù),提升電熱性能。

WLP的技術(shù)基石在于薄膜再分布(RDL)與凸點(diǎn)制作工藝。RDL通過光刻-金屬沉積-刻蝕流程,將芯片周邊I/O焊盤重構(gòu)為表面陣列凸點(diǎn)焊區(qū),配合UBM(凸點(diǎn)下金屬層)的沉積與凸點(diǎn)成型,形成球柵陣列(BGA)。凸點(diǎn)制作依據(jù)間距需求采用預(yù)制焊球、絲網(wǎng)印刷或電化學(xué)沉積技術(shù),其中電鍍工藝憑借自對準(zhǔn)特性可實(shí)現(xiàn)最小凸點(diǎn)尺寸與最高密度,滿足200μm以下間距的嚴(yán)苛要求。

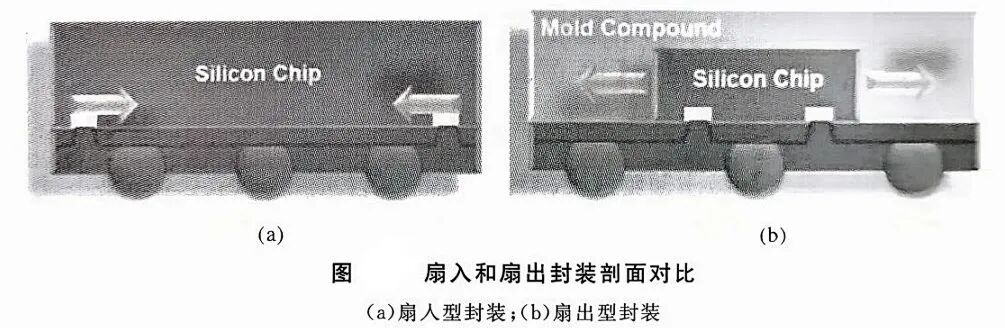

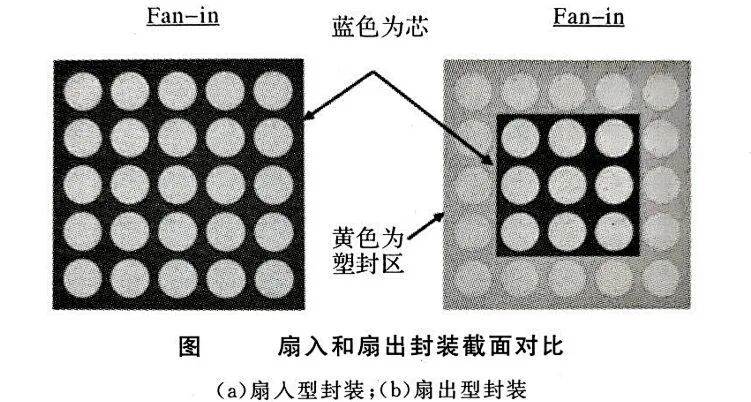

從結(jié)構(gòu)類型看,WLP分為扇入式(Fan-in)與扇出式(Fan-out)兩大路徑。

扇入式封裝在晶圓切割前完成全流程,封裝尺寸與芯片尺寸一致,適用于I/O數(shù)低于400的小尺寸芯片,典型應(yīng)用如消費(fèi)電子中的低功耗芯片。

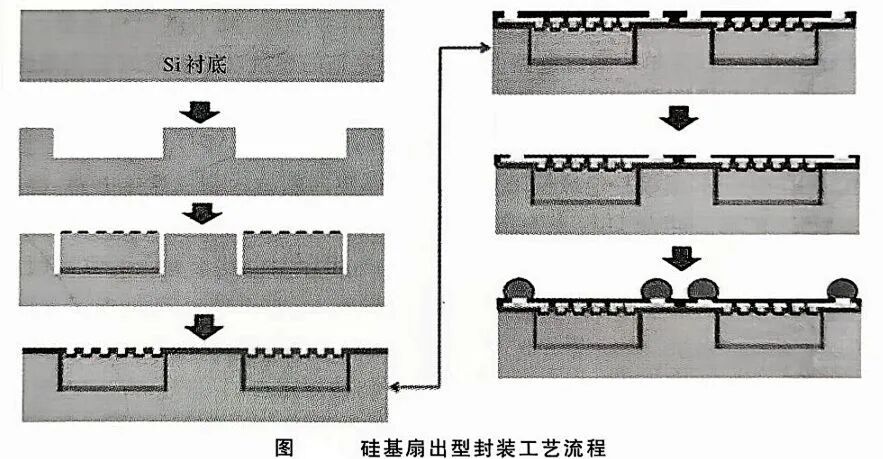

扇出式則通過重構(gòu)晶圓實(shí)現(xiàn)尺寸擴(kuò)展,支持更高I/O密度與三維集成——芯片先上(Die First)工藝如eWLB通過預(yù)置芯片后布線提升良率,芯片后上(Die Last)則通過先布線再貼裝優(yōu)化流程,安靠、日月光等廠商均已實(shí)現(xiàn)成熟量產(chǎn)。硅基扇出型封裝(eSiFO)更以硅基板為載體,通過凹槽嵌入芯片實(shí)現(xiàn)低翹曲、高散熱與高布線密度,結(jié)合TSV技術(shù)可進(jìn)一步實(shí)現(xiàn)3D堆疊,在AI芯片、高性能計(jì)算領(lǐng)域展現(xiàn)顯著性能優(yōu)勢。

當(dāng)前,WLP技術(shù)正朝著更高集成度、更低成本與智能化方向發(fā)展。3D集成技術(shù)通過硅通孔(TSV)與混合鍵合實(shí)現(xiàn)多層芯片堆疊,縮短互連長度至微米級,提升帶寬密度;石墨烯、氮化鎵等新型材料在RDL中的應(yīng)用,正推動(dòng)導(dǎo)電性與熱管理性能的突破;AI驅(qū)動(dòng)的檢測系統(tǒng)通過機(jī)器學(xué)習(xí)算法實(shí)現(xiàn)缺陷自動(dòng)分類與良率預(yù)測,結(jié)合相干探測顯微鏡、太赫茲成像等無損檢測手段,構(gòu)建起全鏈條質(zhì)量監(jiān)控網(wǎng)絡(luò)。

在應(yīng)用層面,WLP已深度滲透智能手機(jī)、圖像傳感器、汽車電子等領(lǐng)域,并隨著金線成本上升,逐步替代傳統(tǒng)引線鍵合工藝,成為高引腳數(shù)器件的主流方案。未來,隨著eSiFO與3D-WLP的融合創(chuàng)新,以及智能檢測技術(shù)的持續(xù)迭代,WLP有望在異構(gòu)集成、系統(tǒng)級封裝(SiP)中扮演更核心的角色,推動(dòng)集成電路產(chǎn)業(yè)向更高性能、更低功耗的終極目標(biāo)邁進(jìn)。

多芯片組件(MCM)

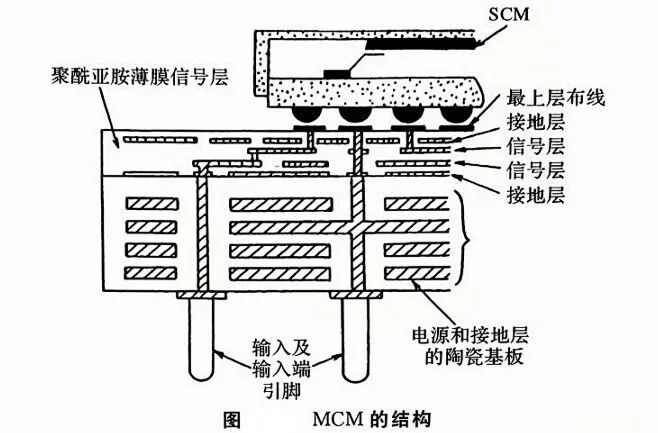

多芯片組件(MCM)作為混合集成電路的演進(jìn)形態(tài),通過將多個(gè)LSI/VLSI芯片高密度集成于多層互連基板并封裝于單一外殼內(nèi),構(gòu)建出兼具高密度、高可靠性與系統(tǒng)級功能的專用電子產(chǎn)品。其核心價(jià)值在于突破單芯片研發(fā)的復(fù)雜度限制——通過組合成熟芯片實(shí)現(xiàn)系統(tǒng)功能,既降低研發(fā)成本與技術(shù)風(fēng)險(xiǎn),又適配小型化便攜產(chǎn)品對高組裝密度、短互連路徑的需求,從而減少信號延遲、縮小體積重量,并提升性能、保密性及可靠性。

從工藝與基板維度,MCM分為三大類:MCM-C以陶瓷為基板,采用厚膜印刷與共燒工藝形成導(dǎo)體電路,憑借陶瓷的高熱導(dǎo)率與氣密性,廣泛應(yīng)用于航空航天、汽車電子等高可靠性場景;MCM-D通過薄膜沉積技術(shù)交替疊加導(dǎo)體與絕緣層,構(gòu)建多層連線基板,支持更精細(xì)的線寬與更高的布線密度,適用于高性能計(jì)算與射頻模塊;MCM-L則基于印制電路板疊合工藝,以層壓板為基板,兼顧成本優(yōu)勢與批量生產(chǎn)能力,常見于消費(fèi)電子領(lǐng)域。近年來,復(fù)合型MCM如MCM-D/L、MCM-D/C等分支產(chǎn)品涌現(xiàn),通過融合不同基板材料的特性,實(shí)現(xiàn)性能與成本的平衡,例如硅基MCM(MCM-Si)利用硅的高熱導(dǎo)率與CMOS兼容性,在三維集成中展現(xiàn)獨(dú)特優(yōu)勢。

MCM的結(jié)構(gòu)設(shè)計(jì)涵蓋IC裸芯片、芯片互連、多層基板及封裝外殼四大要素。裸芯片作為信號與功率源,通過凸點(diǎn)與基板實(shí)現(xiàn)電氣與機(jī)械連接;多層基板采用先進(jìn)互連技術(shù),如微孔填充、埋入式電阻/電容,實(shí)現(xiàn)信號的垂直互連與電源分配;封裝外殼則承擔(dān)污染防護(hù)、機(jī)械應(yīng)力緩沖及散熱功能,常見材料包括金屬、陶瓷及塑料,選擇依據(jù)熱管理需求與環(huán)境適應(yīng)性而定。

在制造技術(shù)層面,芯片互連組裝是關(guān)鍵環(huán)節(jié)。芯片與基板的黏結(jié)采用導(dǎo)電膠或含銀環(huán)氧樹脂,前者兼顧導(dǎo)電性與熱導(dǎo)率,后者通過優(yōu)化填料粒徑提升熱管理性能;電氣連接技術(shù)從傳統(tǒng)絲焊、TAB發(fā)展至倒裝焊(Flip Chip)、C4(Controlled Collapse Chip Connection)及微型凸點(diǎn)技術(shù),其中倒裝焊通過凸點(diǎn)直接連接芯片與基板,顯著縮短互連長度,提升信號傳輸速率;基板與外殼的物理連接以黏合劑焊接為主,電氣連接則通過絲焊過渡引線實(shí)現(xiàn)外引腳與基板焊區(qū)的對接。

當(dāng)前,MCM技術(shù)正朝著更高集成度、更低功耗與智能化方向演進(jìn)。3D MCM通過硅通孔(TSV)與混合鍵合實(shí)現(xiàn)多層芯片垂直堆疊,結(jié)合玻璃基板等新型材料提升熱管理性能;AI驅(qū)動(dòng)的設(shè)計(jì)工具通過優(yōu)化布局布線與熱仿真,提升設(shè)計(jì)效率與可靠性;環(huán)保型封裝材料如生物基環(huán)氧樹脂、可回收陶瓷的應(yīng)用,推動(dòng)綠色制造發(fā)展。

在應(yīng)用層面,MCM已深度滲透5G通信、人工智能、自動(dòng)駕駛等領(lǐng)域,例如在AI加速卡中,MCM通過集成多顆高性能芯片實(shí)現(xiàn)計(jì)算密度與能效的雙重提升,成為支撐系統(tǒng)級創(chuàng)新的關(guān)鍵技術(shù)載體。未來,隨著異構(gòu)集成與先進(jìn)封裝技術(shù)的融合,MCM有望在更廣泛的領(lǐng)域?qū)崿F(xiàn)性能突破與成本優(yōu)化,持續(xù)推動(dòng)電子產(chǎn)品的創(chuàng)新與升級。

-

芯片

+關(guān)注

關(guān)注

463文章

54267瀏覽量

468291 -

晶圓

+關(guān)注

關(guān)注

53文章

5437瀏覽量

132599 -

封裝

+關(guān)注

關(guān)注

128文章

9306瀏覽量

148947

原文標(biāo)題:WLP與MCM封裝

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

一文詳解多芯片組件MCM技術(shù)

HRP晶圓級先進(jìn)封裝替代傳統(tǒng)封裝技術(shù)研究(HRP晶圓級先進(jìn)封裝芯片)

一文詳解晶圓級封裝與多芯片組件

一文詳解晶圓級封裝與多芯片組件

評論