HDMI接口顯示使用DMT時序+TMDS編碼來實現。當用FPGA控制HDMI的數據傳輸時,通常可以采用純RTL實現TMDS算法或者使用專門的HDMI芯片(如ADV7513)這兩種方案來完成。本文主要是介紹如何用FPGA控制ADV7513實現HDMI畫面顯示和音頻播放。

2025-12-02 11:05:29 4543

4543

應用。

FPGA的開發是邏輯實現+約束+綜合+仿真,嵌入式的開發是編碼+編譯+調試,如果是對數字電路設計感興趣,可以考慮FPGA。

?在了解下就業機會哪個多?

?1、嵌入式的就業機會很多,優點就是就業容易,因為

2025-11-20 07:12:55

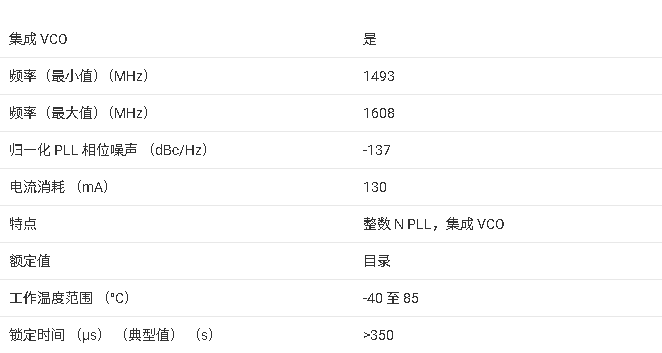

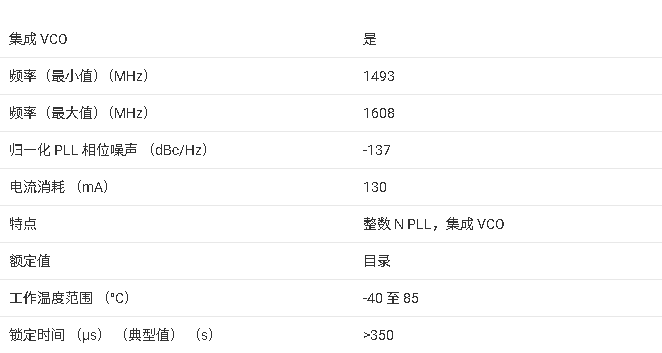

AC1571 是用于 5G 基站應用的基于 PLL的時鐘發生器,該芯片采用全數字鎖相環技術,以實現最佳的高頻低相噪性能,并具有低功耗和高PSRR能力。典型應用場景:· 無線基站·

2025-11-11 16:43:24

FPGA引腳中,在基于邏輯的邊沿變化采集時并不能對準數據穩定的時刻,而不能正確采集到數據。為了在時鐘跳變時能對準數據的穩定時刻,通常在設計時可以采用以下方法:專用IP核延遲、鎖相環移相和門電路延遲。邏輯

2025-10-29 07:38:04

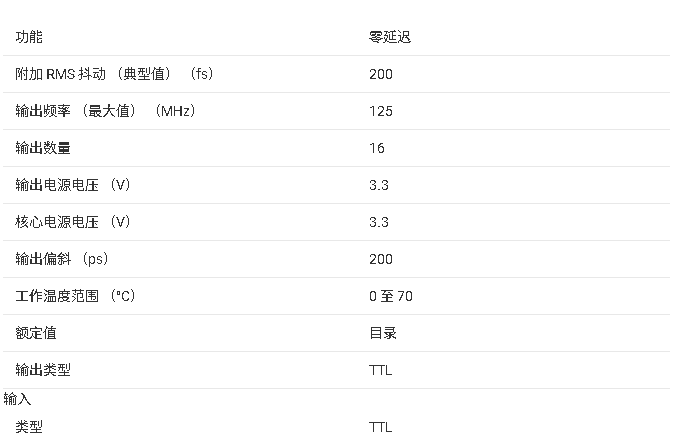

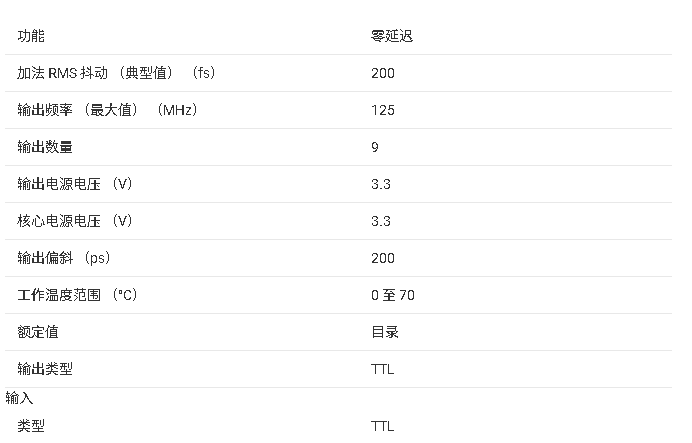

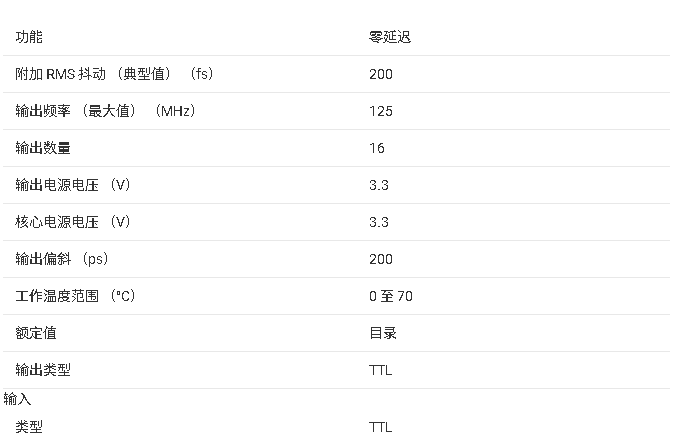

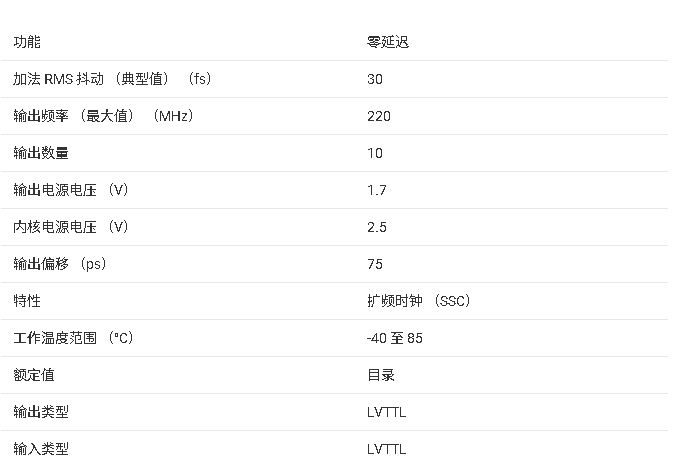

該CDCVF2510是一款高性能、低偏斜、低抖動、鎖相環 (PLL) 時鐘驅動器。它使用鎖相環 (PLL) 將反饋 (FBOUT) 輸出與時鐘 (CLK) 輸入信號在頻率和相位上精確對齊。它專為

2025-10-08 10:00:00 662

662

用來描述集成到設備中的力或觸覺反饋機制,以增強人機互動。 從工程學的角度來看,觸覺反饋通常通過機械致動器來實現。這些致動器可產生受控振動、運動或力,具體包括偏心旋轉質量塊 (ERM) 電機、線性諧振致動器 (LRA) 和壓電元件,可模擬現實世界中的物理感覺,如壓力、重

2025-10-03 17:45:00 1735

1735

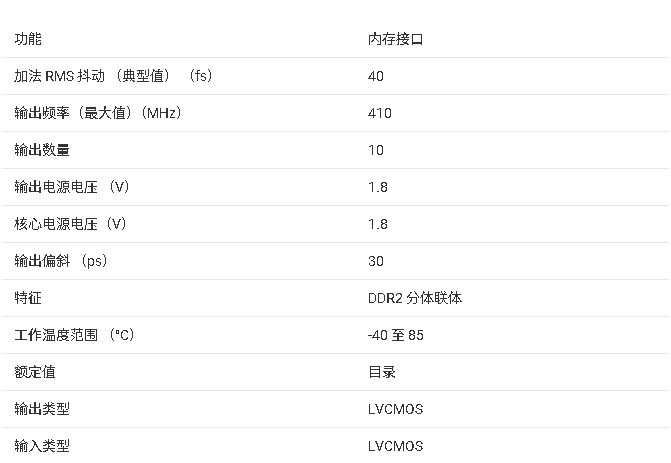

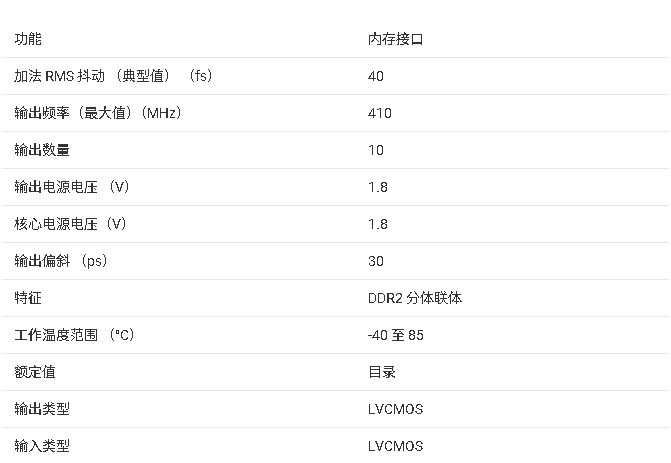

CDC2536是一款高性能、低偏斜、低抖動的時鐘驅動器。它使用鎖相環 (PLL) 將時鐘輸出信號在頻率和相位上精確對齊到時鐘輸入 (CLKIN) 信號。它專門設計用于同步 DRAM 和流行的微處理器

2025-09-24 14:10:43 642

642

CDC536 是一款高性能、低偏斜、低抖動的時鐘驅動器。它使用鎖相環 (PLL) 來精確地 在頻率和相位上,將時鐘輸出信號與時鐘輸入 (CLKIN) 信號對齊。具體來說 設計用于同步 DRAM

2025-09-24 10:15:48 1091

1091

CDC516 是一款高性能、低偏斜、低抖動、鎖相環時鐘驅動器。它使用鎖相環 (PLL) 將反饋輸出 (FBOUT) 與時鐘 (CLK) 輸入信號在頻率和相位上精確對齊。它專為與同步 DRAM 一起使用而設計。CDC516 的工作電壓為 3.3V V~CC~設計用于驅動每個輸出多達五個時鐘負載。

2025-09-23 10:15:40 761

761

CDC509 是一款高性能、低偏斜、低抖動、鎖相環 (PLL) 時鐘驅動器。它使用 PLL 在頻率和相位上將反饋 (FBOUT) 輸出精確對齊到時鐘 (CLK) 輸入信號。它專為與同步 DRAM 一起使用而設計。CDC509 的工作電壓為 3.3V V~CC~設計用于驅動每個輸出多達五個時鐘負載。

2025-09-23 10:09:13 795

795

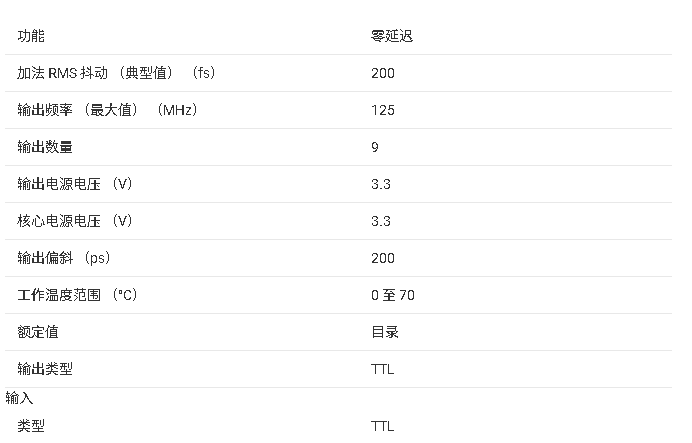

該CDCVF2509是一款高性能、低偏斜、低抖動、鎖相環 (PLL) 時鐘驅動器。該器件使用 PLL 將反饋 (FBOUT) 輸出與時鐘 (CLK) 輸入信號在頻率和相位上精確對齊。該器件專為與同步

2025-09-22 16:22:01 761

761

CDCVF25081是一款高性能、低偏斜、低抖動、鎖相環時鐘驅動器。它使用 PLL 將輸出時鐘在頻率和相位上精確對齊輸入時鐘信號。輸出分為 2 個組,總共 8 個緩沖 CLKIN 輸出。當不存在 CLKIN 信號時,該器件會自動將輸出置于低電平狀態(掉電模式)。

2025-09-22 15:39:14 675

675

、FBOUT)。時鐘輸出由時鐘輸入(CLK、CLK)、反饋時鐘(FBIN、FBIN)和模擬電源輸入(AVDD)控制。當PWRDWN為高電平時,輸出與CLK在相位和頻率上切換。當PWRDWN為低電平時,所有輸出

2025-09-22 09:59:19 503

503

該CDCVF2510A是一款高性能、低偏斜、低抖動、鎖相環 (PLL) 時鐘驅動器。該CDCVF2510A使用鎖相環 (PLL) 將反饋 (FBOUT) 輸出在頻率和相位上精確對齊到時鐘 (CLK

2025-09-22 09:21:33 359

359

該TLC2932A專為鎖相環(PLL)系統而設計,由壓控振蕩器(VCO)和邊沿觸發型相位頻率檢測器(PFD)組成。VCO的振蕩頻率范圍由外部偏置電阻(R ~偏見~ ).VCO在輸出級有一個1/2

2025-09-19 15:09:18 724

724

該TLC2933A專為鎖相環(PLL)系統設計,由壓控振蕩器(VCO)和邊沿觸發型相位頻率檢測器(PFD)組成。VCO的振蕩頻率范圍由外部偏置電阻(R ~偏見~ ).VCO在輸出級有一個1/2分頻器

2025-09-19 14:50:41 738

738

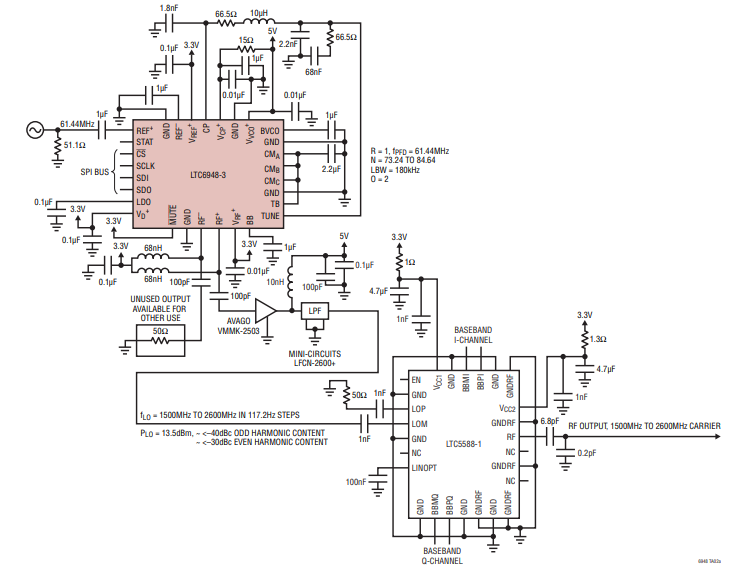

1、2 或 4 選項,以實現更靈活的輸出頻率 范圍。它通過 3 線串行編程接口 (SPI) 接口進行控制。對于電源 敏感應用TRF3761可以通過 SPI 接口或通過外部 chip_en引腳 2。

2025-09-18 10:55:55 1455

1455

時鐘(CK、CK)、反饋時鐘(FBIN、FBIN)、LVCMOS控制引腳(OE、OS)和模擬電源輸入(AV ~DD~ ).當OE為低電平時,除FBOUT/FBOUT外,時鐘輸出被禁用,而內部PLL繼續

2025-09-12 09:52:57 602

602

指定的人對話的“超級耳朵”。SR860則是這個類別中的頂級產品之一。

核心定位:數字鎖相放大器 (DSP Lock-in Amplifier)

SR860的核心功能是從極強的噪聲中提取出極其微弱的信號

2025-09-09 10:00:00

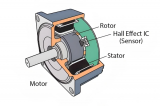

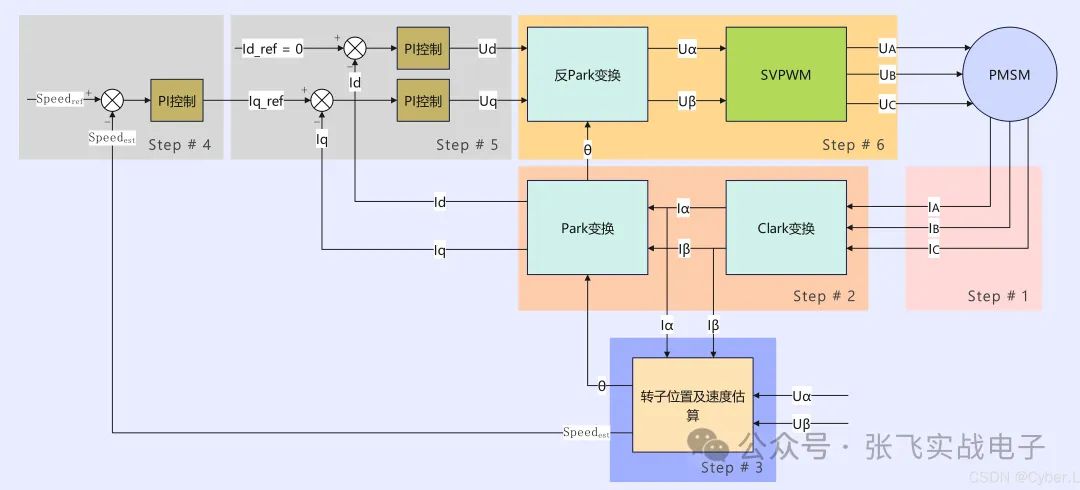

的問題,涵蓋工作原理、特性、采集方法及影響因素等多方面內容。 一、電流環的工作原理與基本構成 電流環本質上是一個反饋控制系統,目標是精確控制電路中的電流。 在電機驅動系統中,電流環負責保障電機以恒定電流運轉,產生穩

2025-09-03 13:39:29 611

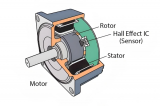

611 在自動駕駛、電動滑板車、無人機甚至工業自動化領域,高性能電機控制是不可或缺的核心技術。而如果你對硬件有足夠的熱情,你會發現:傳統用 MCU 實現 FOC(Field-Oriented Control,磁場定向控制)也能“搬”到 FPGA 上運行,并大大提升實時性和可擴展性。

2025-08-21 15:27:37 5012

5012

統高速并行仿真需求。

? 單模型分割運行: 允許單模型分割 CPU 和 FPGA 中獨立運行,實現電力電子主電路、控制算法和PWM生成模塊的分布式仿真,提升大規模系統測試效率。

▌易用

2025-08-20 18:31:48

Diodes 公司 (Nasdaq:DIOD) 宣布推出AP7372低噪聲低壓差 (LDO) 穩壓器,用于為數據轉換器 (ADC、DAC)、電壓控制振蕩器 (VCO) 和鎖相環 (PLL) 等精密元器件供電。

2025-08-18 09:32:25 892

892 通過FPGA對模數轉換芯片(LTC2308)的采樣控制,實現一個簡易的數字電壓表。

2025-08-16 08:58:07 5307

5307

一直以來,傳統的伺服產品選擇將硬件電流環放在FPGA里,這樣的硬件方案需要消耗MCU更多引腳資源用于和FPGA進行數據傳輸,雙芯片占用板子面積,導致PCB布局布線困難;再者,使用FPGA后也會增加

2025-08-07 15:44:03 4340

4340

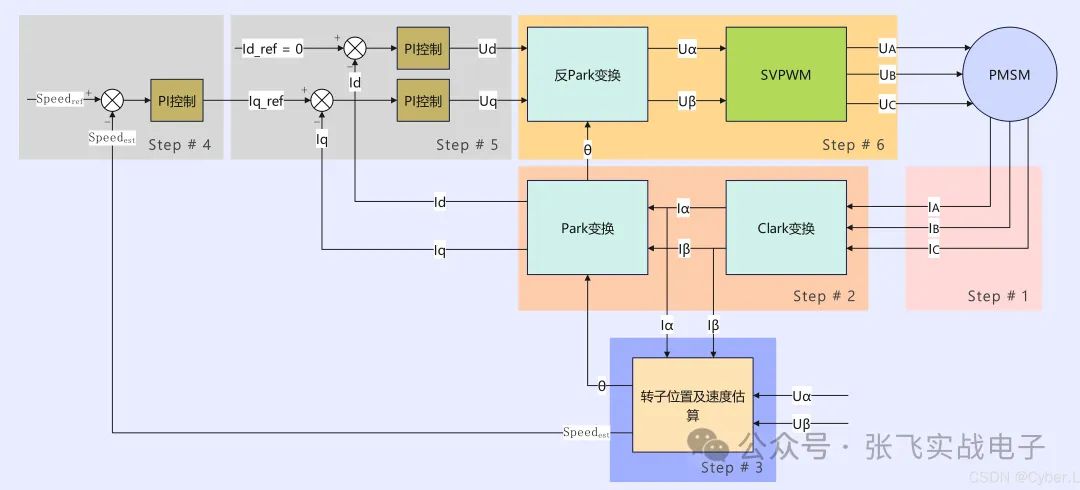

針對無刷直流電機傳統控制的不足,在 STM32 控制框架內設計了無位置傳感器電機矢量控制系統,采用基于鎖相環的滑模觀測器對轉子位置及轉速精確估計并完成電機矢量控制。給出控制系統的總體設計框架及其實現

2025-08-04 14:42:11

使用場合。為實現無軸承同步磁阻電機高速超高速、低成本、實用化運行,提出了一種基于鎖相環法的無速度傳感自檢測技術。通過應用鎖相環原理,設計出無軸承同步磁阻電機無速度傳感器,并基于 Matlab

2025-07-29 16:22:56

、數字識別、HDMI顯示四個主要模塊,成功識別到純底色上的一位數字,并在顯示屏上的數字表中選中該數字,基本實現了本次設計的功能。

2025-07-16 14:28:38 1238

1238

硬件語言編程實現了 PI 調節模塊、過零檢測模塊,脈沖寬度調制發生模塊、換相模塊、啟動模塊等功能,整個控制系統響應速度快、超調小,穩態誤差小,可靠性高、靈活性強,實現了全數字控制,在無位置傳感器直流

2025-07-10 16:35:19

: Window11 PDS2022.2-SP6.4

芯片型號: PG2L50H-484

2.實驗原理

2.1. PLL 介紹

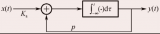

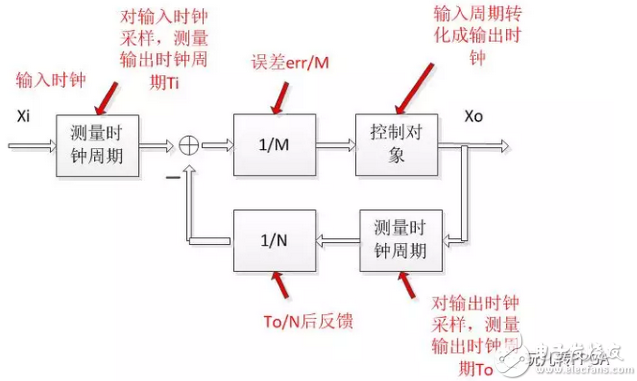

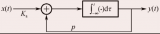

鎖相環作為一種反饋控制電路,其特點是利用外部輸入的參考信號來控制環路內部

2025-07-10 10:28:07

SRAM、ROM等),到大量數模混合 IP(如物理層接口 PHY、鎖相環 PLL 等)——這些模塊經過“K 庫”流程,形成預先定義好、經過參數特征化的標準模塊集合,方可被數字 IC 設計流程所調用。設計師無需從零開始,直接調用這些“積木”,即可高效搭建復雜的電路系統,從而大幅提升設計效率與可靠性。

2025-07-09 10:14:12 2369

2369

,沿任一回路,所有支路電壓的代數和恒等于零。

2、描述反饋電路的概念,列舉他們的應用。

反饋,就是在電子系統中,把輸出回路中的電量輸入到輸入回路中去。

反饋的類型有:電壓串聯負反饋、電流串聯負反饋

2025-06-27 15:05:18

液壓缸上的電液伺服閥。控制上與液壓缸的位移傳感器構成位移閉環,與力傳感器構成力閉環控制:可以實現規則波和階機波的移動控制。

純分享帖,需要者可點擊附件免費獲取完整資料~~~*附件:雙電機驅動數字液壓閥

2025-06-19 10:59:58

品質的因素,包括電流環的動態耦合,速度環的未知擾動等。然后,在介紹擴張狀態觀測器的原理及功能的基礎上,設計了三個擴張狀態觀測器分別估計速度環和電流環的總擾動,進而設計出具有擾動前饋補償和誤差反饋律相結合

2025-06-09 16:11:47

實驗名稱: 鎖相環穩定重復頻率的系統分析 實驗內容: 針對重復頻率的漂移,引入兩套鎖相環系統反饋控制兩個激光器的重復頻率,將其鎖定在同一個穩定的時鐘源上。本章主要闡述了經典鎖相環的原理,穩定重復

2025-06-06 18:36:04 559

559

Analog Devices ADF4382x小數N分頻鎖相環 (PLL) 是一款高性能、超低抖動、小數N分頻鎖相環 (PLL)。它集成了壓控振蕩器 (VCO),是5G或數據轉換器時鐘應用生成

2025-06-04 11:15:21 861

861

鎖相晶體振蕩器(PLDRO)是一種結合了介質振蕩器(DRO)和鎖相環(PLL)技術的先進振蕩器。它在需要高度穩定和精確的微波頻率的應用中廣泛使用,如衛星通信、雷達系統和測試及測量設備。PLDRO

2025-05-30 14:51:29

內容概況:

§1 反饋的概念及判斷

§2 負反饋放大電路的方框圖及放大倍數的估算

§3 交流負反饋對放大電路性能的影響

§4 負反饋放大電路的穩定性

§5 放大電路中反饋的其它

2025-05-29 14:41:51

有規范的,也就是可以百度到,所以高云官網的文檔其實沒有細說,每個FPGA廠家也是通用的。如有迷糊的大家可以在百度上補充一下相關的知識,反正不要被嚇到就好。

接著我們繼續看主程序的代碼,這里有個鎖相環

2025-05-17 20:23:37

,特別是第4章介紹負反饋電路的基本分析方法以及實現穩定放大器的負反饋設計方法。本書也給出了大量的實驗數據和計算機模擬結果,盡可能使所學的知識具體化。

純分享貼,有需要可以直接下載附件獲取完整資料!

(如果內容有幫助可以關注、點贊、評論支持一下哦~)

2025-05-17 17:03:18

晶閘管)設計,并配備了先進的直接轉矩控制(DTC)技術。這些技術為變頻器的穩定運行和精確控制提供了堅實的基礎。 二、同步切換控制原理 同步切換控制的核心在于利用鎖相環(PLL)技術,使變頻器輸出電壓的頻率、幅值和相位與電網電壓保持一致。這樣,在

2025-05-11 16:54:35 902

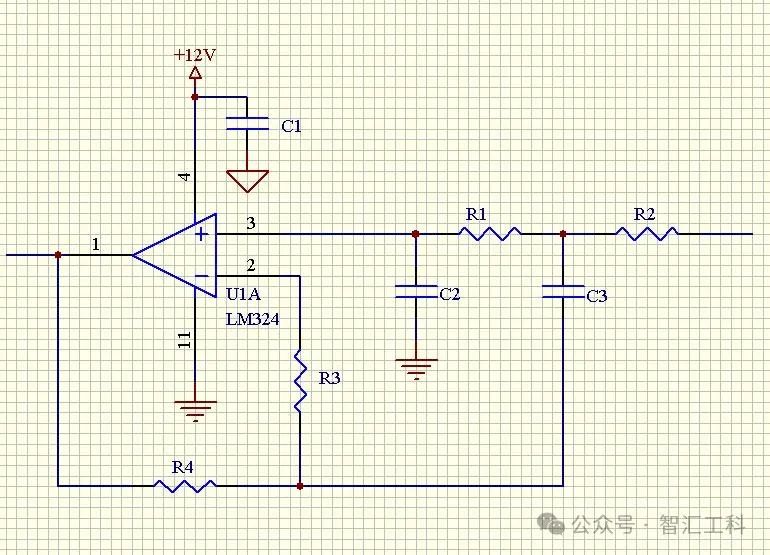

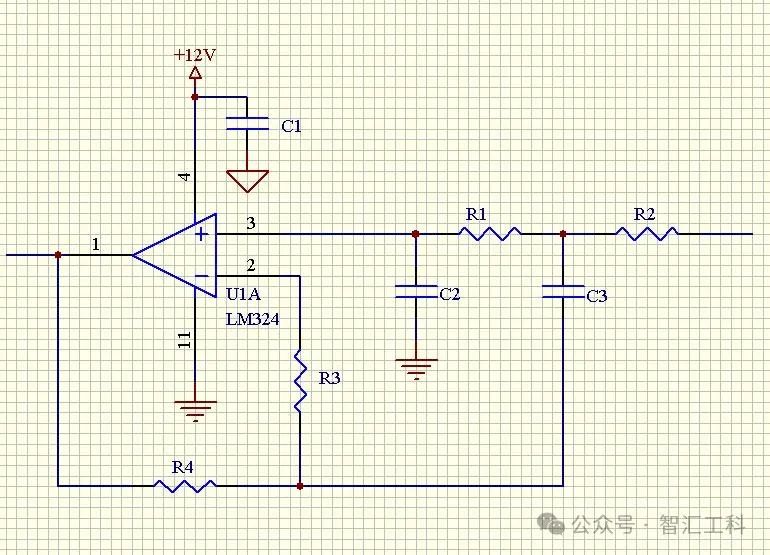

902 1. 理論講解 本文將講述實際環路補償的設計步驟。 對于硬件工程師來說,開關電源和運放的信號處理電路是最常遇到的,都是典型的帶負反饋的閉環控制系統。因此,這兩類電路設計的穩定性和控制理論密切相關

2025-04-28 17:02:43

這是本人經典收藏的電子類書籍,有的是參加設計類大賽時翻閱的參考類文案,有的是參加培訓時藏有的經典教程,在此平臺上分享,希望能夠幫助到有電子興趣好愛的你,請且行且珍惜,好好收藏吧!

2025-04-25 17:05:15

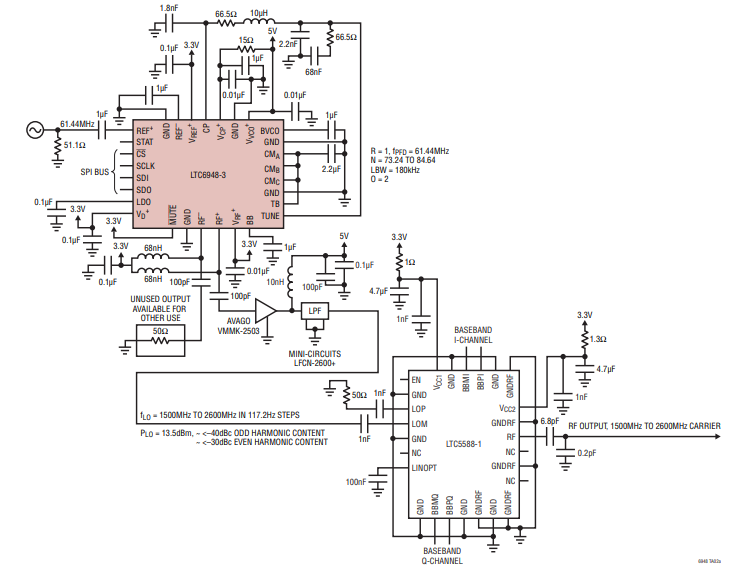

LTC6948 是一款具全集成型 VCO 的高性能、低噪聲、6.39GHz 鎖相環 (PLL),其包括一個基準分頻器、相位-頻率檢測器 (PFD)、超低噪聲充電泵、分數反饋分頻器和 VCO 輸出分頻器。

2025-04-25 14:08:33 723

723

,要求實現電流——電壓信號的轉換時,應在放大電路中引入電壓并聯負反饋等。

純分享貼,有需要可以直接下載附件獲取文檔!

(如果內容有幫助可以關注、點贊、評論支持一下哦~)

2025-04-25 13:29:21

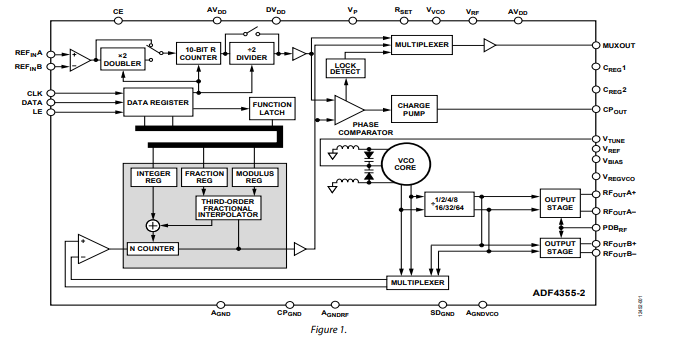

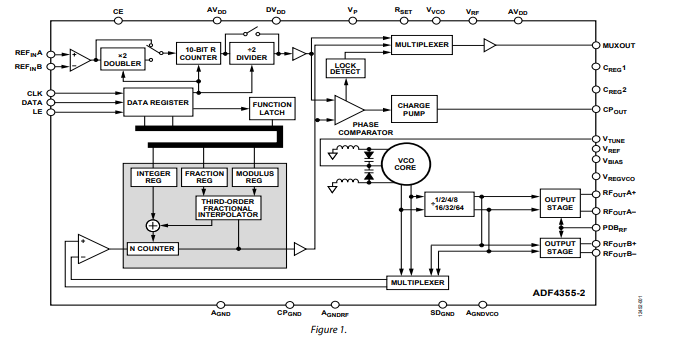

ADF4355-2結合外部環路濾波器和外部參考頻率使用時,可實現小數N分頻或整數N分頻鎖相環(PLL)頻率合成器。 一系列分頻器可實現54 MHz至4400 MHz的工作頻率。

2025-04-25 11:42:53 914

914

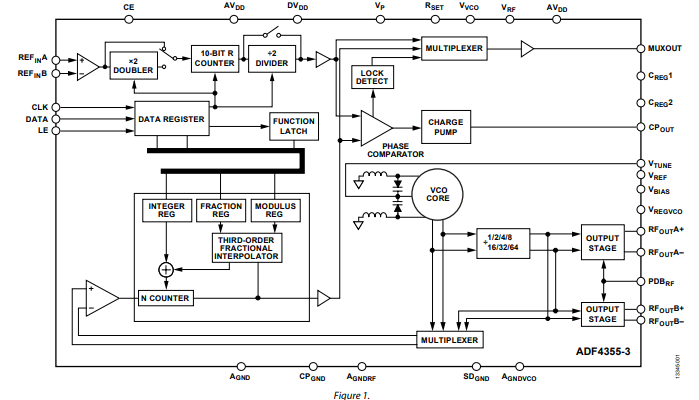

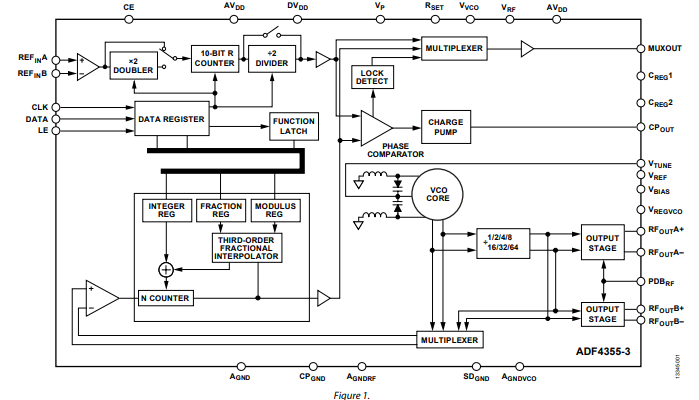

ADF4355-3結合外部環路濾波器和外部參考頻率使用時,可實現小數N分頻或整數N分頻鎖相環(PLL)頻率合成器。 其他頻率輸出的一系列分頻器可實現51.5625 MHz至6600 MHz的工作頻率。

2025-04-25 11:06:46 848

848

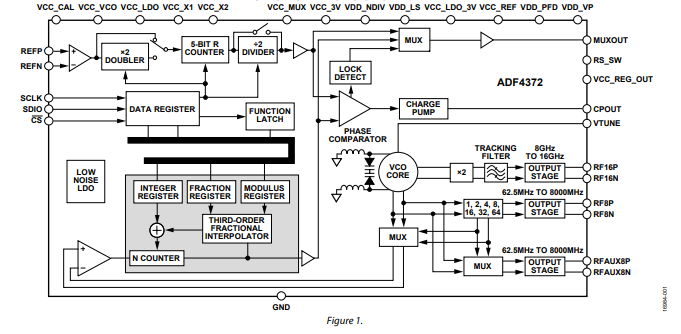

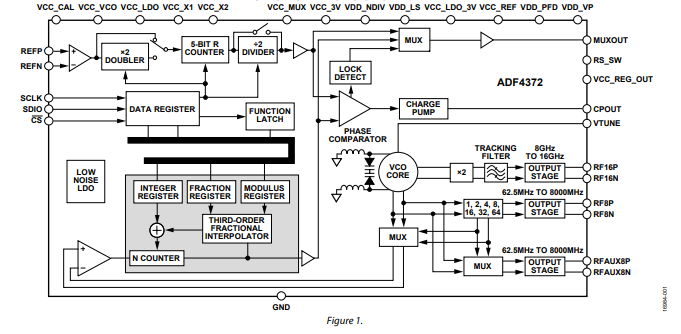

ADF4372 結合外部環路濾波器和外部基準頻率使用時,可實現小數 N 分頻或整數 N 分頻鎖相環 (PLL) 頻率合成器。寬帶微波壓控振蕩器 (VCO) 設計允許產生 62.5 MHz 至 16 GHz 的頻率。

2025-04-25 09:57:01 1058

1058

摘要本題目中,振蕩器采用輸出波形好,頻率穩定度高的具有波段切換功能的改進型電容三點式振蕩電路。在每一個波段內,頻率的調節是通過改變壓控振蕩器的變容二極管的直流反壓實現的。采用鎖相環頻率合成電路,以

2025-04-22 14:54:08

內容介紹本文檔主要介紹鎖相環(PLL)電路的設計與應用,內容包括PLL工作原理與電路構成、PLL電路的傳輸特性、PLL電路中環路濾波器的設計方法、PLL電路的測試與評價方法、PLL特性改善技術

2025-04-18 15:34:51

問題。第三部分(第9-13章)著重介紹面向各種應用的電路設計方法,包括非線性電路、信號發生器、電壓基準和穩壓電源、D-A和A-D轉換器以及非線性放大器和鎖相環等。可用作通信類、控制類、遙測遙控、儀器儀表等相關

2025-04-16 14:34:16

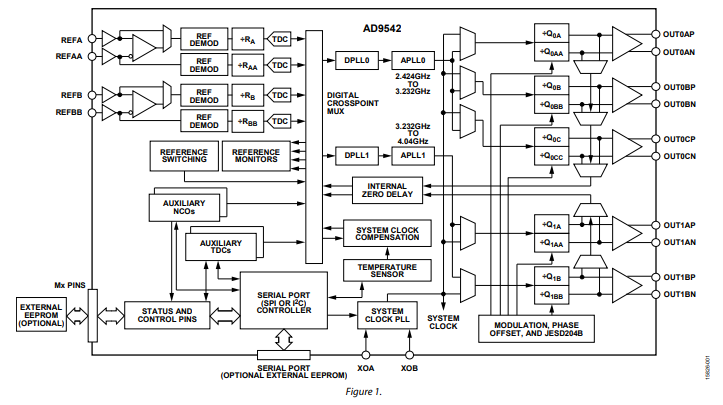

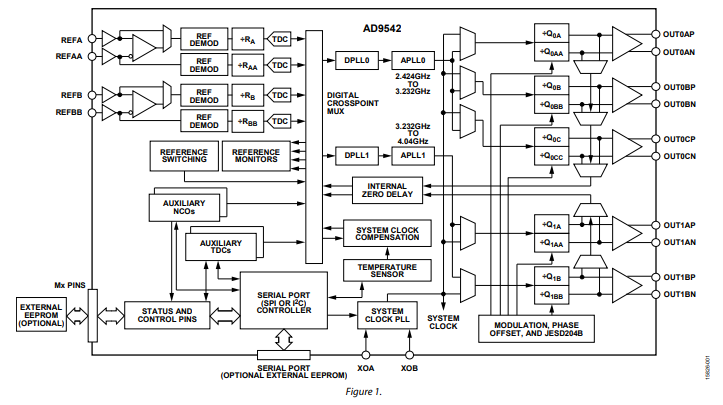

AD9542的10個時鐘輸出與最多四個輸入基準電壓源之一同步。數字鎖相環(DPLL)可減少與外部基準電壓源相關的時序抖動。借助數字控制環路和保持電路,即使所有參考輸入都失效,也能持續產生低抖動輸出信號。

2025-04-16 10:58:58 871

871

相電流檢測及重構(單電阻、雙電阻及三電阻采樣)6.轉子位置及速度提取(滑膜觀測器、低通濾波器、鎖相環)7.PMSM無感控制的啟動計劃寫完上述內容后再開始寫一些別的控制

2025-04-15 19:33:08 3164

3164

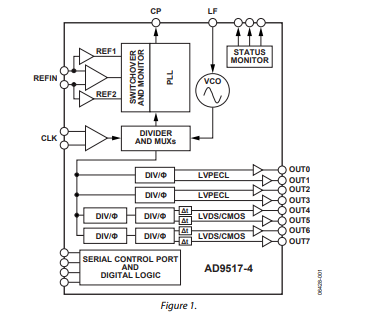

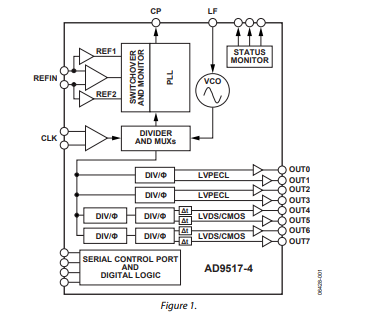

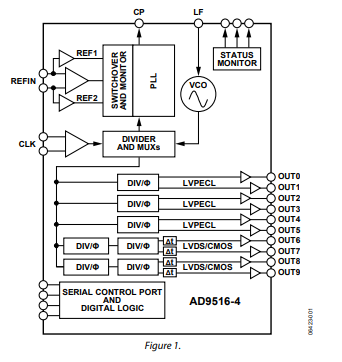

AD9517-4提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為1.45 GHz至1.80 GHz。也可以使用高達2.4 GHz的外部VCO/VCXO。

2025-04-14 10:10:38 953

953

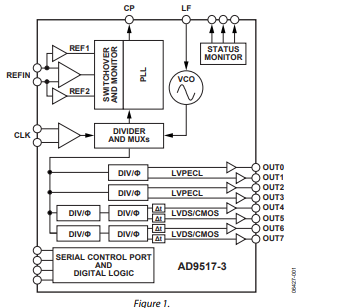

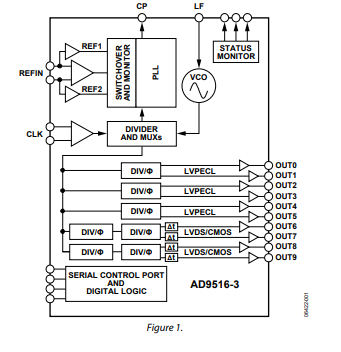

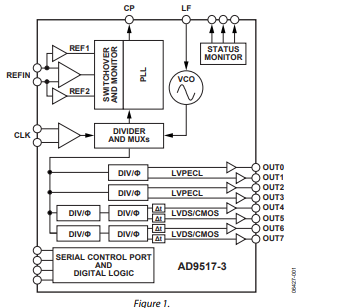

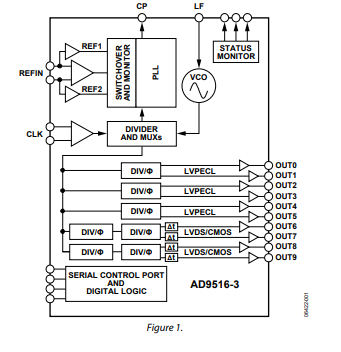

AD9517-3提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為1.75 GHz至2.25 GHz。也可以使用高達2.4 GHz的外部VCO/VCXO。

2025-04-14 10:04:19 922

922

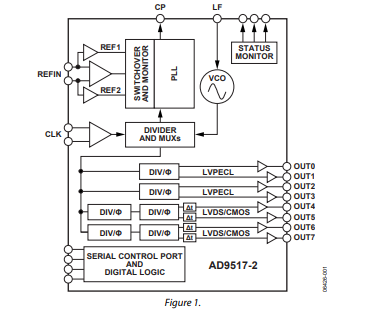

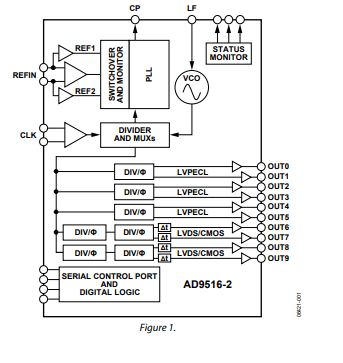

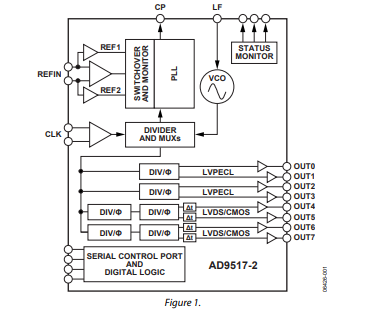

AD9517-2提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為2.05 GHz至2.33 GHz。也可以使用高達2.4 GHz的外部VCO/VCXO。

2025-04-14 09:53:49 848

848

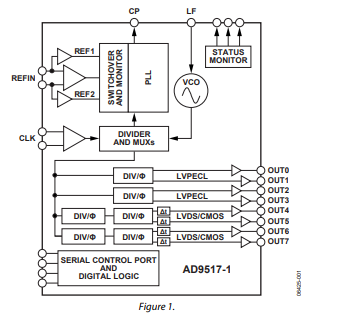

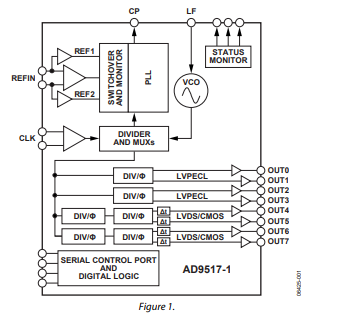

AD9517-1提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為2.30 GHz至2.65 GHz。也可以使用高達2.4 GHz的外部VCO/VCXO。

2025-04-14 09:41:50 852

852

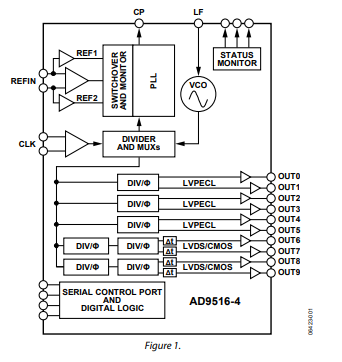

AD9516-4*提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為1.45 GHz至1.80 GHz。也可以使用最高2.4 GHz的外部VCO/VCXO。

2025-04-11 16:36:38 1017

1017

AD9516-3提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為1.75 GHz至2.25 GHz。也可以使用最高2.4 GHz的外部VCO/VCXO。

2025-04-11 16:29:24 1046

1046

AD9516-2提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為2.05 GHz至2.33 GHz。也可以使用最高2.4 GHz的外部VCO/VCXO。

2025-04-11 16:18:10 1056

1056

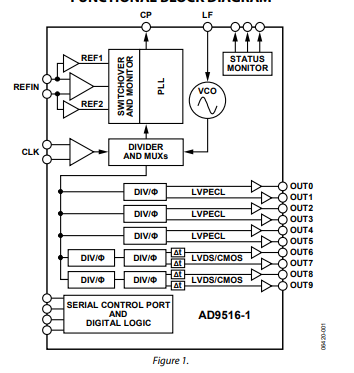

AD9516-1提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,還配有片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為2.30 GHz至2.65 GHz。或者,也可以使用最高2.4 GHz的外部VCO/VCXO。

2025-04-11 16:11:24 1095

1095

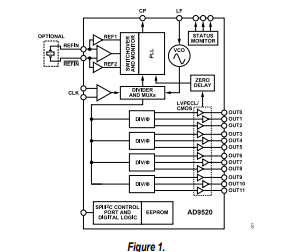

AD9520-4提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為1.4 GHz至1.8 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 15:38:15 688

688

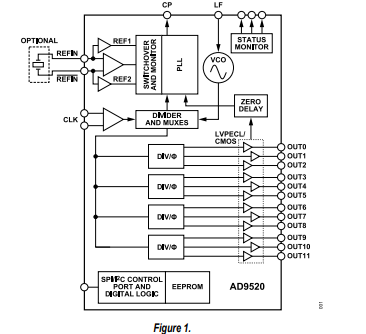

AD9520-3提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為1.72 GHz至2.25 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 15:29:51 807

807

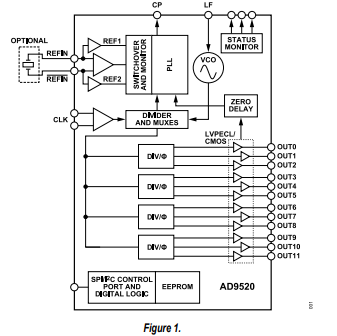

AD9520-2提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為2.02 GHz至2.335 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 14:38:24 768

768

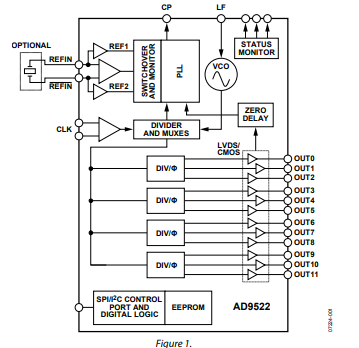

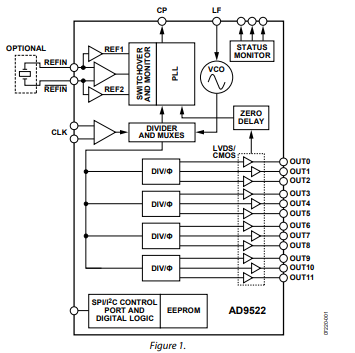

AD9522-4提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為1.4 GHz至1.8 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 14:14:08 822

822

AD9522-3提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為1.72 GHz至2.25 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 11:50:33 733

733

AD9522-1提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為2.27 GHz至2.65 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 11:34:42 770

770

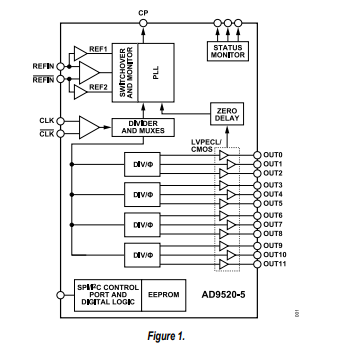

AD9520-5提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL),可以配合外部VCO使用。

2025-04-11 11:17:07 720

720

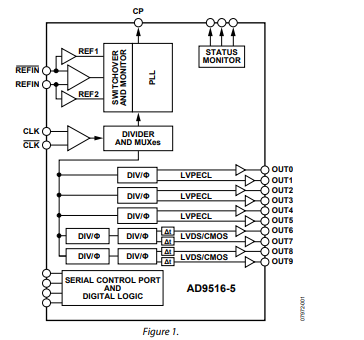

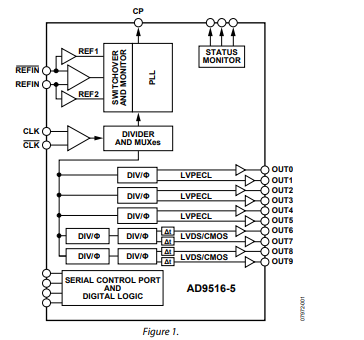

AD9516-5提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL),可以配合外部VCO/VCXO使用。

2025-04-11 11:00:50 719

719

AD9547針對許多系統提供同步功能,包括同步光纖網絡(SONET/SDH)。該器件產生的輸出時鐘可以與兩路差分或四路單端外部輸入參考時鐘之一同步。數字鎖相環(PLL)可以降低與外部參考時鐘

2025-04-11 09:37:58 757

757

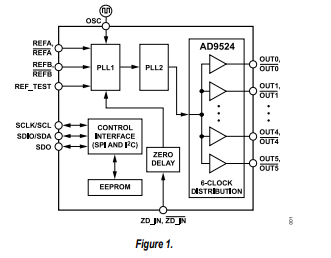

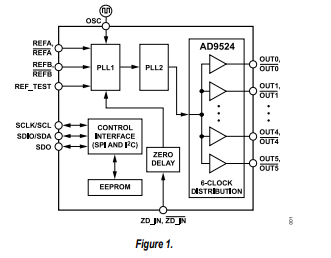

AD9524提供低功耗、多路輸出時鐘分配功能,具有低抖動性能,還配有片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為3.6 GHz至4.0 GHz。

2025-04-10 15:57:05 714

714

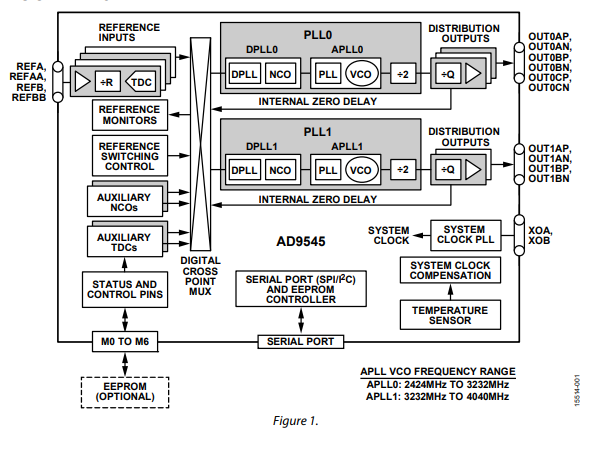

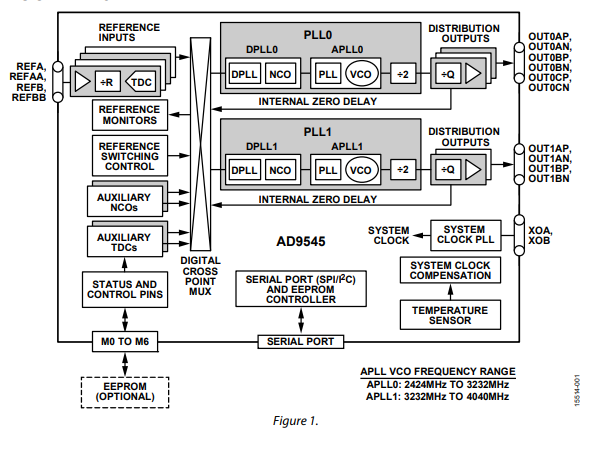

AD9545 支持針對在服務提供商包交換網絡上提供頻率、相位和當日時間的現有和新興 ITU 標準。

將 AD9545 的 10 個時鐘輸出同步為多達四個輸入基準電壓源中的任意一個。數字鎖相環

2025-04-09 18:04:59 1100

1100

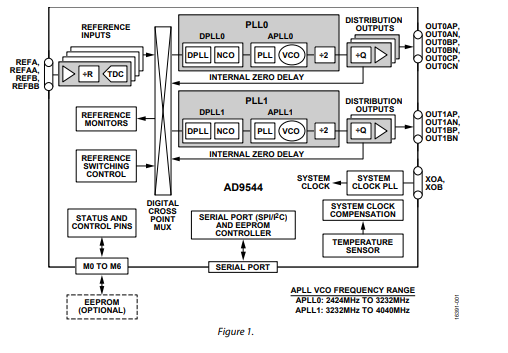

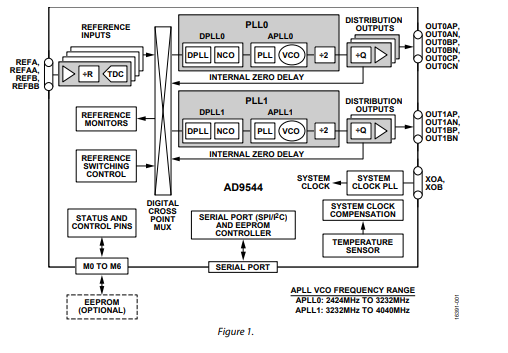

AD9544的10個時鐘輸出與最多四個輸入基準電壓源之一同步。數字鎖相環(DPLL)可減少與外部基準電壓源相關的時序抖動。借助數字控制環路和保持電路,即使所有參考輸入都失效,也能持續產生低抖動輸出信號。

2025-04-09 17:48:46 1083

1083

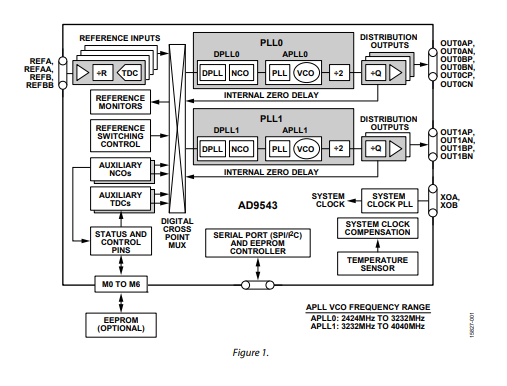

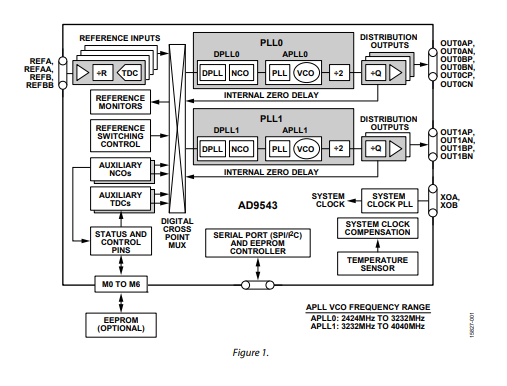

AD9543支持現有和新興的ITU標準,可通過服務提供商分包網絡傳輸頻率、相位和當前時間。

AD9543的10個時鐘輸出與最多四個輸入基準電壓源之一同步。數字鎖相環(DPLL)可減少與外部基準電壓源相關的時序抖動。借助數字控制環路和保持電路,即使所有參考輸入都失效,也能持續產生低抖動輸出信號。

2025-04-09 17:35:04 1053

1053

~

01、數字信號處理的FPGA實現

旨在講解前端數字信號處理算法的高效實現。首先概述了當前的FPGA技術、器件以及用于設計最先進DSP系統的工具。闡述了計算機算法的概念、理論、FIR和IIR濾波器

2025-04-07 16:41:58

CS5228替代AG7120HDMI線纜延長方案包含 TypeC雙模式 DP 線纜適配器寄存器,可用于識別線纜適配器的性能。抖動清理 PLL(鎖相環)能夠消除輸入抖動,并完全重置系統抖動容限,因此能

2025-04-02 10:54:38

反饋的概念及判斷,負反饋放大電路的方框圖及放大倍數的估算,交流負反饋對放大電路性能的影響,負反饋放大電路的穩定性,放大電路中反饋的其它問題

2025-04-01 10:29:41

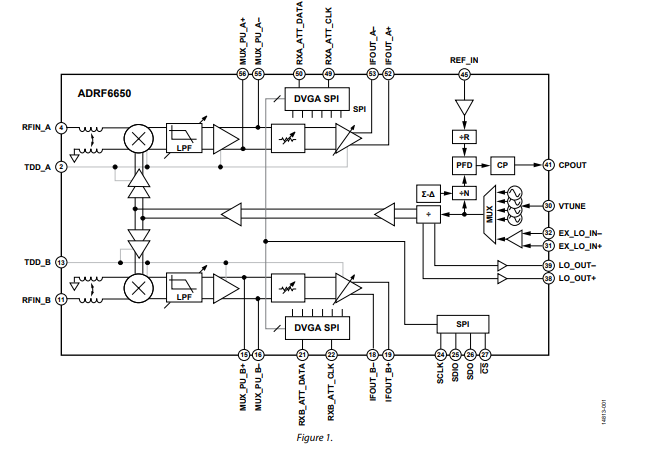

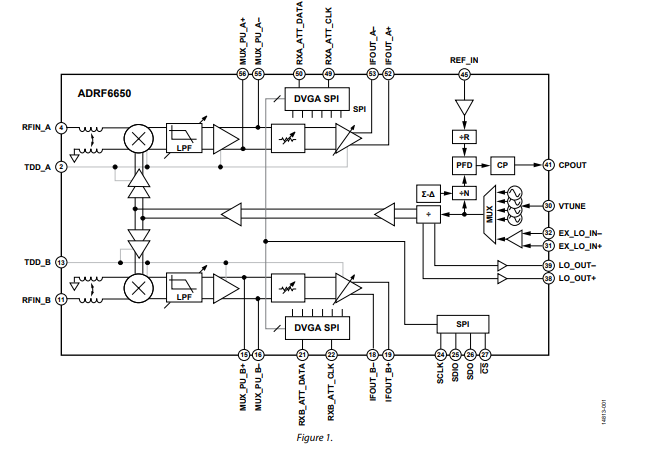

ADRF6650是一款高度集成的下變頻器,集成了雙混頻器、雙數字交換衰減器、雙數字可變增益放大器、鎖相環(PLL)和壓控振蕩器(VCO)。此外,ADRF6650還集成了兩個射頻(RF)巴倫、串行增益控制(SGC)控制器和快速啟用輸入以實現分時雙工(TDD)運行。

2025-03-26 10:56:55 921

921

的單閉環調速系統可以實現無靜差調速。但電機在啟動過程中,為了實現最快啟動,需要電流迅速達到最大值并且在一定時間內保持恒定,而主電路中存在的電感使得電流不能發生突變,因此,可以采用電流負反饋控制來實現這一

2025-03-21 17:32:55

控 制電機轉速來完成的,因而調速系統是其最核心的控制 系 統 \" 。在電機的速度達到穩態的情況下,轉速負反饋和PI調節器的單閉環調速系統可以實現無靜差調速。但電機在啟動過程中,為了實現最快

2025-03-20 13:03:04

電樞電流構成電流環。軟件編程實現改進的轉速、電流雙閉環PI控 制器,利用單片機的定時器生成占空比可調的PWM信號,光耦隔離后經功率驅動放大,通過 控制H橋驅動電路對直流電機進行無級平滑調速。實驗表明該系統控制精度高,可靠性和穩定 性加強。

全文點擊下方附件查看*附件:直流電機雙閉環數字調速系統設計與實現.pdf

2025-03-20 12:55:42

鎖相介質振蕩器(點頻源)簡介盛鉑科技PDROUxxxx系列超低相位噪聲鎖相介質振蕩器可實現在1GHz至44GHz范圍內基于參考頻率整數倍的任意固定頻率高質量信號輸出。PRDOUxxxx系列通過雙環

2025-03-13 11:35:08

負反饋環是所有線性電源和開關電源的核心部分,它使電源的輸出電壓保持恒定。為了實現這一功能,采用誤差放大器來減小輸出電壓與理想參考電壓的誤差。從理論上講,采用極高增益的反相放大器就行了。但實際上

2025-03-11 14:40:08

基于不同的標準和電路特性進行分類,以下是幾種主要的類型: 1. 按照反饋極性分類: ● 正反饋:輸出信號增強了輸入信號,導致凈輸入信號增加。這種反饋常用于振蕩器和某些放大電路中。 ● 負反饋:輸出信號削弱了輸入信號,使凈

2025-03-05 12:07:38 2664

2664

技術的革新潮流。 精準定位,奠定高效生產基石 磁環編碼器通過內置的磁感應元件與精密的信號處理電路,能夠實現對旋轉軸位置的實時監測與精準反饋。無論是高速運轉的機械臂,還是精密裝配線上的旋轉平臺,磁環編碼器都能

2025-02-28 08:54:34 1002

1002 路LVDS差分時鐘信號。本器件片內集成鎖相環模塊,鎖相環輸入頻率范圍20MHz~135MHz。I/O電壓支持1.8V/3.3V,core電壓為1.8V/3.3V的

2025-02-17 14:03:13

1.放大電路負反饋特性總結? 2.放大電路負反饋電路種類? 3.放大電路對電路放大倍數及穩定性影響? 4. 放大電路對電路波形及帶寬影響? 5. 放大電路對電路輸入電阻的影響? 6. 放大電路對電路輸出電阻的影響 ?

2025-02-11 10:05:19 969

969

的參考信號。測試設備:用于頻率測量和信號源。深圳市立維創展科技是Synergy的經銷商,主要提供Synergy微波壓控振蕩器、晶體振蕩器、鎖相振蕩器、鎖相環頻率合成器、混頻器等產品,產品位于美國北部的直接

2025-02-11 09:29:16

tlk2711發送端出來的眼圖較差,tlk2711接收端的鎖相環不能鎖定,我們在示波器上觀察恢復時鐘老是調相,如何解決?

2025-02-06 07:06:50

特定的路徑送回到輸入端的過程。依據反饋信號對輸入信號的影響,可分為正反饋和負反饋兩大類型。 正反饋,顧名思義,是指反饋信號與輸入信號相加后,使得輸入信號得到增強。這種反饋機制能夠促使電路輸出迅速增大,在一些

2025-02-04 14:32:00 1719

1719 鎖相環(Phase-Locked Loop,簡稱PLL)是一種廣泛應用于電子系統中的反饋控制系統,主要用于頻率合成和相位同步。本文將從鎖相環的工作原理、基本組成、應用案例以及設計考慮等方面進行詳細闡述,以幫助讀者全面理解這一重要技術。

2025-02-03 17:48:00 2317

2317 和 1.5MHz;-上行端口內置1.5K上拉電阻和下行端口內置15K下拉電阻;-片內集成5V、3.3V、1.8V電壓調整器;-內置12MHz晶振啟動電阻和電容;-40倍頻到480MHz的PLL鎖相環電路;-可以通過外置EEPROM控制VID、PID等設置;-SSOP-28無鉛封裝。管腳配置

功能框圖

2025-01-24 12:16:06

在生物體和工程系統中,反饋調節是一種普遍存在的控制機制,它通過監測系統的狀態并作出相應的調整來維持系統的穩定性或實現特定的功能。正反饋調節和負反饋調節是兩種基本的反饋類型,它們在行為和效果上有著本質

2025-01-18 09:47:36 9557

9557 電子發燒友網站提供《使用獨立于內核的外設實現降壓轉換器設計和反饋控制器.pdf》資料免費下載

2025-01-15 15:31:16 0

0 一.依據模擬環設計數字環 根據信號與系統的分析理論,一個系統完全由系統函數來確定,因此我們可從系統函數的角度出發,找到模擬電路與數字電路的轉換關系,最終根據環路濾波器的數字域系統函數進行數字

2025-01-14 11:14:00 1130

1130

電子發燒友網站提供《AN-1420:利用數字鎖相環(DPLL)實現相位增建和無中斷切換.pdf》資料免費下載

2025-01-13 14:07:28 0

0 管理:集成數字時鐘管理器 (DCM)、鎖相環 (PLL) 時鐘發生器和高級配置選項。 連接選項:兼容 PCI Express? 的集成端

2025-01-11 10:01:05 841

841 鎖相環(Phase-LockedLoop,PLL)是一個能夠比較輸出與輸)入相位差的反饋系統,利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位,使振蕩信號同步至參考信號。而鎖相環

2025-01-08 17:39:41 1053

1053

電子發燒友網站提供《基于鎖相環法的載波提取方案.pdf》資料免費下載

2025-01-07 14:41:16 2

2 ,基于相電壓采樣的鎖相控制比較容易受干擾,以及電網不平衡時容易影響系統穩定性,提出基于線電壓采樣的鎖相環以及相應的并網電流正負序分離控制策略。

2025-01-06 08:47:12 1734

1734

電子發燒友App

電子發燒友App

評論