前言

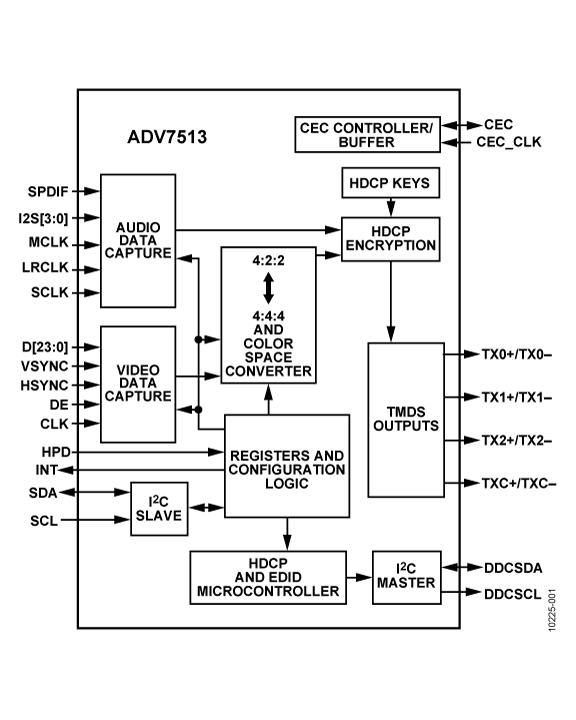

HDMI接口顯示使用DMT時序+TMDS編碼來實現。當用FPGA控制HDMI的數據傳輸時,通常可以采用純RTL實現TMDS算法或者使用專門的HDMI芯片(如ADV7513)這兩種方案來完成。本文主要是介紹如何用FPGA控制ADV7513實現HDMI畫面顯示和音頻播放。

顯示器時序(DMT)標準介紹

DMT(Display Monitor Timing)是由VESA(視頻電子標準協會)制定的顯示器時序標準,用于定義計算機顯示器的視頻信號參數。是現代數字顯示設備的核心規范。開發人員應遵循DMT標準使自己的設計成為符合行業標準的產品。

在深入了解DMT時序之前,首先需要掌握一些與圖像相關的基本概念,如像素、分辨率、刷新率、像素時鐘等。

1 圖像相關的幾個基本概念

像素(Pixel):是“圖像元素”(Picture Element)的縮寫,是構成數字圖像(如照片、屏幕顯示內容等)的基本單位。可以將其理解為數字圖像中的 “最小點”,一張圖像由無數個像素按照一定規律排列組成。

分辨率:指圖像的像素總量,通常以“寬度 × 高度” 的形式表示(單位為像素)。例如:一張分辨率為 640×480 的圖片,意味著橫向有 640 個像素,縱向有 480 個像素,總像素數307200個。常見的圖像分辨率還包括 2560×1440(2K)、3840×2160(4K)等。

刷新率:刷新率是描述顯示器每秒刷新畫面次數的指標,單位為“赫茲(Hz)”。刷新率數值越高,動態畫面越流暢,但需內容和硬件共同支持。選擇時需平衡流暢需求、設備性能和功耗,例如日常使用 60Hz 足夠,游戲或高頻操作場景則可優先考慮 90Hz 及以上刷新率。

像素時鐘(Pixel Clock):簡稱PCLK,是數字視頻系統中用于同步像素數據傳輸的時鐘信號。根據行同步時序以及場同步時序可以計算得到像素的時鐘=水平總像素*垂直總行數*60, 比如640*480@60分辨率的像素時鐘是:800 * 525 * 60 = 25.2MHz

2 顯示器時序介紹

如下是DMT時序,代表顯示一整幀的傳輸時序:

在顯示器時序中,sync(同步)、porch(消隱間隔)、和 border(邊框)是用于控制顯示器如何逐行和逐幀繪制圖像的關鍵參數。這些參數一起定義了每一行和每一幀圖像的精確時序。

sync(同步):同步信號分行同步(HSYNC)脈沖和場同步(VSYNC)脈沖。

HSYNC用于控制每一行像素的開始和結束。它告訴顯示器何時開始繪制新的一行。每當一行像素繪制完成時,HSYNC信號會產生一個脈沖,提示顯示器移動到下一行。

VSYNC用于控制一幀圖像的開始和結束。當所有行的像素都繪制完畢時,VSYNC信號產生一個脈沖,提示顯示器返回到屏幕頂部,準備繪制下一幀。

porch(消隱間隔):在傳統的CRT顯示器的掃描過程中,掃描總是從顯示器的左上角開始,水平向前行進,同時掃描點也以較慢的速率向下移動。當掃描點到達顯示器右側邊緣時,掃描點快速返回左側,重新開始在第1行的起點下面進行第2行掃描。當掃描完顯示器上所有的行,就形成一幀,然后電子束要從顯示器的右下角返回到顯示器的左上角,開始新一幀的掃描。

電子束在行與行之間的返回過程以及在幀與幀之間的返回過程(從右下角返回到顯示器的左上角)都稱之為逆程,掃描正程期間傳送圖像信號,逆程期間不傳送圖像信號。電子束逆程掃描在熒光屏上出現回掃線,將對正程的圖像造成干擾,影響圖像的清晰度。因此需使顯示器在行、場掃描逆程期間電子束截止,以消除行、場逆程回掃線,即實現消隱。消隱分為前消隱間隔和后消隱間隔。

前消隱間隔(Front Porch):有效視頻之后,同步脈沖之前,為同步脈沖的清晰識別提供保障,是行/幀結束的“預告”。

后消隱間隔(Back Porch):同步脈沖之后,有效視頻之前,提供電路穩定時間,確保準確開始繪制像素。

注:消隱間隔在CRT顯示器(陰極射線管顯示器)中起到了重要作用,目前為了兼容性和穩定性,消隱間隔在LCD等現代顯示器中仍然保留。

border(邊框):通常就是指屏幕四周的黑邊。在顯示器的時序中,border(邊框)區域定義了可見圖像之外的部分,通常會顯示為屏幕四周的黑邊。這些黑邊在現代顯示器上通常是不可見的,或者僅在特定情況下才會出現,例如在分辨率與顯示器實際尺寸不匹配時。邊框是圖像周圍的不可見區域,通常用于在屏幕的可見顯示區域和消隱間隔之間提供一個緩沖區。邊框區域不顯示圖像數據,但它在時序中占有一定的時間,以確保圖像的穩定性和完整性。避免因顯示器電路

處理時間不足而導致的圖像抖動、扭曲或閃爍。

Addressable video:位于中間的區域就是我們通常稱為的可顯示圖像區域,也就是分辨率實際描述的區域。這是屏幕上實際用于顯示圖像內容的部分。

Polarity(極性):是指同步信號(包括水平同步信號HSYNC和垂直同步信號VSYNC)的信號電平方向,通常標記為正極性(Positive Polarity)或負極性(Negative Polarity)。為了確保不同硬件、軟件和標準之間的無縫協作,同步信號的極性有四種可選:

1. 行、場同步信號正極性:

2. 行同步信號正極性、場同步信號負極性:

3. 行、場同步信號負極性:

4. 行同步信號負極性、場同步信號正極性:

本教程選擇的是行、場同步信號負極性。

3 顯示器時序中不同分辨率刷新率的參數

不同分辨率的時序參數各不相同。我們可以通過查閱DMT 文檔(下載地址https://vesa.org/vesa-standards/)來獲取這些信息。這里以640*480@60為例教大家如何查看相關參數。

從上圖可以分析出行信號的參數(P,像素):

以及場信號的參數(L,行):

不過在實際設計當中一般將H Back Porch和H Left Border合并當作顯示后沿(或者稱之為行后肩),H Right Border和H Front Porch合并當作顯示前沿(或者稱之為行前肩)。V Back Porc和V Left Border合并當作場顯示后沿(或者稱之為場后肩),V Right Border和V Front Porch合并當作場顯示前沿(或者稱之為場前肩)。

其他常見分辨率的參數查詢以此類推,合并后的參數如下表格:

-

FPGA

+關注

關注

1656文章

22317瀏覽量

631097 -

顯示器

+關注

關注

22文章

5133瀏覽量

143801 -

HDMI

+關注

關注

34文章

1876瀏覽量

158993 -

音頻信號

+關注

關注

9文章

278瀏覽量

34807 -

時序

+關注

關注

5文章

403瀏覽量

38661

原文標題:1-DE10-Nano的HDMI方塊移動案例——顯示器時序(DMT)標準介紹

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

ADV7513芯片是否支持DE模式的RGB輸入,是否可以在內部產生Hsync和Vsync信號呢?

HDMI TX 發送器

ADV7513是HDMI發送器,是AD9889的升級版本

例說FPGA連載89:多分辨率HDMI顯示驅動設計之功能概述

請問為什么在使用ADV7513的時候讀出寄存器的數值都是0xff呢?

ADV7513具有哪些特性參數應用?

為什么我在使用ADV7513的時候讀出寄存器的數值都是0xff呢?

ADV7513 165 MHz高性能HDMI發送器

高性能HDMI發送器ADV7513的主要特性及應用電路

AN-1270: 基于ADV7511/ADV7511W/ADV7513的視頻發生器

如何用FPGA控制ADV7513實現HDMI畫面顯示和音頻播放

如何用FPGA控制ADV7513實現HDMI畫面顯示和音頻播放

評論