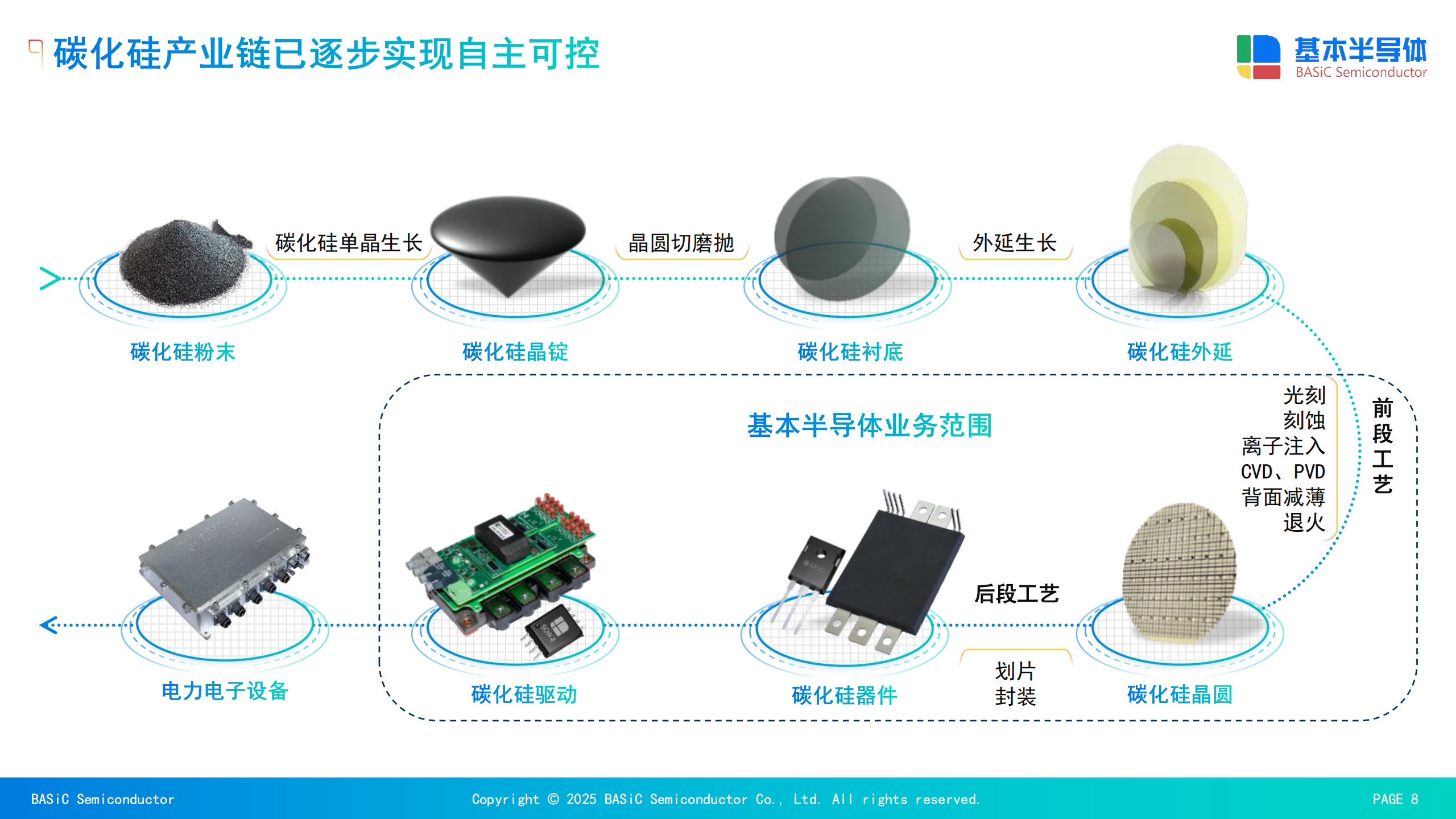

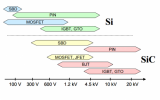

碳化硅器件正在幾個(gè)大容量功率應(yīng)用中取代其現(xiàn)有的硅對(duì)應(yīng)物。隨著 SiC 市場(chǎng)份額的持續(xù)增長(zhǎng),該行業(yè)正在消除大規(guī)模商業(yè)化的最后一道障礙,包括高于 Si 器件的成本、相對(duì)缺乏晶圓平面度、存在基面位錯(cuò)、可靠性和耐用性問(wèn)題以及需要對(duì)于熟練掌握 SiC 功率技術(shù)的勞動(dòng)力,以跟上不斷增長(zhǎng)的需求。為了實(shí)現(xiàn)具有成本效益的 SiC 制造,需要高產(chǎn)量的制造工藝。在我的 PowerUP 演講中,我將總結(jié) SiC 制造技術(shù)的關(guān)鍵方面,并概述非 CMOS 兼容工藝,這些工藝已經(jīng)過(guò)簡(jiǎn)化,可以在傳統(tǒng)成熟的 Si 晶圓廠中大規(guī)模制造 SiC 器件。

碳化硅晶片

如今,SiC 晶圓占 SiC 器件總成本的 55% 至 70%,這是其獨(dú)特復(fù)雜的制造細(xì)節(jié)的結(jié)果。傳統(tǒng)的 SiC 襯底主要通過(guò)種子升華技術(shù)在約 2,500?C 的溫度下生長(zhǎng),這帶來(lái)了工藝控制挑戰(zhàn)。晶體膨脹是有限的,需要使用大的、高質(zhì)量的晶種,升華生長(zhǎng)速度可能相對(duì)較低,大約為 0.5-2 毫米/小時(shí)。位錯(cuò)通過(guò)晶錠傳播并存在于器件晶片中。此外,與金剛石相當(dāng)?shù)?SiC 材料的硬度使得 SiC 襯底的鋸切和拋光相對(duì)于 Si 而言速度較慢且成本較高。

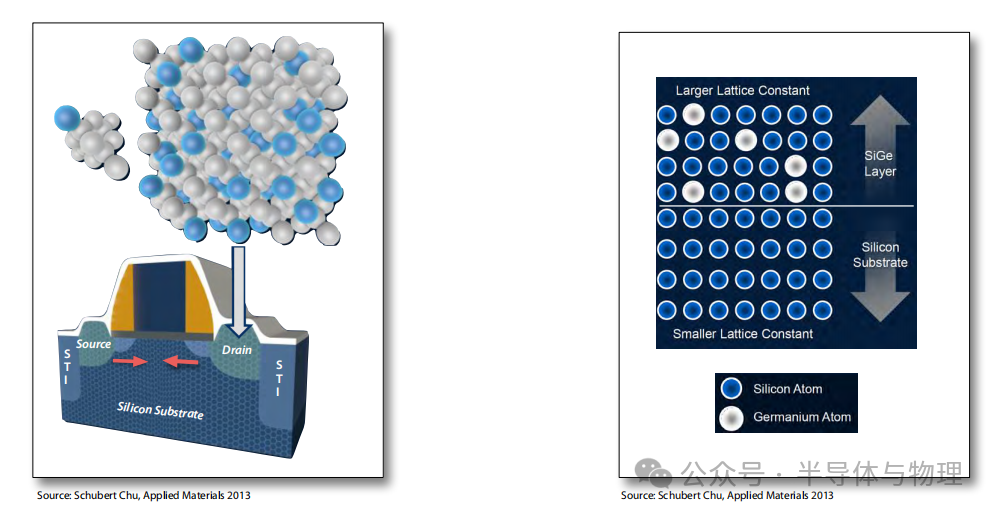

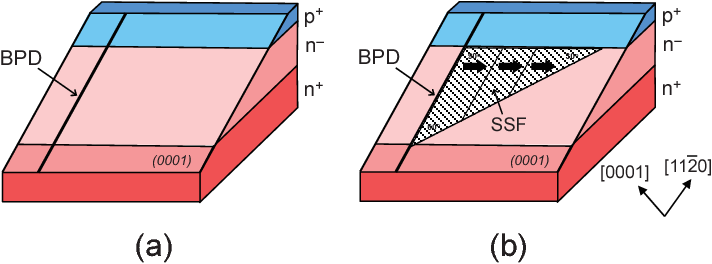

制造 SiC 器件的外延層是通過(guò)化學(xué)氣相沉積在 1,500°C 至 1,650°C 的水平或行星反應(yīng)器中生長(zhǎng)的。壓力通常在 30 到 90 托之間,生長(zhǎng)速率可高達(dá) 46 毫米/小時(shí)。外延生長(zhǎng)在 4? 切邊襯底上進(jìn)行,以保持襯底的多型穩(wěn)定性。外延的目標(biāo)是盡量減少缺陷的產(chǎn)生,限制從襯底到外延的“性能退化”缺陷傳播,并確保從襯底傳播到外延的性能退化缺陷轉(zhuǎn)化為良性缺陷。由于 SiC 晶圓中的缺陷限制了大面積器件的良率,并且許多器件在模塊中并聯(lián)以增加電流輸出,因此非常需要緊密的外延摻雜和厚度均勻性,特別是隨著晶圓尺寸的增加。

總體而言,SiC 晶圓的合成比硅更復(fù)雜、更慢。結(jié)果是更昂貴的晶圓和最終更高的設(shè)備成本。當(dāng)今 SiC 行業(yè)發(fā)生的垂直整合的一個(gè)關(guān)鍵部分是確保內(nèi)部襯底和外延晶圓的能力,以消除采購(gòu)利潤(rùn)率。此外,破壞性 SiC 襯底形成、晶錠切割、鋸切/拋光等的機(jī)會(huì)具有高回報(bào),并且正在受到多家公司的追捧。

碳化硅器件制造

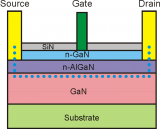

許多成熟的硅技術(shù)工藝已成功轉(zhuǎn)移到 SiC。然而,SiC 材料特性需要優(yōu)化特定工藝,包括晶圓減薄、蝕刻、熱注入和退火,以及低電阻率歐姆接觸形成。SiC 對(duì)化學(xué)溶劑是惰性的,只有干法蝕刻是可行的。此外,碳化硅的硬度導(dǎo)致光刻膠選擇性低,碳化硅光刻圖案化和蝕刻需要通常由金屬或電介質(zhì)組成的“硬”掩模。

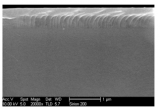

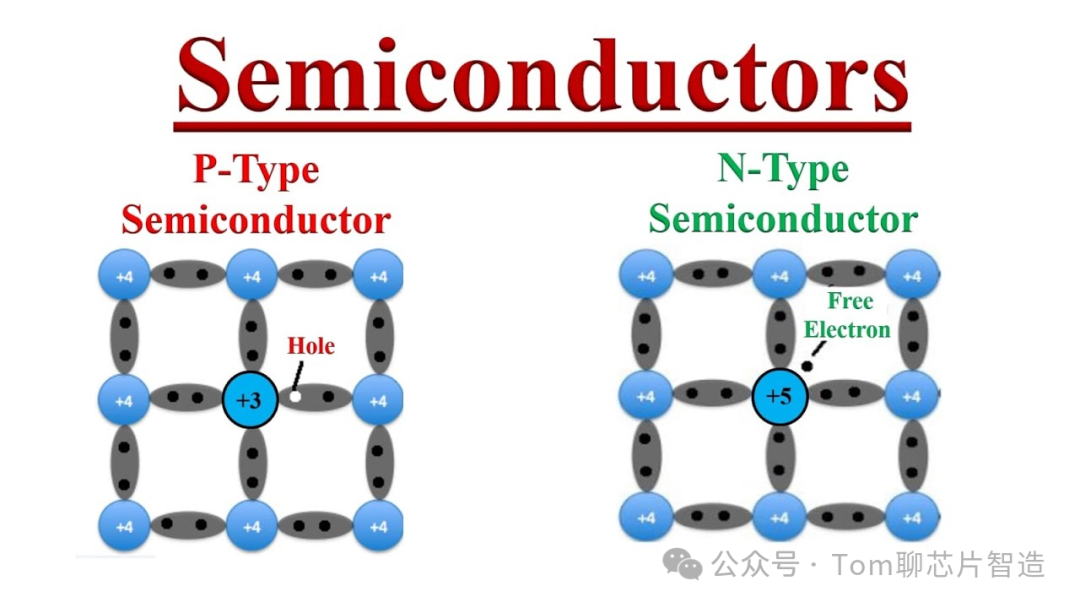

由于 SiC 的高熔點(diǎn)和低摻雜劑在 SiC 內(nèi)的擴(kuò)散常數(shù),傳統(tǒng)的熱擴(kuò)散在摻雜 SiC 中是不現(xiàn)實(shí)的。加熱離子注入通常用于 10 16 –10 20 cm –3的摻雜密度(較高的摻雜密度有助于形成歐姆接觸),室溫注入可以很好地用于低注入劑量(~10 15 cm –3)。氮/磷和鋁分別是 n 型和 p 型 SiC 摻雜的優(yōu)選雜質(zhì)。離子注入后,進(jìn)行 1,600°C 至 1,800°C 的退火,以恢復(fù)晶格損傷和高摻雜電激活。正如從它們的低擴(kuò)散常數(shù)所預(yù)期的那樣,在對(duì) Al、P 和 N 進(jìn)行退火之后,仍保留了注入時(shí)的深度分布。缺乏擴(kuò)散使得在 SiC 中容易形成淺結(jié)而難以形成深結(jié)。在退火過(guò)程中,覆蓋 SiC 晶片的保護(hù)蓋層保護(hù)其表面免受由于 Si 脫附和表面原子遷移而導(dǎo)致的退化(圖 1)。

圖 1:“p+ 離子注入后”經(jīng)過(guò) 1,650?C 退火的 SiC 晶圓在存在碳保護(hù)蓋層的情況下的掃描電子顯微鏡圖像。獲得了優(yōu)異的表面形態(tài)和高器件良率。

SiC/金屬勢(shì)壘的高值導(dǎo)致金屬接觸整流,并且歐姆接觸形成需要后金屬沉積退火。通常,50 到 100 nm 的 Ni 層在晶圓上進(jìn)行毯式沉積和圖案化,以便在 n 型和 p 型摻雜區(qū)域上同時(shí)形成歐姆接觸。鎳圖案晶片的高溫退火產(chǎn)生用于低電阻歐姆接觸形成的鎳硅化物。

與 Si 晶片不同,SiC 晶片是透明的。這使得使用“硅”工具進(jìn)行 CD-SEM 和計(jì)量測(cè)量變得復(fù)雜,因?yàn)榻蛊矫媸鞘褂?a target="_blank">光學(xué)顯微鏡確定的。現(xiàn)在可以從多家供應(yīng)商處獲得特定于 SiC 的波長(zhǎng)計(jì)量/檢測(cè)工具。

另一個(gè)問(wèn)題是與硅相比,碳化硅晶片相對(duì)缺乏平坦度,這會(huì)使光刻復(fù)雜化。此外,高溫 SiC 加工會(huì)進(jìn)一步降低晶圓的平整度,有時(shí)會(huì)導(dǎo)致晶圓無(wú)法使用。這對(duì)于 3.3-kV 器件制造中使用的厚外延晶片來(lái)說(shuō)尤其成問(wèn)題。正在努力生產(chǎn)更平坦的起始 SiC 晶圓,并盡量減少制造過(guò)程中的平坦度退化。

最后,不良的 SiC/SiO 2界面質(zhì)量降低了反型層遷移率。因此,鈍化技術(shù),包括氮化物退火,被用來(lái)改善 SiC/SiO 2界面質(zhì)量,類似于硅的情況。

碳化硅晶圓廠基礎(chǔ)設(shè)施

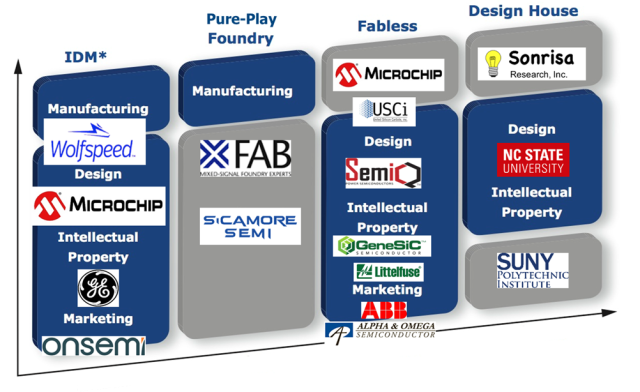

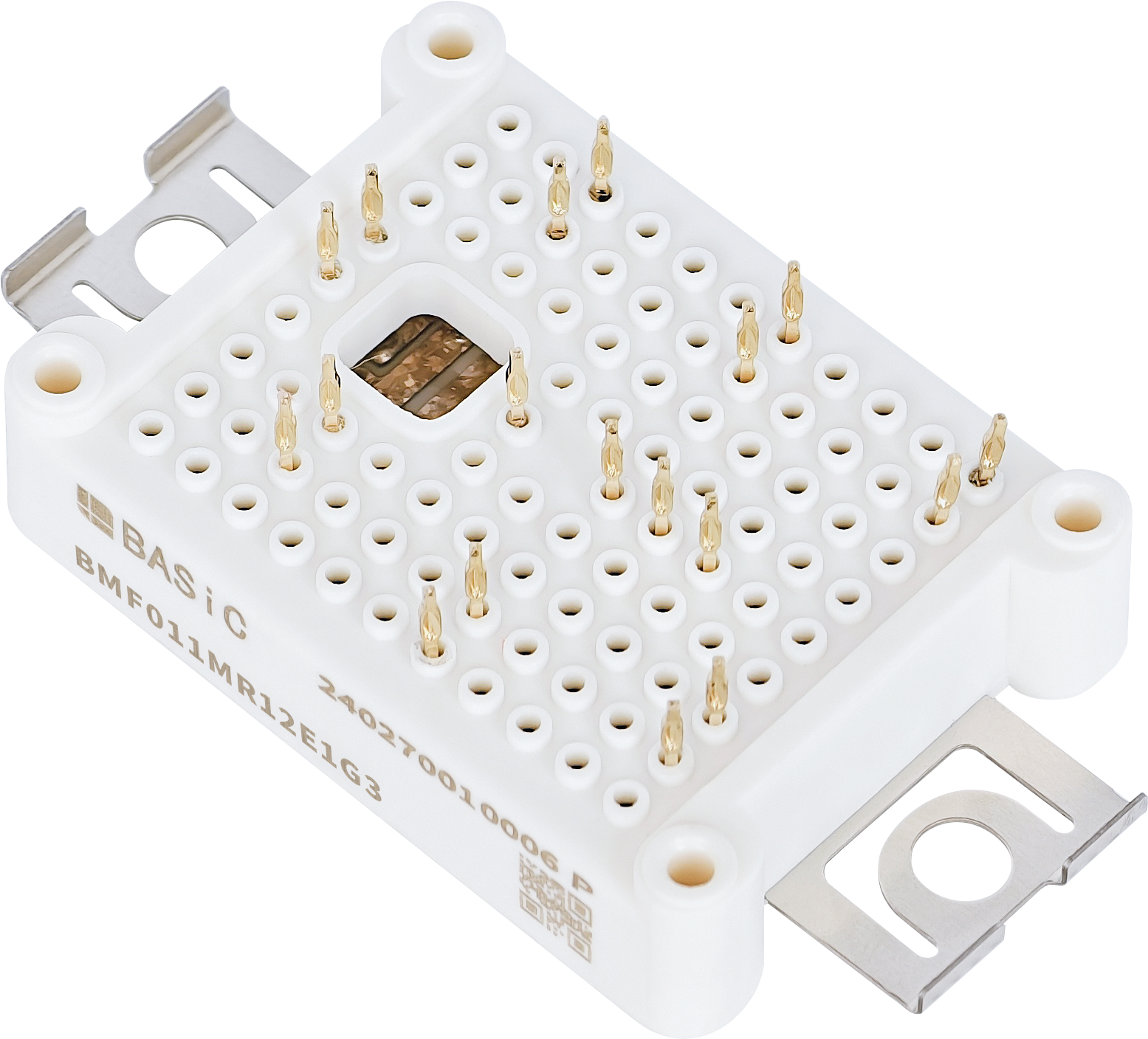

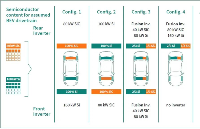

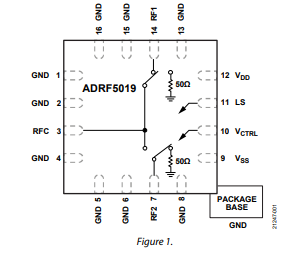

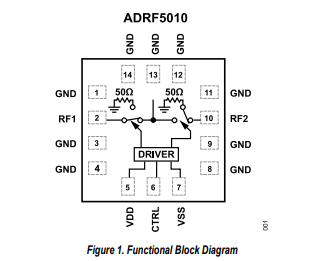

設(shè)備制造商已經(jīng)為多個(gè) SiC 加工步驟開發(fā)了 IP,并在設(shè)計(jì)和加工方面展開了競(jìng)爭(zhēng)。盡管 SiC 不完全兼容 CMOS,但 SiC 行業(yè)通過(guò)進(jìn)行適應(yīng)現(xiàn)有晶圓廠所需的相對(duì)較小的財(cái)務(wù)投資,充分利用了 Si 技術(shù)工藝和基礎(chǔ)設(shè)施。如今,SiC 制造已經(jīng)成熟,其晶圓廠基礎(chǔ)設(shè)施與 Si 類似。集成 SiC 器件制造商與代工廠和無(wú)晶圓廠公司共存,設(shè)計(jì)公司提供可用于加速進(jìn)入市場(chǎng)的專業(yè)知識(shí)和 IP(圖 2)。

與硅一起在量產(chǎn)晶圓廠中制造 SiC 器件已成為利用硅制造規(guī)模經(jīng)濟(jì)的一種降低成本的模式。通過(guò)重新利用舊的、完全折舊的 150 毫米(很快為 200 毫米)硅晶圓廠,可以用支持獨(dú)特 SiC 加工步驟所需的相對(duì)較小的投資來(lái)制造 SiC 功率器件。通過(guò)利用成熟的硅量產(chǎn)來(lái)最小化制造成本假設(shè)晶圓廠的負(fù)載接近產(chǎn)能,標(biāo)準(zhǔn)硅和碳化硅工藝在同一條生產(chǎn)線上運(yùn)行。

此外,匯總批量晶圓廠對(duì) SiC 襯底和外延層的需求有助于降低材料成本。完全折舊的 Si + SiC “容量負(fù)載”晶圓廠的制造成本降低,再加上材料成本的降低,可以顯著降低 SiC 器件的價(jià)格。這種方法為過(guò)時(shí)的硅晶圓廠提供了一個(gè)新的機(jī)會(huì),這些晶圓廠沒有跟上過(guò)去 20 年溝道長(zhǎng)度縮短的步伐,可以繼續(xù)制造傳統(tǒng)的硅部件,同時(shí)增加需要相對(duì)適中的 ~0.3-μ 設(shè)計(jì)規(guī)則的 SiC 制造。

圖 2:美國(guó) SiC 晶圓廠基礎(chǔ)設(shè)施與 Si 類似。它由集成設(shè)備制造商、代工廠、無(wú)晶圓廠公司和設(shè)計(jì)公司組成。

概括

SiC 引人注目的效率和系統(tǒng)優(yōu)勢(shì)正在被廣泛采用,從而實(shí)現(xiàn)制造規(guī)模經(jīng)濟(jì)并降低系統(tǒng)成本。與 Si 相比,晶圓在 SiC 器件總成本中所占的比例過(guò)高。碳化硅制造成熟,包括非 CMOS 兼容工藝。

參考

PowerUP 虛擬會(huì)議(2022 年 6 月 28 日至 30 日)

審核編輯 黃昊宇

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論