傾佳電子碳化硅 (SiC) MOSFET 分立器件與功率模塊規格書深度解析與應用指南

傾佳電子(Changer Tech)是一家專注于功率半導體和新能源汽車連接器的分銷商。主要服務于中國工業電源、電力電子設備和新能源汽車產業鏈。傾佳電子聚焦于新能源、交通電動化和數字化轉型三大方向,分銷代理BASiC基本半導體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅動板等功率半導體器件以及新能源汽車連接器。

傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

傾佳電子楊茜咬住SiC碳化硅MOSFET功率器件三個必然,勇立功率半導體器件變革潮頭:

傾佳電子楊茜咬住SiC碳化硅MOSFET模塊全面取代IGBT模塊和IPM模塊的必然趨勢!

傾佳電子楊茜咬住SiC碳化硅MOSFET單管全面取代IGBT單管和大于650V的高壓硅MOSFET的必然趨勢!

傾佳電子楊茜咬住650V SiC碳化硅MOSFET單管全面取代SJ超結MOSFET和高壓GaN 器件的必然趨勢!

摘要

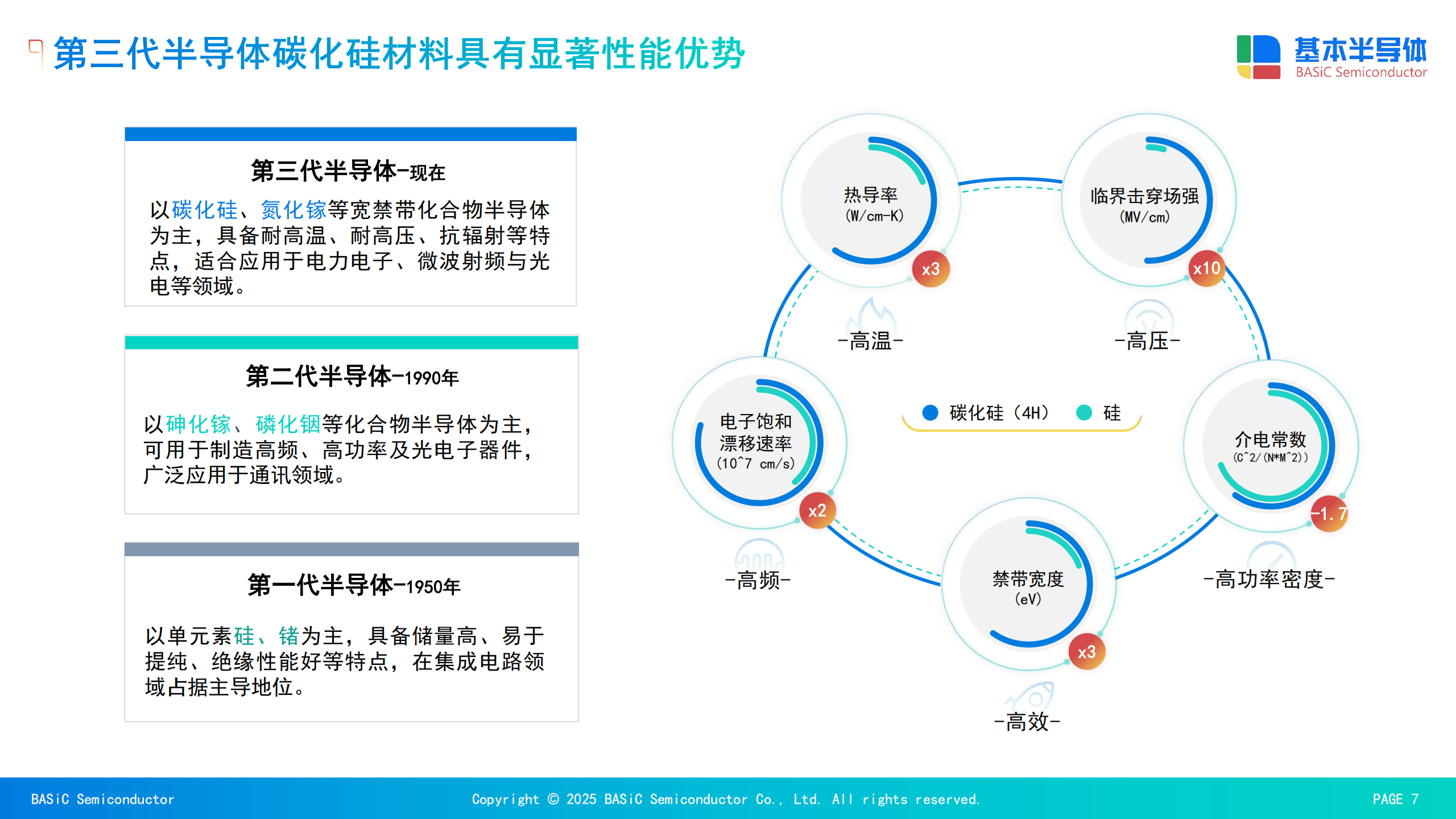

隨著寬禁帶半導體技術的飛速發展,碳化硅(SiC)MOSFET 已成為高頻、高壓、高功率密度電力電子轉換器的核心器件。與傳統的硅基(Si)IGBT 和 MOSFET 相比,SiC 器件憑借其寬禁帶(3.26 eV)、高臨界擊穿場強(比 Si 高 10 倍)和高熱導率等固有物理優勢,能夠顯著降低開關損耗并提升系統效率 1。然而,這些物理特性的改變也使得 SiC MOSFET 的規格書參數呈現出與硅器件截然不同的特征。工程師若僅沿用硅器件的經驗解讀 SiC 規格書,極易在柵極驅動設計、熱管理及短路保護等方面產生誤判,進而影響系統的可靠性。

傾佳電子旨在為電力電子工程師提供一份詳盡的 SiC MOSFET 規格書解讀指南。傾佳電子將涵蓋從單管到功率模塊的全系列參數,深入剖析絕對最大額定值、靜態電氣特性、動態開關特性、熱阻抗特性及可靠性指標。特別針對 SiC 特有的參數——如不對稱柵極電壓額定值、體二極管的雙極性退化效應、開爾文源極(Kelvin Source)的影響、以及短路耐受時間(tSC)的限制——進行重點闡述,并結合實際應用場景探討參數間的制約關系與設計權衡。

1. 絕對最大額定值(Absolute Maximum Ratings):安全邊界的物理詮釋

絕對最大額定值定義了器件能夠承受的應力極限。超過這些限制,即便是一瞬間,也可能導致器件的永久性損壞或性能的不可逆退化。對于 SiC MOSFET 而言,其額定值的設定邏輯與失效機理與硅器件存在顯著差異。

1.1 漏源極電壓 (VDSS) 與擊穿機理

VDSS 代表了器件在關斷狀態下(VGS=0V)漏極與源極之間所能承受的最大電壓。雖然 SiC 材料具有極高的臨界擊穿場強,允許在更薄的漂移層上實現高耐壓(如 650V, 1200V, 1700V, 3300V),但設計者必須清醒地認識到,VDSS 是一個絕對上限,而非工作電壓 。

在實際的高頻開關應用中,電路中的寄生電感(Lσ)與極高的電流變化率(di/dt)相互作用,會在關斷瞬間產生電壓尖峰(Vspike=VDC+Lσ×di/dt)。SiC MOSFET 的開關速度遠快于 Si IGBT,這意味著在同樣的雜散電感下,SiC 會產生更高的電壓過沖。因此,設計者必須預留充足的電壓裕量,通常建議工作母線電壓不超過 VDSS 的 80% 。若電壓尖峰超過 VDSS,器件將進入雪崩擊穿模式,雖然 SiC 具備一定的雪崩耐受能力,但這并非正常工作狀態。

1.2 柵源極電壓 (VGSS) 的不對稱性與氧化層可靠性

與硅 MOSFET 通常具有對稱的柵極耐壓(如 ±20V)不同,SiC MOSFET 的柵極氧化層界面特性決定了其額定電壓往往是不對稱的,常見的額定值?5V/+18V 。這種不對稱性源于 SiC 與 SiO2 界面處較高的缺陷密度以及 SiC 側較高的電場強度。

正向偏置 (+VGSS):為了獲得最低的導通電阻 (RDS(on)),SiC MOSFET 通常推薦在接近最大額定值的電壓下驅動(如 +18V )。然而,長期承受過高的正向柵壓會加速經時介質擊穿(TDDB),縮短器件壽命。因此,規格書中通常會區分“推薦工作電壓”(Recommended Operating Voltage)和“絕對最大電壓”。例如,某器件可能允許瞬態達到 +22V,但推薦工作電壓嚴格限制在 +18V 。

負向偏置 (?VGSS):由于 SiC MOSFET 的閾值電壓 (VGS(th)) 較低且隨溫度升高而降低,為了防止在關斷過程中因米勒效應(dV/dt 耦合)導致的誤導通,通常必須施加負偏置電壓 -5V。VGSS 的負向極限限制了設計者可使用的負壓幅度。如果負壓過大,不僅可能導致柵極氧化層損傷,還可能引起閾值電壓的漂移(Vth Hysteresis),這是 SiC 特有的界面陷阱效應導致的 。

1.3 漏極電流 (ID) 與 脈沖電流 (IDM)

規格書中的連續漏極電流 ID 通常是一個基于熱阻計算出來的理論值,而非實測值。它表示在特定的殼溫(TC,通常為 25°C 或 100°C)下,器件結溫達到最大允許值(Tj,max)時所能流過的電流。

ID=RDS(on)×RthJCTj,max?TC

然而,在實際的大功率模塊或分立器件中,電流能力往往受到封裝限制(Package Limit),例如鍵合線的熔斷電流或端子的載流能力。仔細閱讀規格書會發現,某些器件的計算電流可能高達 100A,但受限于 TO-247 封裝引腳,實際標注的 ID 被限制在 75A 左右 。

脈沖漏極電流 IDM 則定義了器件在極短時間內(通常為微秒級)承受大電流的能力,這通常受限于器件的瞬態熱阻抗 (ZthJC) 和安全工作區 (SOA)。對于 SiC MOSFET,IDM 通常是連續電流的 2 到 4 倍 。

1.4 功率耗散 (Ptot) 的誤區

Ptot 是指當殼溫恒定在 25°C 時,器件內部能夠耗散的最大熱功率。這是一個理想化的參數,因為在實際應用中,散熱器極其難以將殼溫維持在室溫。該參數主要用于比較不同器件的熱性能優劣,而非設計依據。實際允許的功耗必須根據實際的散熱條件(RthCA)和環境溫度進行降額計算 。

1.5 結溫 (Tj) 與存儲溫度 (Tstg)

SiC 材料本身的固有本征溫度極高(超過 600°C),但商業化 SiC MOSFET 的最高結溫 (Tj,max) 通常限制在 150°C 或 175°C。這一限制并非來自芯片本身,而是受限于封裝材料(如環氧樹脂、焊料層、鍵合線)的耐溫能力 。隨著封裝技術的進步(如銀燒結技術的應用),部分先進模塊的 Tj,max 正逐步提升至 200°C,這將顯著提升器件的功率密度。

2. 模塊級特性與機械參數(Module Characteristics)

對于 SiC 功率模塊(如 62mm 封裝或 EasyPACK 封裝),除了芯片本身的參數外,模塊的封裝特性對系統設計至關重要。

2.1 絕緣電壓 (Visol)

絕緣電壓是指模塊的功率端子與底板(散熱器)之間能夠承受的電壓有效值(RMS),通常測試時間為 1 分鐘。常見的等級有 2500V、3000V 甚至 4000V 。這一參數直接決定了系統是否符合特定的安規標準(如 UL1557)。在高壓應用中,高 Visol 等級是確保操作人員安全和防止系統對地擊穿的關鍵。

2.2 雜散電感 (Lσ 或 LsCE)

在 SiC 模塊規格書中,雜散電感是一個極其關鍵的參數。由于 SiC MOSFET 的開關速度極快(di/dt 可達數 kA/μs),即便是極小的雜散電感也會產生巨大的電壓過沖。

Vovershoot=Lσ×dtdi

傳統 IGBT 模塊的雜散電感可能在 20nH 到 50nH 之間,而為了適配 SiC 的高速特性,新型低電感模塊設計通常將 Lσ 控制在 10nH 甚至更低 10。在 BMF540R12KA3 等模塊的規格書中,雜散電感可能作為開關特性測試條件的一部分給出(如 Lσ=30nH),這提示了測試環境的限制,也暗示了實際應用中母排設計必須追求極低電感 。

2.3 模塊引線電阻 (RCC′+EE′)

這是一個經常被忽視但對高電流模塊至關重要的參數。它代表了從模塊外部端子到芯片表面的連接電阻(包括端子、鍵合線、覆銅板走線等)。在幾百安培的大電流下,即便 0.5 mΩ 的引線電阻也會產生數十瓦的額外損耗(Ploss=I2×R)。

熱計算修正:規格書中的 VDS(on) 或 VCE(sat) 有時是在芯片級(Chip level)定義的,有時是在端子級(Terminal level)定義的。若是前者,計算總損耗時必須加上引線電阻產生的壓降;若是后者,則已包含。明確這一點對于精確的熱仿真至關重要 。

2.4 相比漏電起痕指數 (CTI)

CTI(Comparative Tracking Index)衡量了封裝絕緣材料在受污染環境下抵抗表面漏電起痕(Tracking)的能力。CTI 值越高(如 >400 或 >600),意味著材料絕緣性能越好,在 PCB 設計或模塊布局時可以允許更小的爬電距離(Creepage Distance),從而有助于提高系統的功率密度 。SiC 模塊通常采用高 CTI 值的材料以適應高壓緊湊型設計。

2.5 安裝扭矩 (Mounting Torque)

對于依靠螺栓固定的模塊,規格書會嚴格規定安裝扭矩(如 2.5 - 5 N.m)。

過小:導致接觸熱阻(RthCS)過大,熱量無法有效傳導至散熱器,導致過熱失效。

過大:可能導致陶瓷基板(DBC/AMB)破裂,破壞絕緣性能,甚至直接壓碎芯片。

專業的裝配工藝要求分步擰緊,并嚴格控制導熱硅脂的厚度。

3. 靜態電氣特性(Static Characteristics):導通與阻斷的細節

靜態特性描述了器件在穩態導通或關斷時的行為,主要影響導通損耗和靜態功耗。

3.1 導通電阻 (RDS(on)) 的復雜依賴性

RDS(on) 是 SiC MOSFET 最核心的參數,直接決定了導通損耗。與硅器件不同,SiC MOSFET 的 RDS(on) 表現出獨特的特性:

柵極電壓依賴性:SiC MOSFET 的跨導較低,這意味著其通道并沒有在閾值電壓后迅速完全開啟。從 +15V 增加到 +18V 或 +20V,其 RDS(on) 仍會有顯著下降 。因此,為了獲得最佳效率,推薦使用規格書建議的較高柵壓(如 +18V)進行驅動。

正溫度系數 (PTC):幸運的是,SiC MOSFET 的 RDS(on) 隨溫度升高而增加。例如,從 25°C 到 175°C,電阻值通常增加 1.4 到 1.6 倍 20。這種 PTC 特性有利于多管并聯時的均流,防止熱失控。相比之下,硅 CoolMOS 的電阻隨溫度變化率更大(可達 2.5 倍),這意味著 SiC 在高溫下的導通性能衰減更小,實際高溫運行時的效率優勢比室溫下看起來更大。

3.2 閾值電壓 (VGS(th)) 與漂移

VGS(th) 定義為漏極電流開始流動的柵極電壓。SiC MOSFET 的 VGS(th) 具有以下關鍵特征:

負溫度系數:隨溫度升高,VGS(th) 會顯著降低。一個室溫下閾值為 2.7V 的器件,在 175°C 時可能降至 1.9V 甚至更低 。這極大地增加了高溫下因噪聲或米勒效應導致誤導通(Parasitic Turn-on)的風險,因此在關斷時施加負偏置電壓(如 -5V)幾乎是強制性的 。

漂移現象:由于柵氧界面的缺陷,長時間的正向或負向偏置應力(PBTI/NBTI)會導致 VGS(th) 發生漂移。現代 SiC 工藝已通過篩選和工藝優化控制了這一問題,但設計者仍需關注規格書中的 VGS(th) 最小值范圍 。

3.3 漏電流 (IDSS)

雖然 SiC 是寬禁帶材料,理論漏電流極低,但實際器件的 IDSS 仍受表面漏電和封裝影響。規格書通常給出 25°C 和高溫下的漏電流值。值得注意的是,SiC 的高溫漏電流依然非常小,這使得它非常適合高壓阻斷應用,且不會因漏電流引起顯著的熱失控風險。

4. 動態電氣特性(Dynamic Characteristics):開關行為的物理本質

SiC MOSFET 的優勢在于“快”。要理解其開關行為,必須深入解讀電容、電荷和內部電阻參數。

4.1 寄生電容 (Ciss,Coss,Crss) 的非線性

MOSFET 的三個寄生電容隨漏源電壓 (VDS) 的變化呈現高度非線性。

Ciss(輸入電容,CGS+CGD):決定了柵極驅動所需的瞬態電流。雖然 SiC 的 Ciss 通常小于同規格的 Si IGBT,但由于驅動電壓擺幅大(如 -5V 到 +18V,共 23V 擺幅),驅動功率需求并不低 。

Coss(輸出電容,CDS+CGD):在硬開關中,Coss 儲存的能量 (Eoss) 會在每次開通時被耗散在通道內,轉化為熱量。在軟開關(如 LLC、ZVS)應用中,Coss 決定了實現零電壓開通所需的死區時間和勵磁電流。

Crss(反向傳輸電容/米勒電容,CGD):這是決定開關速度和抗干擾能力的核心參數。SiC MOSFET 的 Crss 通常極小,這允許極快的電壓轉換速率 (dV/dt)。然而,Crss/Ciss 的比率決定了器件對米勒效應的敏感度。如果該比率過大,漏極電壓的快速跳變會通過 Crss 耦合到柵極,導致柵壓抬升并引起誤導通。

4.2 等效輸出電容 (Co(er) 與 Co(tr))

由于 Coss 隨電壓變化劇烈(在低壓時極大,高壓時極小),為了方便計算,規格書引入了兩個等效線性電容參數 :

Co(er) (能量等效電容):該固定電容值在充電到規定電壓(如 800V)時,所儲存的能量與實際非線性 Coss 儲存的能量 (Eoss) 相同。

Eoss=∫0VDCv?Coss(v)dv=21Co(er)?VDC2

用途:用于計算硬開關拓撲中的開關損耗。

Co(tr) (時間等效電容):該固定電容值在恒流充電到規定電壓時,所需的時間與實際 Coss 相同。

用途:用于計算軟開關拓撲中的死區時間(Dead-time)或 dV/dt 轉換時間。

關鍵洞察:Co(er) 和 Co(tr) 數值可能相差很大。混用會導致損耗估算或時序設計的嚴重偏差。

4.3 柵極電荷 (Qg) 與米勒平臺

Qg 曲線描述了驅動器必須提供的電荷量。曲線中的平坦區域被稱為“米勒平臺”。在此階段,柵極電流全部用于給 Crss 充電,以支持漏極電壓的快速變化 (dVDS/dt),柵壓保持不變。SiC MOSFET 的米勒平臺電壓通常較高(約 6V-10V),且平臺寬度較窄,意味著其開關過程極快 。

4.4 內部柵極電阻 (RG(int))

這是芯片內部柵極流道的物理電阻。與硅器件不同,SiC MOSFET 的 RG(int) 在某些設計中可能受頻率影響 。

影響:RG(int) 與外部柵極電阻 (RG(ext)) 串聯,共同決定了開關速度。如果 RG(int) 過大,即使外部電阻設為零,開關速度也會受限。

振蕩阻尼:適當的 RG(int) 有助于抑制柵極振蕩,但過大會增加開關損耗。在計算驅動電流峰值時,必須包含此電阻:Ig,peak=ΔVGS/(RG(ext)+RG(int)+Rdriver)。

4.5 開關時間與能量 (ton/off,Eon/off)

規格書中的開關時間(td(on),tr,td(off),tf)和損耗能量(Eon,Eoff)是在特定測試條件下測得的(通常是雙脈沖測試,感性負載)。

Eon的構成:包含了 MOSFET 通道的開通損耗以及續流二極管的反向恢復損耗 (Err)。如果是帶有集成 SBD 的 SiC MOSFET,其 Eon 會顯著降低 。

Eoff的特性:SiC MOSFET 沒有 IGBT 的拖尾電流(Tail Current),因此關斷極快,主要受限于 dV/dt 和雜散電感。

損耗估算公式:在實際應用中,電壓和電流往往與測試條件不同。可以使用修正系數進行估算 :

Esw(Iapp,Vapp)≈Esw(datasheet)×(VtestVapp)Kv×(ItestIapp)Ki

其中 Kv 通常接近 1.2-1.4(考慮電容非線性),Ki 接近 1(線性關系)。

5. 第三象限特性與體二極管(Reverse Diode Characteristics)

SiC MOSFET 在橋式電路中需要處理反向續流。其特性由體二極管或同步整流模式決定。

5.1 體二極管的正向壓降 (VSD)

SiC MOSFET 的本征體二極管是 PN 結結構。由于 SiC 的禁帶寬度大,其開啟電壓(Knee Voltage)很高,通常在 3V 到 4V 以上 。

功耗陷阱:如果在死區時間內長時間讓體二極管導通,巨大的 VSD 會導致嚴重的導通損耗。

同步整流 (Synchronous Rectification):為了避免上述損耗,必須在二極管導通后迅速開啟 MOSFET 溝道(VGS>Vth)。此時電流流經溝道,表現為電阻特性(V=I×RDS(on)),壓降可大幅降低至 1V 以下。規格書中的“第三象限特性曲線”通常會展示 VGS=?5V(二極管模式)和 VGS=18V(同步整流模式)兩條曲線,兩條曲線的交點提示了在極大電流下二極管模式可能反而壓降更低,但在正常工作范圍內,同步整流優勢明顯 。

5.2 反向恢復特性 (Qrr,trr)

雖然 SiC 體二極管是 PN 結,但由于載流子壽命極短,其反向恢復電荷 (Qrr) 遠小于同電壓等級的硅快恢復二極管。

溫度獨立性:硅二極管的 Qrr 隨溫度升高而急劇增加,而 SiC 二極管的 Qrr 對溫度幾乎不敏感 。這使得 SiC 轉換器在高溫下仍能保持極低的開關損耗和電磁干擾 (EMI)。

6. 熱阻抗特性與瞬態熱響應

6.1 熱阻 (RthJC) 與 瞬態熱阻抗 (ZthJC)

RthJC:描述了穩態下的散熱能力。

ZthJC曲線:描述了器件對短脈沖功率的熱響應。對于毫秒級甚至微秒級的過載脈沖,熱量還沒來得及傳導到散熱器,主要由芯片本身的熱容吸收。ZthJC 曲線允許工程師計算在脈沖負載下的瞬時結溫升 。

應用:在電機啟動堵轉或短路保護設計中,必須使用 ZthJC 而非 RthJC 來評估芯片是否會過熱燒毀。

7. 安全工作區 (SOA) 與魯棒性

7.1 正向偏置安全工作區 (FBSOA)

FBSOA 定義了器件在導通狀態下允許的電壓和電流范圍。

線性模式限制:與硅 MOSFET 不同,SiC MOSFET 的 FBSOA 曲線在“線性模式區”(高電壓、大電流同時存在)往往受到更嚴格的限制,或者甚至不建議在此區域工作 。這是因為 SiC 芯片面積小,功率密度極高,且在某些條件下可能出現類似 Spirito 效應的熱不穩定性(局部熱點導致電流集中)。

應用警示:SiC MOSFET 不適合用作線性穩壓器或電子負載。它們是為開關應用而優化的。

7.2 反向偏置安全工作區 (RBSOA)

RBSOA 定義了關斷過程中的安全軌跡。通常為矩形區域,即在關斷瞬間,電壓不超過 VDSS,電流不超過 IDM 。SiC MOSFET 必須在此范圍內硬關斷,且需嚴格控制關斷電壓尖峰。

7.3 短路耐受時間 (tSC)

這是 SiC MOSFET 的一個短板。由于芯片面積小、熱容量小,SiC MOSFET 承受短路電流的時間顯著短于 IGBT。

典型值:IGBT 通常為 10μs,而 SiC MOSFET 通常僅為 2μs 到 3μs 。

保護要求:這對門極驅動器的去飽和檢測(Desat)或電流保護電路提出了極高的響應速度要求。標準 IGBT 驅動器可能太慢,無法保護 SiC 器件。

7.4 雪崩能量 (EAS)

雖然 SiC 具有 Avalanche Ruggedness,但由于溝槽柵(Trench)結構的電場集中效應和較小的芯片體積,其標稱的 EAS 值可能看似不高。但關鍵在于其在規定能量下的耐受力是可靠的。設計時應盡量避免讓 SiC 器件頻繁進入雪崩狀態,通常建議通過鉗位電路吸收感性關斷能量 。

7.5 dV/dt 耐受力

SiC MOSFET 能夠承受極高的電壓變化率(如 >100 V/ns)。

風險:過高的 dV/dt 即使不擊穿器件,也可能通過寄生電容耦合導致低壓側電路故障,或觸發器件內部寄生 BJT 的閂鎖效應(Latch-up)。不過現代 SiC 器件通常對 dV/dt 具有很高的免疫力,規格書常標注 >50 V/ns 或更高 。

8. 封裝對性能的影響:開爾文源極 (Kelvin Source)

在閱讀規格書時,封裝引腳配置是一個極易被忽視但至關重要的細節。

8.1 傳統 3 引腳封裝的局限

在 TO-247-3 等傳統封裝中,源極引腳同時承載驅動回路的參考地和功率回路的主電流。功率回路的巨大電流變化 (di/dt) 會在源極引線的寄生電感 (LS) 上產生感應電壓 (V=LS×di/dt)。這個電壓會負反饋到柵極驅動回路,減緩開啟速度,增加開關損耗。

8.2 4 引腳開爾文源極封裝 (TO-247-4)

新型 SiC 分立器件常采用 4 引腳封裝,增加了一個開爾文源極引腳 (Driver Source / Kelvin Source)。

原理:該引腳專門用于連接柵極驅動器的回路參考地,不流過功率電流。因此,功率回路的 di/dt 不會影響驅動電壓。

優勢:這消除了源極電感的負反饋效應,使得 SiC MOSFET 能夠以更快的速度開關,通常可降低 30%-50% 的開關損耗 (Eon) 。

解讀:在對比不同器件規格書時,若一個是 3 引腳,一個是 4 引腳,即使芯片參數相同,4 引腳器件在實際應用中的動態性能也會顯著優越。

9. 結論:解讀 SiC 規格書的系統化思維

深圳市傾佳電子有限公司(簡稱“傾佳電子”)是聚焦新能源與電力電子變革的核心推動者:

傾佳電子成立于2018年,總部位于深圳福田區,定位于功率半導體與新能源汽車連接器的專業分銷商,業務聚焦三大方向:

新能源:覆蓋光伏、儲能、充電基礎設施;

交通電動化:服務新能源汽車三電系統(電控、電池、電機)及高壓平臺升級;

數字化轉型:支持AI算力電源、數據中心等新型電力電子應用。

公司以“推動國產SiC替代進口、加速能源低碳轉型”為使命,響應國家“雙碳”政策(碳達峰、碳中和),致力于降低電力電子系統能耗。

需求SiC碳化硅MOSFET單管及功率模塊,配套驅動板及驅動IC,請添加傾佳電子楊茜微芯(壹叁貳 陸陸陸陸 叁叁壹叁)

解讀 SiC MOSFET 規格書不僅僅是比對數字,更是一個理解器件物理限制與應用場景匹配的過程。工程師應遵循以下邏輯:

核對絕對邊界:確保 VDSS 留有足夠的過沖裕量;嚴格遵守負向柵壓 VGSS 限制以防 Vth 漂移;確認短路保護機制能覆蓋 tSC 的極短時間窗口。

評估靜態損耗:不要只看 25°C 的 RDS(on),更要關注 175°C 下的數值。利用 SiC 的 PTC 特性進行并聯設計,但需警惕 ZTC 點以下的負溫度系數區域不穩定性 。

精算動態損耗:區分 Eon 是否包含二極管損耗;利用 Co(er) 計算電容損耗;意識到實際開關速度受限于外部 RG 和回路電感 Lσ,規格書中的納秒級速度僅在理想測試條件下實現。

重視封裝特性:在高頻應用中,優先選擇帶開爾文源極的封裝或低電感模塊(Lσ<15nH),并關注模塊的 RthJC 和 Visol 等級。

熱設計驗證:利用 ZthJC 曲線校核最惡劣工況(如堵轉、浪涌)下的瞬態結溫,確保不超過 Tj,max。

通過全面、深入地理解這些參數及其背后的物理意義,設計者才能真正釋放碳化硅功率器件的潛能,構建出高效、可靠且具有競爭力的電力電子系統。

審核編輯 黃宇

-

MOSFET

+關注

關注

151文章

10210瀏覽量

234523 -

分立器件

+關注

關注

5文章

267瀏覽量

22322 -

功率模塊

+關注

關注

11文章

675瀏覽量

47011

發布評論請先 登錄

位移電流物理本質與碳化硅(SiC)功率器件應用解析

SiC碳化硅MOSFET功率半導體銷售培訓手冊:電源拓撲與解析

雙脈沖測試技術解析報告:國產碳化硅(SiC)功率模塊替代進口IGBT模塊的驗證與性能評估

傾佳電子碳化硅SiC MOSFET驅動特性與保護機制深度研究報告

傾佳代理的基本半導體碳化硅MOSFET分立器件產品力及應用深度分析

碳化硅 (SiC) MOSFET 分立器件與功率模塊規格書深度解析與應用指南

碳化硅 (SiC) MOSFET 分立器件與功率模塊規格書深度解析與應用指南

評論