聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

dsp

+關注

關注

561文章

8244瀏覽量

366603 -

嵌入式

+關注

關注

5198文章

20442瀏覽量

333979 -

賽靈思

+關注

關注

33文章

1798瀏覽量

133425

發布評論請先 登錄

相關推薦

熱點推薦

ARM嵌入式這樣學

葉等等,假如你將DSP看做一款MCU來搞,那太浪費了,100塊的東西當幾塊錢的來用。要用好它,物盡其用,那真的很難,要精通算法才行。

2、嵌入式軟件是什么?

嵌入式軟件分為

發表于 12-04 07:48

利用開源uart2axi4實現串口訪問axi總線

,可以實現跨fpga平臺使用。利用uart2axi4我們可以通過python,輕松訪問axi4_lite_slave寄存器,大大方便fpga工程師進行系統調試和定位bug。

嵌入式系統的定義和應用領域

大量使用了嵌入式系統。

不僅如此,汽車電子類產品、網絡通信類產品、通信與娛樂產品以及工業控制類產品等眾多領域也都受益于嵌入式系統的應用。可以說,嵌

發表于 11-17 06:49

NVMe高速傳輸之擺脫XDMA設計24: UVM 驗證包設計

。

Axi4_lite_agent 負責對接 AXI4-Lite 接口。 在 DUT 使用的三個接口中, AXI4-Lite

發表于 08-29 14:33

NVMe IP高速傳輸擺脫XDMA設計之四:系統控制模塊設計

的方式實現功能的控制和狀態的監測。 為方便用戶訪問這些寄存器組, 系統控制模塊采用 AXI4-Lite 總線作為接口, AXI4-Lite 接口

發表于 06-29 18:07

NVMe IP高速傳輸卻不依賴XDMA設計之三:系統架構

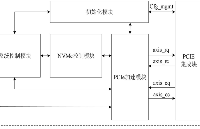

所設計的新系統架構中,Nvme over PCIe IP通過 PCIe 3.0x4 接口連接 NVMe固態硬盤, 并提供 AXI4-Lite 接口

NVMe IP之AXI4總線分析

針對不同的應用場景,制定了三個不同類型的接口,其中包括AXI4-Full、AXI4-Lite以及AXI4-Stream。表1為三種AXI4總

發表于 06-02 23:05

AMD Versal Adaptive SoC Clock Wizard AXI DRP示例

本文將使用 Clocking Wizard 文檔 PG321 中的“通過 AXI4-Lite 進行動態重配置的示例”章節作為參考。

將DSP設計融入嵌入式系統的AXI4-Lite接口

將DSP設計融入嵌入式系統的AXI4-Lite接口

評論