在 AXI 基礎第 6 講 - Vitis HLS 中的 AXI4-Lite 簡介中,使用 C 語言在 HLS 中創(chuàng)建包含 AXI4-Lite 接口的 IP。

在本篇博文中,我們將學習如何導出 IP 以供在 Vivado Design Suite 中使用、如何將其連接到其它 IP 核與處理器以及如何在板上運行工程。

本篇博文將分為 3 個部分:

1. 從 Vitis HLS 導出 IP。

2. 使用Vivado Design Suite創(chuàng)建硬件。

3. 在Vitis 統(tǒng)一軟件平臺中編寫軟件并在板上運行。

01

導出 IP

在AXI 基礎第 6 講 - Vitis HLS 中的 AXI4-Lite 簡介中,我們創(chuàng)建了 1 個包含 AXI4-Lite 接口的 IP。如果要把新 IP 連接到任何其它 IP 或者連接到 PS,則首先需要將軟件代碼綜合成 RTL(即,將其轉(zhuǎn)換為硬件)。隨后,我們就可以將 RTL IP 導出到 Vivado Design Suite,以便在其中將其連接到其它 IP 核或者連接到 PS。

1.1. 按如下所示編輯代碼,然后保存。

int example(char *a, char *b, char *c)

{

#pragma HLS INTERFACE s_axilite port=a bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=b bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=c bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=return bundle=BUS_A

*c += *a + *b;

int result = 0;

result = *c;

return result;

}

1.2. 鑒于我們將在板上運行此代碼,因此需要將綜合設置更改為對應于可用的開發(fā)板的設置。

我這里選擇的是 Zynq UltraScale+ ZCU106 評估板。要更改所使用的開發(fā)板,請轉(zhuǎn)至“解決方案 (Solution) -》 解決方案設置 (Solution Settings) -》 綜合設置 (Synthesis Settings)”,然后選擇如下所示高亮的“。..”即可選擇可用的開發(fā)板。

1.3. 選擇屏幕頂部的綠色運行按鈕 即可運行 C 語言綜合。這樣即可將代碼轉(zhuǎn)換為 RTL:

1.4. 完成綜合后,您可選擇“導出 RTL (ExportRTL)”工具欄按鈕,或者也可以單擊“解決方案 (Solution) -》 導出 RTL (Export RTL)”以打開“Export RTL”對話框。

1.5. 打開的對話框應如下截屏所示。

本文包含有關所有可用選項的詳細解釋。

選擇“配置 (configuration)”選項,為新 RTL IP 添加詳細信息。將顯示名稱更改為“Example”,然后選擇“確定 (OK)”。當您在 Vivado Design Suite 中打開自己的 IP 時,將顯示此名稱。

選擇“瀏覽 (Browse)”按鈕以選擇 Vivado IP (.zip) 文件的輸出位置及其名稱。輸出的 ZIP 文件將包含您的 RTL IP,您可將其導入 Vivado Design Suite。

1.6. 等待工具完成導出,然后打開 Vivado Design Suite。選擇“創(chuàng)建新工程”選項:

1.7. 對于后續(xù)所有其它步驟,請選擇“下一步 (Next)”。選擇器件時,請務必選擇您在創(chuàng)建工程時所選的器件。如果您不確定,可在 Vitis HLS 中的“解決方案設置 (solution settings) -》 綜合設置 (synthesis settings)”下找到該器件。如果您選擇其它器件,那么將您的 IP 導入 Vivado Design Suite 時可能會出現(xiàn)問題。

最后,選擇“完成 (Finish)”以打開空工程。

1.8. 要使用 Vivado 工程中生成的 IP,首先必須將新 IP 存儲庫添加到 Vivado 工程中。此處所示文件夾包含從 Vitis HLS 導出的 .zip 文件。要添加存儲庫,請選擇“設置 (Settings) -》 IP -》 存儲庫 (Repository)”。選擇 + 按鈕并在 Vitis HLS 中選擇 IP 導出的位置(即,以上第 6 步)。

選擇位于對話框底部的“應用 (Apply)”按鈕,然后選擇“確定 (OK)”。

1.9. 選擇 IP 目錄 (Select IP Catalog)。現(xiàn)在,您的新存儲庫應已顯示在目錄中。

如已成功導入 IP,那么詳細信息窗口中所列出的 IP 數(shù)量應為“1”。

注:如果列出的 IP 數(shù)量為 0,那么您可右鍵單擊自己的新存儲庫并選擇“將 IP 添加到存儲庫中 (Add IP to Repository)”。選擇您從 Vitis HLS 導出的 ZIP 文件。隨后,存儲庫中的 IP 數(shù)量應已顯示為“1”。如果未顯示正確數(shù)量,請檢查您在 Vitis HLS 中所選的板/器件與您在 Vivado 中所使用的是否相同,否則,則表示您的 IP 可能不兼容。

1.10. 在 Flow Navigator 中,選擇“創(chuàng)建模塊設計 (Create Block Design)”。

在顯示的選項卡中,選擇 + 按鈕并搜索您在第 6 步中在 Vitis HLS 中指定的 IP 名稱(即,Example)。

祝賀您!您已成功創(chuàng)建了 IP、將其從 Vitis HLS 導出并已添加到 Vivado Design Suite 中的模塊設計中。

單擊 s_axi_BUS_A 旁的 + 按鈕即可展開端口。如需獲取更多相關信息,請參閱 (PG155 )中的 “端口描述”。

02

創(chuàng)建硬件

您可能會想要連接到 PS 以便充分利用其功能。添加 PS IP(如 ZCU106 評估板上提供的 Zynq UltraScale+ MPSoC IP)即可支持您執(zhí)行此操作。

2.1. 將 Zynq UltraScale+ MPSoC IP 添加到模塊框圖中。添加完成后,將在屏幕頂部出現(xiàn)一條提示信息。選擇“運行自動連接功能 (Run Connection Automation)”。

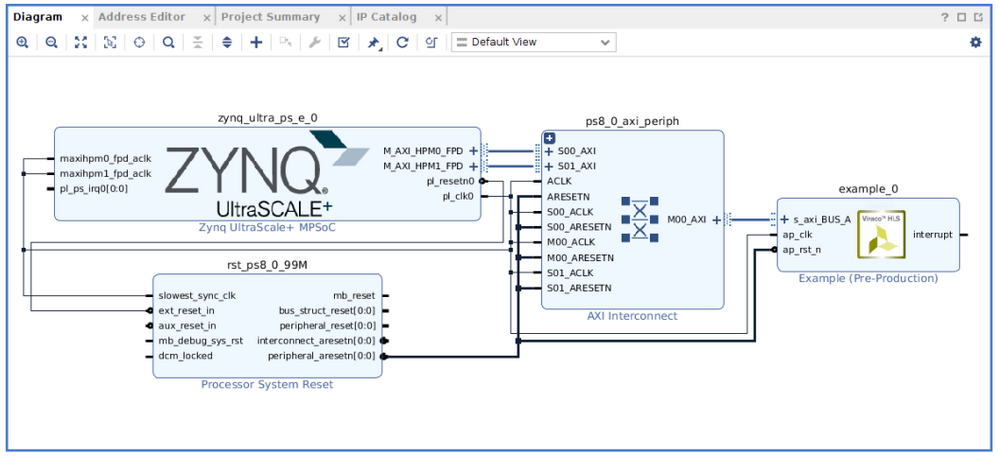

2.2. 這樣即可得到如下圖示。或者,您可為此 IP 手動添加所有器件,并如該圖所示連接這些器件。這樣即可得到如下圖示:

2.3. 右鍵單擊“源 (Source)”選項卡下的《design_name》.bd 以創(chuàng)建 HDL 封裝器 (wrapper)。運行綜合、運行實現(xiàn),然后生成比特流。下一步,選擇“文件 (File) -》 導出 (Export) -》 導出硬件 (Export Hardware)”。請務必選中包含比特流的選項,并記下所選導出位置。這樣即可創(chuàng)建包含所有硬件信息的 XSA 文件。現(xiàn)在,您可以關閉 Vivado。

03

編寫軟件

鑒于您的硬件已完成創(chuàng)建并導出,我們需要編寫軟件以向硬件提供操作指示。我們將在Vitis中編寫軟件。

3.1. 打開 Vitis。在打開的菜單中,選擇“創(chuàng)建平臺工程 (Create Platform Project)”。這將生成工程基本信息,我們將在其中添加硬件信息(XSA 文件)并編寫一些軟件定義。出現(xiàn)提示時,請選中“從 XSA 文件創(chuàng)建 (create from XSA file)”選項。隨后,我們需要選擇以上步驟 2.3 中的 XSA 文件導出位置。繼續(xù)完成其它設置,最后單擊“完成 (Finish)”。

3.2. 下一步,我們需要創(chuàng)建包含軟件的應用工程。它將基于我們的平臺工程,因此其中包含我們的硬件信息,并且我們需要使用該應用工程在目標板上運行應用。選擇“文件 (File) -》 新建 (New) -》 新建應用工程 (New Application Project)”。

3.3. 出現(xiàn)提示時,選中“選擇存儲庫中的平臺 (Select a platform from arepository)”選項。選擇步驟 3.1 中創(chuàng)建的平臺工程,然后單擊“下一步 (Next)”。

3.4. 選擇 Hello World 模板,然后單擊“完成 (Finish)”。

3.5. 現(xiàn)在,Hello World 代碼會顯示在《application_project_name》/src/helloworld.c下。為了執(zhí)行完整性檢查,我們將通過 JTAG 把示例下載到板上,并使用 UART 終端查看 printf 信息。

為此,請連接目標板,并打開終端仿真器軟件(例如,Tera Term)以讀取輸出消息。如果您不知曉如何執(zhí)行此操作,請參閱板相關的用戶指南。 編譯并運行程序。正確完成此操作后,您應可在 Tera Term 中看到 Hello World 打印信息。

3.6. 現(xiàn)在,確認板已正確連接后,下一步即可創(chuàng)建使用 HLS IP 的代碼。從Vitis_Code.c復制代碼(隨附于本教程)并將其粘貼到 helloworld.c 中,替換原有 helloworld 代碼。

保存,然后重新編譯并運行軟件。這次 Tera Term 會提示您提供 2 項輸入:A 和 B,這 2 項將作為輸入一并傳遞給 HLS IP 中,并顯示結(jié)果。

注:由于在 Vitis HLS 中,A 和 B 已定義為“char”類型,因此輸入的值上限為 127。

示例代碼使用由 Vitis 自動創(chuàng)建的函數(shù),因此開發(fā)非常便捷。

在名為X《HLS_IP_name》.h的文件中以及在《platform_project》/hw/drivers/《ex_name》/src 下可找到所使用的函數(shù)。

原文標題:開發(fā)者分享 | AXI 基礎第 7 講 - 使用 AXI4-Lite 將 Vitis HLS 創(chuàng)建的 IP 連接到 PS

文章出處:【微信公眾號:FPGA開發(fā)圈】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

責任編輯:haq

-

C語言

+關注

關注

183文章

7645瀏覽量

146030 -

AXI

+關注

關注

1文章

145瀏覽量

18003 -

HLS

+關注

關注

1文章

135瀏覽量

25951

原文標題:開發(fā)者分享 | AXI 基礎第 7 講 - 使用 AXI4-Lite 將 Vitis HLS 創(chuàng)建的 IP 連接到 PS

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

AMD Versal CPM5 QDMA Gen4x8 ST Only Performance Design CED示例

【請教】FPGA燒錄軟件工具二次開發(fā)問題

Include File解鎖Vector Logger Suite高階功能

電能質(zhì)量在線監(jiān)測裝置的多維度統(tǒng)計報表支持遠程訪問導出嗎?

AMD Vivado Design Suite 2025.2版本現(xiàn)已發(fā)布

vcs和vivado聯(lián)合仿真

Vivado浮點數(shù)IP核的一些設置注意點

在AMD Versal自適應SoC上使用QEMU+協(xié)同仿真示例

Vivado無法選中開發(fā)板的常見原因及解決方法

AMD Vivado Design Suite 2025.1現(xiàn)已推出

如何使用AMD Vitis HLS創(chuàng)建HLS IP

如何使用One Spin檢查AMD Vivado Design Suite Synth的結(jié)果

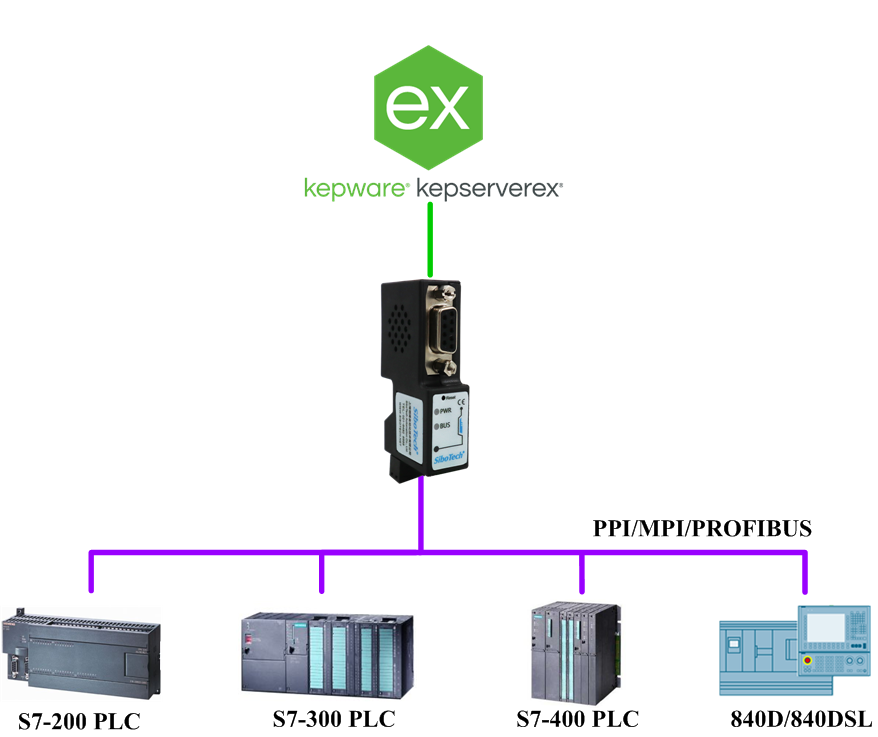

Kepware Siemens Suite

如何導出IP以供在Vivado Design Suite中使用?

如何導出IP以供在Vivado Design Suite中使用?

評論