microblaze和jtag-to-axi(jtag2axi)雖然也提供了訪問axi總線的能力,但是依賴于xilinx平臺。而uart-to-axi(uart2axi4)橋接器并不依賴任何平臺

2025-12-02 10:05:43 1846

1846

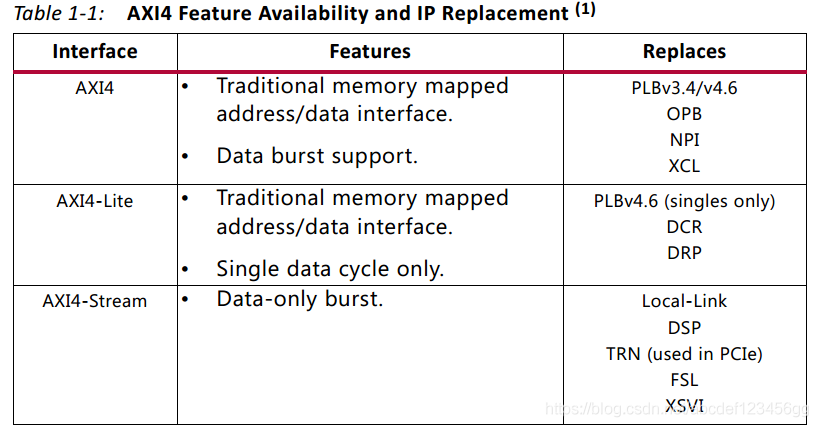

。AXI4-Lite接口的特性如下: 1) 突發長度為1。 2) 所有訪問數據的寬度和數據總線寬度相同。 3) 支持數據總線寬度為32位或64位。 4) 所有的訪問相當于AWCACHE和ARCACHE

2020-09-27 11:33:02 9823

9823

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一種總線協議, Xilinx從 6 系列的 FPGA 開始對 AXI 總線提供支持,目前使用 AXI

2020-12-04 12:22:44 9055

9055

前面一節我們學會了創建基于AXI總線的IP,但是對于AXI協議各信號的時序還不太了解。這個實驗就是通過SDK和Vivado聯合調試觀察AXI總線的信號。由于我們創建的接口是基于AXI_Lite協議

2020-12-23 15:32:37 3253

3253 開發基于總線的系統。 使用的板子是zc702。 AXI總線初識: AXI (Advanced eXtensible Interface),由ARM公司提出的一種總線協議。總線是一組傳輸通道, 是各種邏輯器件

2020-12-25 14:07:02 6725

6725

MPSoC有六個PL側高性能(HP)AXI主接口連接到PS側的FPD(PL-FPD AXI Masters),可以訪問PS側的所有從設備。這些高帶寬的接口主要用于訪問DDR內存。有四個HP AXI

2022-07-22 09:25:24 4483

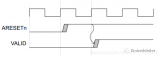

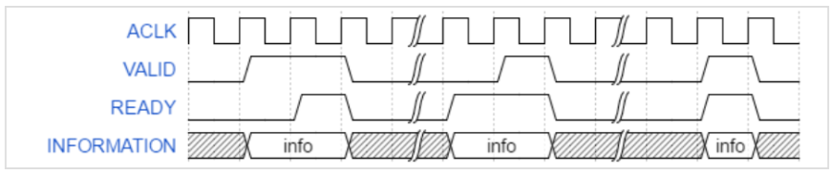

4483 由于ZYNQ架構和常用接口IP核經常出現 AXI協議,賽靈思的協議手冊講解時序比較分散。所以筆者收藏AXI協議的幾種時序,方便編程。

2022-08-02 12:42:17 9566

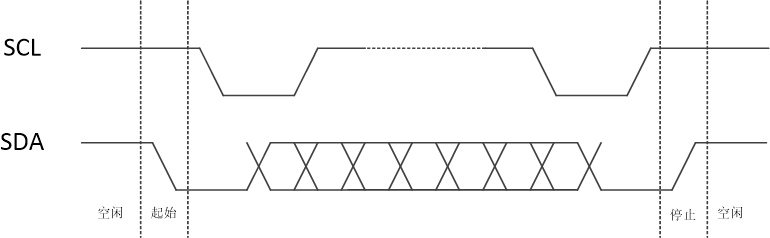

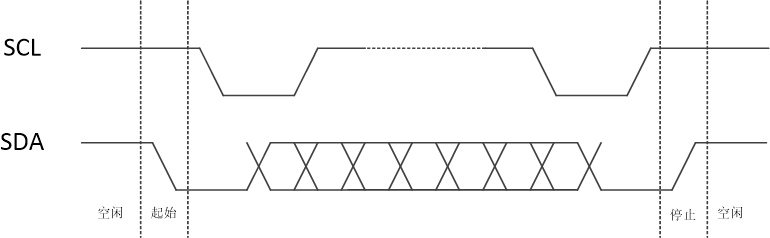

9566 IIC總線是一個雙向的兩線連續總線,它為集成電路之間提供通信線路。其意思是完成集成電路或功能單元之間信息交換的協議。

2023-07-23 11:45:50 28512

28512

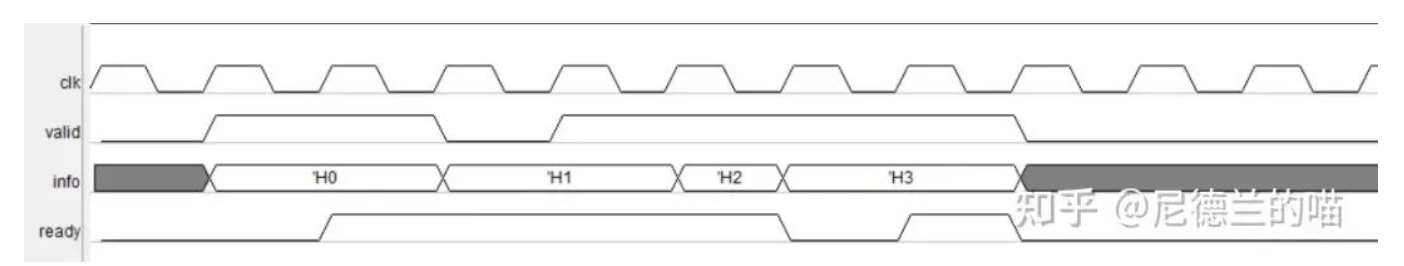

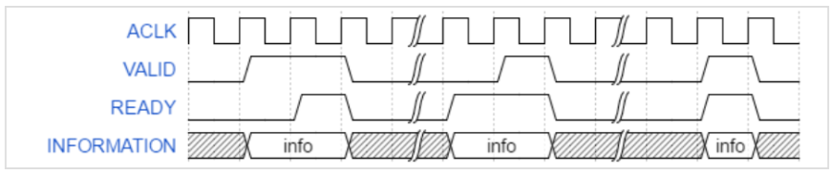

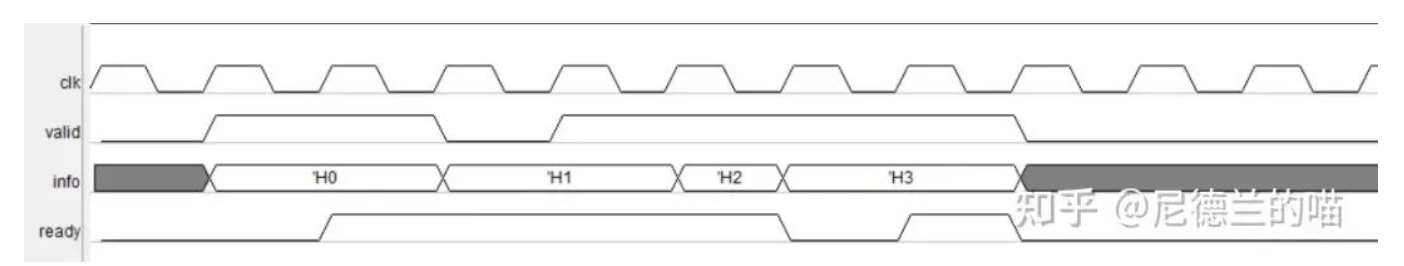

最早接觸到握手協議是在校期間學習PCIe的AXI總線時,至今日雖然PCIe的結構已經忘得一干二凈,但握手協議經過不斷的使用還算掌握的不錯。

2023-12-11 14:11:21 5361

5361

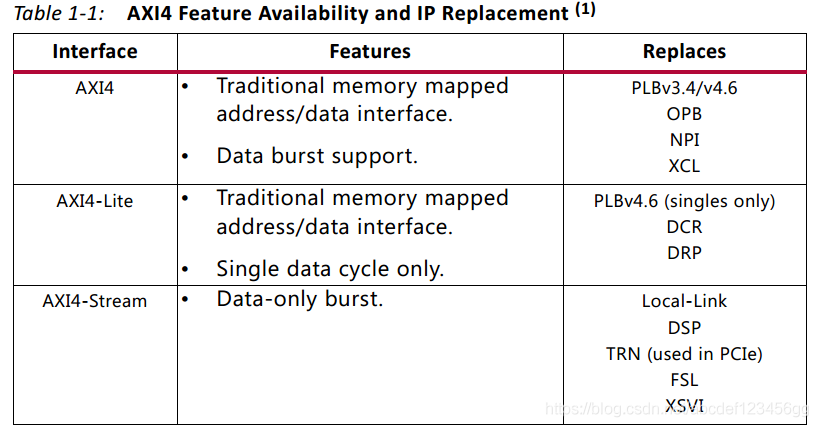

首先我們看一下針對AXI接口的IP設計,在介紹之前我們先回顧一下AXI所具有的一些feature。

2024-02-20 17:12:56 3488

3488

各位大俠, 誰有AXI總線的手冊呀?如果有中文學習記錄+手冊就更完美了。謝謝先

2014-08-05 12:28:25

總線、接口和協議,這三個詞常常被聯系在一起,但是我們心里要明白他們的區別。總線是一組傳輸通道,是各種邏輯器件構成的傳輸數據的通道,一般由由數據線、地址線、控制線等構成。接口是一種連接標準,又常常被稱之為物理接口。協議是傳輸數據的規則。

2021-02-05 07:30:05

AXI總線學習AXI協議的主要特征主要結構通道定義讀寫地址通道讀數據通道寫數據通道寫操作回應信號接口和互聯寄存器片基本傳輸Read burstOverlapping read burstWrite

2022-02-09 07:17:23

什么是AMBA?AMBA分為哪幾種?AXI、AHB與APB的性能有什么不同?AHB總線是如何組成的?APB總線有哪些主要應用?

2021-06-18 06:55:01

1、AXI接口協議詳解 AXI 總線 上面介紹了AMBA總線中的兩種,下面看下我們的主角—AXI,在ZYNQ中有支持三種AXI總線,擁有三種AXI接口,當然用的都是AXI協議。其中三種AXI總線

2022-10-14 15:31:40

AXI 總線上面介紹了AMBA總線中的兩種,下面看下我們的主角—AXI,在ZYNQ中有支持三種AXI總線,擁有三種AXI接口,當然用的都是AXI協議。其中三種AXI總線分別為:AXI

2022-04-08 10:45:31

DMA內部寄存器的讀寫方式基于AXI的DMA對內部寄存器的讀寫有著相同的方式。在普通傳輸模式下,DMA內部的寄存器都是由處理器通過AXI-Lite總線進行讀寫的;但基于AXI總線的三種DMA,都

2022-10-14 15:23:41

市面上主流幾種LED調光協議分析及具體應用場景介紹目前國內外的LED驅動已經不僅僅滿足照明需求,更多是去追求各種不同場景的應用,搭配各種數字協議,實現某種特定的功能,比如在汽車大燈的應用中,未為兼容

2021-12-31 08:04:57

您可以將協議斷言與任何旨在實現AMBA?4 AXI4的接口一起使用?, AXI4 Lite?, 或AXI4流? 協議通過一系列斷言根據協議檢查測試接口的行為。

本指南介紹SystemVerilog

2023-08-10 06:39:57

AXI協議支持高性能、高頻的系統設計,用于

管理器和下屬組件。

AXI協議的特點是:

?適用于高帶寬和低延遲設計。

?在不使用復雜橋梁的情況下提供高頻操作。

?該協議滿足各種組件的接口要求

2023-08-02 09:44:08

本文介紹了AMBA3.0AXI的結構和特點,分析了新的AMBA3.0AXI協議相對于AMBA2.0的優點。它將革新未來高性能SOC總線互連技術,其特點使它更加適合未來的高性能、低延遲設計。最后介紹了基于AXI協議的設計實例,探討了利用IP復用技術和DesginWareIP搭建基于AXI協議的SOC系統。

2023-09-20 08:30:25

AMBA_AXI總線詳解

2014-04-18 11:48:28

1、AXI協議用AxCACHE來控制事務屬性來看看事務屬性(Transaction Attributes),主要是對cache,buffer和memory controller的規定。按照協議,從機

2022-04-08 09:49:47

,AXI 這些。所以咱們花點時間,來好好研究一下這些總線協議都是什么。開始之前,先說一下,ACE 是 AXI Coherency Extensions 的縮寫。顧名思義,ACE 就是 AXI 加上支持

2022-04-07 09:35:17

Arm AMBA協議集中,AXI協議是基于burst的嗎?

2022-09-28 10:21:03

Arm AMBA協議集中,axi如何避免deadlock的,其它總線例如PCI是怎么避免的?

2022-10-20 11:07:56

文章目錄I2c協議和時序I2c介紹I2c硬件連接I2c總線的信號I2c總線寫時序I2c總線讀時序I2c驅動框架I2C子系統軟件框架常用的對象設備驅動對象i2c_client—掛在I2C總線上的I2C

2022-02-10 06:51:12

1AXI4總線協議

AXI4總線協議是由ARM公司提出的一種片內總線協議 ,旨在實現SOC中各模塊之間的高效可靠的數據傳輸和管理。AXI4協議具有高性能、高吞吐量和低延遲等優點,在SOC設計中被

2025-06-02 23:05:19

NVMe需要用AXI總線進行高速傳輸。這里,AXI總線是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)協議中的重要組成部分,主要面向

2025-05-17 10:27:56

AXI 總線是一種高速片內互連總線,其定義于由 ARM 公司推出的 AMBA 協議中,主要用于高性能、高帶寬、低延遲、易集成的片內互連需求。AXI4 總線是第四代 AXI 總線,其定義了三種總線接口

2025-06-24 18:00:11

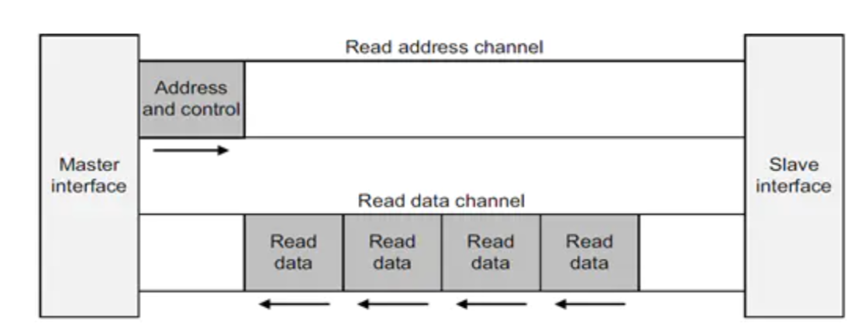

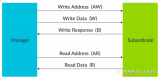

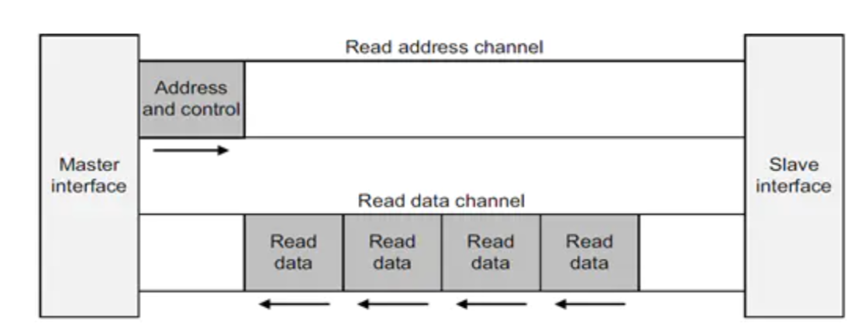

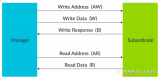

? 這里以功能完備的 AXI4 接口舉例說明 AXI4 總線的相關特點。AXI4 總線采用讀寫通道分離且數據通道與控制通道分離的方式,這樣的總線通道使其具有多主多從的連接特性和并行處理的能力,能夠

2025-06-24 18:02:23

SPI總線協議介紹

2012-08-18 21:26:58

SPI總線協議介紹(接口定義,傳輸時序)

2021-03-03 07:45:16

typora-copy-images-to: typora_picture基于FPGA與MCU通信的SPI協議設計1. SPI總線協議介紹及硬件設計1.1 SPI總線協議介紹及硬件設計SPI總線

2021-11-10 07:06:18

越來越多的芯片集成了這種通信協議。SPI是一個環形總線結構,由ss(cs)、sck、sdi、sdo構成,其時序其實很簡單,主要是在sck的控制下,兩個雙向移位寄存器進行數據交換。 上升沿發送、下降沿

2018-07-06 07:24:25

一.單總線協議時序對應代碼1.延時函數//單總線延時函數,約1~2usvoid Delay_OneWire(unsigned int t){static unsigned char i;while(t--){ for(i=0;i

2022-01-17 08:05:52

Arm AMBA協議集中,axi如何避免deadlock的,其它總線例如PCI是怎么避免的?求大神解答

2022-09-06 11:17:56

`1、在開發zynq工程時遇到多個axi_hp總線讀寫ddr時,總線鎖死。現象就是axi_hp的wready信號一直為低。架構圖: 2、應用write1、wrtie2、read1同時并行讀寫ddr3

2020-04-15 21:57:28

本指南介紹了高級微控制器總線體系結構(AMBA)AXI的主要功能。

該指南解釋了幫助您實現AXI協議的關鍵概念和細節。

在本指南中,我們介紹:

?AMBA是什么。

?為什么AMBA在現代SoC設計中

2023-08-09 07:37:45

介紹參考文檔《玩轉Zynq-基礎篇:AXI總線協議介紹.pdf》。3 AXI GP外設配置在zstar_ex53實例的基礎上,需要對ZYNQ7Processing System(PS)配置頁面做更改

2019-11-12 10:23:42

的邏輯設計。2 AXI總線協議介紹參考文檔《玩轉Zynq-基礎篇:AXI總線協議介紹.pdf》。3Zynq PS的AXI HP配置在ZYNQ7 ProcessingSystem中,點擊左側Page

2019-11-26 09:47:20

不同通道使用情況下的數據吞吐量。大家可以在此基礎上,更改不同的AXI HP總線時鐘頻率,以評估時鐘頻率對AXI HP總線的影響。2 AXI總線協議介紹參考文檔《玩轉Zynq-基礎篇:AXI總線協議介紹

2019-11-28 10:11:38

`玩轉Zynq連載3——AXI總線協議介紹1 更多資料共享 鏈接:https://share.weiyun.com/5s6bA0s 1 AXI協議簡介AMBA AXI(Advanced

2019-05-06 16:55:32

不做過多的講解(小伙伴可以自行下載AMBA總線協議規范或者翻看網絡上AXI4總線協議相關文章)。在SpinalHDL中,關于Axi4總線,包含了配置和實現兩塊內容,其內容均在

2022-08-02 14:28:46

目的是利用嵌入在Xilinx FPGA中的MicroBlaze核實現基于AXI總線的雙核嵌入式系統設計以及共享實現LED燈的時控.

2012-03-09 14:17:01 91

91 AMBA AXI 總線學習筆記,非常詳細的AXI總線操作說明

2015-11-11 16:49:33 12

12 詳細介紹AXI總線

2017-02-28 21:03:54 1

1 AXI總線的MicroBlaze雙核SoPC系統設計

2017-10-31 08:54:44 8

8 基于AXI4Stream總線協議,在Xilinx公司提供的FPGA上實現了一個具有缺陷像素校正、色彩濾波陣列插值、圖像降噪實時圖像采集與顯示功能的視頻系統。AXI4Stream總線協議由ARM公司

2017-11-17 08:58:01 5345

5345 1、AXI 總線通道,總線和引腳的介紹 AXI接口具有五個獨立的通道: (1)寫地址通道(AW):write address channel (2)寫數據通道( W): write data

2018-01-05 08:13:47 11271

11271

AXI-4 Memory Mapped也被稱之為AXI-4 Full,它是AXI4接口協議的基礎,其他AXI4接口是該接口的變形。總體而言,AXI-4 Memory Mapped由五個通道構成,如下圖所示:寫地址通道、寫數據通道、寫響應通道、讀地址通道和讀數據通道。

2020-09-23 11:20:23 6924

6924

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現,不能直接和PS相連,必須通過AXI-Lite或

2020-09-24 09:50:30 7203

7203

不同類型的DMA GPIO PL general purpose AXI GP AXI utlilizing PS DMAC High performance w/DMA ACP w/DMA 幾種

2020-10-09 18:05:57 8939

8939

ZYNQ中DMA與AXI4總線 為什么在ZYNQ中DMA和AXI聯系這么密切?通過上面的介紹我們知道ZYNQ中基本是以AXI總線完成相關功能的: 圖4?34連接 PS 和 PL 的 AXI 互聯

2020-11-02 11:27:51 5033

5033

在 AMBA 系列之 AXI 總線協議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標準的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯,多 Master,多 Slave的場景

2022-02-08 11:44:02 18240

18240 在介紹AXI之前,先簡單說一下總線、接口以及協議的含義。總線、接口和協議,這三個詞常常被聯系在一起,但是我們心里要明白他們的區別。

2022-02-08 11:38:56 8388

8388

在介紹AXI之前,先簡單說一下總線、接口以及協議的含義。總線、接口和協議,這三個詞常常被聯系在一起,但是我們心里要明白他們的區別。

2021-02-04 06:00:15 10

10 在 AMBA 系列之 AXI 總線協議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標準的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯,多 Master,多 Slave的場景

2021-02-23 06:57:00 45

45 本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當前我對 AXI總線的理解尚談不上深入。但我希望通過一系列文章,讓讀者能和我一起深入探尋 AXI4。

2021-03-17 21:40:29 25

25 AMBA AXI 協議以高性能,高頻系統設計為目標,提供了很多適合高速亞微型系統 互連的特征。

2021-03-28 09:47:04 23

23 本文介紹了AMBA3。0AXI的結構和特點,分析了新的AMBA3。0AXI協議相對于AMBA2。0的優點。它將革新未來高性能SOC總線互連技術,其特點使它更加適合未來的高性能、低延遲設計。

2021-03-29 09:46:43 9

9 為實現片上系統不同P核之間的協議轉換與高效通信,提出一種高效率PLB2AⅪI總線橋設計方案。利用PLB與AXI高性能總線的帶寬優勢,通過引入流水線傳輸和讀寫重疊傳輸機制,將PLB總線協議中的地址

2021-03-30 15:21:33 9

9 電子發燒友網為你提供SPI總線協議介紹(接口定義,傳輸時序)資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-01 08:45:43 25

25 AXI是個什么東西呢,它其實不屬于Zynq,不屬于Xilinx,而是屬于ARM。它是ARM最新的總線接口,以前叫做AMBA,從3.0以后就稱為AXI了。

2021-04-09 17:10:10 7245

7245

本文介紹了AMBA 3.0 AXI的結構和特點,分析了新的AMBA 3.0 AXI協議相對于AMBA 2. 0的優點。它將革新未來高性能SOC總線互連技術,其特點使它更加適合未來的高性能、低延遲

2021-04-12 15:47:39 28

28 學習內容 學習關于AXI總線的信號接口的具體要求(包括不同通道之間的關系,握手機制說明等)和AXI4-Lite的相關信息,在文章后半部分對AXI讀寫時序進行了簡要講解,主要針對ARM公司

2021-04-30 11:22:13 5137

5137

學習內容 近期設計需要用到AXI總線的IP,所以就對應常用的IP進行簡要的說明,本文主要對AXI互聯IP進行介紹。 基礎架構IP 基礎的IP是用于幫助組裝系統的構建塊。基礎架構IP往往是一個通用IP

2021-05-11 14:52:55 7870

7870

學習內容 學習關于AXI總線的信號接口的具體要求(包括不同通道之間的關系,握手機制說明等)和AXI4-Lite的相關信息,在文章后半部分對AXI讀寫時序進行了簡要講解,主要針對ARM公司

2021-06-01 10:57:38 3463

3463

AXI總線學習AXI協議的主要特征主要結構通道定義讀寫地址通道讀數據通道寫數據通道寫操作回應信號接口和互聯寄存器片基本傳輸Read burstOverlapping read burstWrite

2021-12-05 16:21:03 5

5 本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當前我對 AXI總線的理解尚談不上深入。但我希望通過一系列文...

2022-02-07 11:36:33 4

4 XI4-Stream跟AXI4的區別就是AXI4-Stream去除了地址線,這樣就不涉及讀寫數據的概念了,只有簡單的發送與接收說法,減少了延時。由于AXI4-Stream協議(amba4_axi4_stream_v1_0_protocol_spec.pdf)沒有時序圖,

2022-06-23 10:08:47 3052

3052 本文主要介紹關于AXI4-Stream Video 協議和AXI_VDMA的IP核相關內容。為后文完成使用帶有HDMI接口的顯示器構建圖像視頻顯示的測試工程做準備。

2022-07-03 16:11:05 10566

10566 關于AXI總線協議的一些簡單知識,通過閱讀Xilinx的使用指導手冊(UG1037),結合正點原子的ZYNQ視頻進行梳理總結。

2022-07-15 09:16:29 3977

3977 本文主要介紹了AXI通道以及在每個通道下信號的概述。

2022-08-04 10:49:17 12564

12564 AXI (高性能擴展總線接口,Advanced eXtensible Interface)是ARM AMBA 單片機總線系列中的一個協議,是計劃用于高性能、高主頻的系統設計的。AXI協議是被優化

2022-10-10 09:22:22 11273

11273 AXI總線作為一種線,可以掛若干主設備與從設備,如果若干主設備要同時訪問總線,必然會導致總線需要仲裁。本文不涉及細節,只簡單減少原理,一般來說這個東西不需要自己寫,ARM會提供,但是作為設計者要大致知道原理。

2022-11-30 17:04:36 2510

2510 V1.0 ASB、APB是第一代AMBA協議的一部分。主要應用在低帶寬的外設上,如UART、 I2C,它的架構不像AHB總線是多主設備的架構,APB總線的唯一主設備是APB橋(與AXI或APB相連),因此不需要仲裁一些Request/grant信號。

2023-04-14 10:54:54 4694

4694 AMBA AXI協議支持用于主從模塊之間通信的高性能、高頻率系統設計。

2023-05-04 14:35:14 2818

2818

之前文章為大家介紹了AXI的協議與架構,本篇我們接著往下講AXI的讀寫傳輸

內容概括

2023-05-04 14:41:27 3072

3072

AXI 規范描述了兩個接口之間的點對點協議:manager and subordinate接口。

2023-05-05 11:42:40 1323

1323

AXI 協議有幾個關鍵特性,旨在改善數據傳輸和事務的帶寬和延遲

2023-05-06 09:49:45 1795

1795 上文FPGA IP之AXI4協議1_協議構架對協議框架進行了說明,本文對AXI4接口的信號進行說明。

2023-05-24 15:05:46 2767

2767

在zynq開發過程中,AXI總線經常遇到,每次看到AXI總線相關的信號時都一頭霧水,仔細研究一下,將信號分分類,發現其實也不難。

2023-05-25 11:22:54 1790

1790

AXI4協議是ARM的AMBA總線協議重要部分,ARM介紹AXI4總線協議是一種性能高,帶寬高,延遲低的總線協議。

2023-06-19 11:17:42 5678

5678

最近需要用到AXI接口的模塊,xilinx的IP核很多都用到了AXI總線進行數據和指令傳輸。如果有多個設備需要使用AXI協議對AXI接口的BRAM進行讀寫,總線之間該如何進行仲裁,通信?

2023-06-19 15:45:14 14453

14453

從 FPGA 應用角度看看 AMBA 總線中的 AXI4 總線。

2023-06-21 15:21:44 3091

3091

可以看到,在AXI到UART中,是通過寄存器和FIFO進行中介的。因為從AXI總線往里看,其控制的是就是地址上所映射的寄存器。

2023-06-27 10:12:53 7698

7698

本文開源一個FPGA項目:基于AXI總線的DDR3讀寫。之前的一篇文章介紹了DDR3簡單用戶接口的讀寫方式:《DDR3讀寫測試》,如果在某些項目中,我們需要把DDR掛載到AXI總線上,那就要通過MIG IP核提供的AXI接口來讀寫DDR。

2023-09-01 16:20:37 7276

7276

以AXI4為例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有關IP核中,經常見到AXI總線接口,AXI總線又分為三種: ?AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 2142

2142

在介紹AXI之前,先簡單說一下總線、 接口 以及協議的含義 總線、接口和協議,這三個詞常常被聯系在一起,但是我們心里要明白他們的區別。 總線是一組傳輸通道,是各種邏輯器件構成的傳輸數據的通道,一般由

2023-12-16 15:55:01 1879

1879 本文主要集中在AMBA協議中的AXI4協議。之所以選擇AXI4作為講解,是因為這個協議在SoC、IC設計中應用比較廣泛。

2024-01-17 12:21:22 4273

4273

AXI總線由一些核心組成,包括AXI主處理器接口(AXI4)、AXI處理器到協處理器接口(AXI4-Lite)、AXI主外設接口(AXI4)、AXI外設到主處理器接口(AXI4-Lite)等。

2024-04-18 11:41:39 2500

2500 AXI4和AXI3是高級擴展接口(Advanced eXtensible Interface)的兩個不同版本,它們都是用于SoC(System on Chip)設計中的總線協議,用于處理器和其它外設之間的高速數據傳輸。

2024-05-10 11:29:50 13098

13098

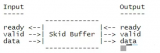

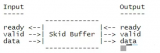

skid buffer(pipeline緩沖器)介紹 ??解決ready/valid兩路握手的時序困難,使路徑流水線化。 ??只關心valid時序參考這篇寫得很好的博客鏈接:?握手協議(pvld

2025-03-08 17:10:51 1105

1105

NVMe需要用AXI總線進行高速傳輸。而AXI總線是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)協議中的重要組成部分,主要面向高性能、高帶寬、低延時的片內互連需求。這里簡要介紹AXI總線區別,以及讀寫架構基本原理

2025-05-21 09:29:51 658

658

電子發燒友App

電子發燒友App

評論