集成電路制造中薄膜生長設(shè)備的類型和作用

薄膜生長設(shè)備作為集成電路制造中實(shí)現(xiàn)材料沉積的核心載體,其技術(shù)演進(jìn)與工藝需求緊密關(guān)聯(lián),各類型設(shè)備通過結(jié)....

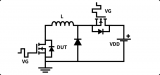

芯片邏輯內(nèi)建自測試技術(shù)的工作原理與核心架構(gòu)

隨著半導(dǎo)體工藝的不斷進(jìn)步,芯片集成度呈指數(shù)級增長,測試成本與測試效率已成為行業(yè)面臨的核心挑戰(zhàn)。傳統(tǒng)依....

集成電路制造中薄膜生長工藝的發(fā)展歷程和分類

薄膜生長是集成電路制造的核心技術(shù),涵蓋PVD、CVD、ALD及外延等路徑。隨技術(shù)節(jié)點(diǎn)演進(jìn),工藝持續(xù)提....

集成電路制造工藝中的刻蝕技術(shù)介紹

本文系統(tǒng)梳理了刻蝕技術(shù)從濕法到等離子體干法的發(fā)展脈絡(luò),解析了物理、化學(xué)及協(xié)同刻蝕機(jī)制差異,闡明設(shè)備與....

拋光設(shè)備的核心自動化配置要求和關(guān)鍵工藝參數(shù)

在半導(dǎo)體器件規(guī)模化量產(chǎn)過程中,拋光設(shè)備的自動化水平直接決定生產(chǎn)效率、工藝穩(wěn)定性與作業(yè)安全性,需同時(shí)滿....

數(shù)字標(biāo)準(zhǔn)單元庫的工藝設(shè)計(jì)套件生成步驟

本文將詳細(xì)介紹數(shù)字標(biāo)準(zhǔn)單元庫的工藝設(shè)計(jì)套件(PDK)生成步驟。

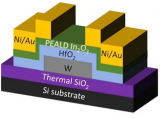

MIT團(tuán)隊(duì)提出一種垂直集成的BEOL堆疊架構(gòu)

近期發(fā)現(xiàn),通過在傳統(tǒng)CMOS芯片的后端工藝(BEOL)層添加額外的有源器件層,可將原本僅用于布線的區(qū)....

一文解讀微機(jī)電系統(tǒng)的基礎(chǔ)知識

微機(jī)電系統(tǒng)(MEMS,Micro-electro-mechanical System,亦稱微系統(tǒng)),....

陽極鍵合工藝的基本原理和關(guān)鍵參數(shù)

直接鍵合方式具備較高的對準(zhǔn)精度與穩(wěn)固的鍵合強(qiáng)度,能滿足高端器件的封裝需求,但該技術(shù)對晶圓表面的平整度....

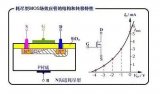

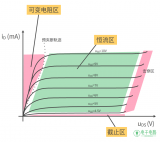

晶體管輸出特性曲線的構(gòu)成與核心區(qū)域

晶體管的輸出特性曲線是半導(dǎo)體器件物理與芯片電路設(shè)計(jì)之間最關(guān)鍵的橋梁。這張圖表描繪了在固定柵極電壓下,....

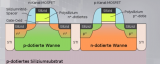

簡單認(rèn)識3D SOI集成電路技術(shù)

在半導(dǎo)體技術(shù)邁向“后摩爾時(shí)代”的進(jìn)程中,3D集成電路(3D IC)憑借垂直堆疊架構(gòu)突破平面縮放限制,....

SOI晶圓片的結(jié)構(gòu)特性及表征技術(shù)

SOI晶圓片結(jié)構(gòu)特性由硅層厚度、BOX層厚度、Si-SiO?界面狀態(tài)及薄膜缺陷與應(yīng)力分布共同決定,其....

淺談SOI晶圓制造技術(shù)的四大成熟工藝體系

SOI晶圓片制造技術(shù)作為半導(dǎo)體領(lǐng)域的核心分支,歷經(jīng)五十年技術(shù)沉淀與產(chǎn)業(yè)迭代,已形成以SIMOX、BS....