文章來源:EETOP

原文作者:EETOP編譯整理

本文主要講述MIT顛覆芯片堆疊挑戰。

近期發現,通過在傳統CMOS芯片的后端工藝(BEOL)層添加額外的有源器件層,可將原本僅用于布線的區域改造為兼具邏輯晶體管與存儲功能的垂直堆疊結構。

這一創新技術通過在芯片后端堆疊多個有源組件,大幅提升了能量利用效率。相關研究成果以兩篇論文的形式在IEEE國際電子器件會議(IEDM)上發布,分別聚焦于BEOL氧化銦晶體管和BEOL納米級鐵電存儲器件的研發與應用。

超越晶體管本身的核心瓶頸

數據中心與邊緣設備的功耗預算中,始終存在著一種架構層面的固有損耗。由于邏輯單元與存儲單元通常是相互獨立的結構,任何依賴存儲狀態的計算步驟都必須迫使數據穿越互連線路和封裝邊界。

這種數據遷移過程既消耗能量又占用時間,而在深度學習、計算機視覺等數據密集型工作負載中,該問題帶來的性能損耗更為顯著。MIT團隊將研究目標定為:通過在緊湊的垂直堆疊結構中實現功能元件的高密度集成,縮短數據傳輸路徑,從而降低遷移損耗。

3D堆疊技術并非全新概念,但在已完成的邏輯層上方進行單片堆疊時,溫度限制成為關鍵制約因素。標準硅基器件制造過程中所需的高溫環境,極易損壞已制備的晶體管和金屬層。MIT團隊的核心創新在于避開了"前端"高溫制備硅基器件的傳統思路,轉而在芯片后端——即傳統上用于布線和金屬鍵合的區域——添加有源層。

這一"反向布局"策略的關鍵價值在于:無需讓底層CMOS電路承受額外的前端高溫工藝,即可將BEOL層轉化為額外的器件承載區域;同時大幅縮短了計算單元、嵌入式存儲與互連線路之間的物理距離,解決了傳統布局中數據傳輸路徑過長導致的能耗浪費問題。

垂直集成的BEOL堆疊架構

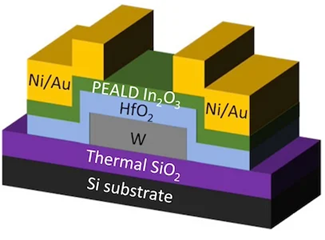

MIT提出的架構方案是在現有電路的后端工藝層上制備垂直集成器件堆疊,在已完成的CMOS電路上方形成新增的有源晶體管層和存儲元件。該堆疊結構的核心使能器件是采用非晶氧化銦溝道層的BEOL晶體管。研究團隊表示,得益于氧化銦的材料特性,他們能夠在約150℃的低溫環境下生長出極薄的功能層,這一溫度足以避免對下方已有電路造成損傷。

圖1:BEOL PEALD氧化銦溝道場效應晶體管(FET)示意圖

制造過程中的核心挑戰在于材料控制。根據工藝描述,該氧化銦薄膜的厚度僅約2納米,其性能表現高度依賴于缺陷管理。氧空位有助于提升溝道導電性,但過量的氧空位會破壞器件的開關特性。研究團隊通過優化制造工藝,將缺陷密度控制在極低水平,使器件能夠實現"快速、潔凈"的開關操作,從而降低了晶體管開關過程中的額外能耗。

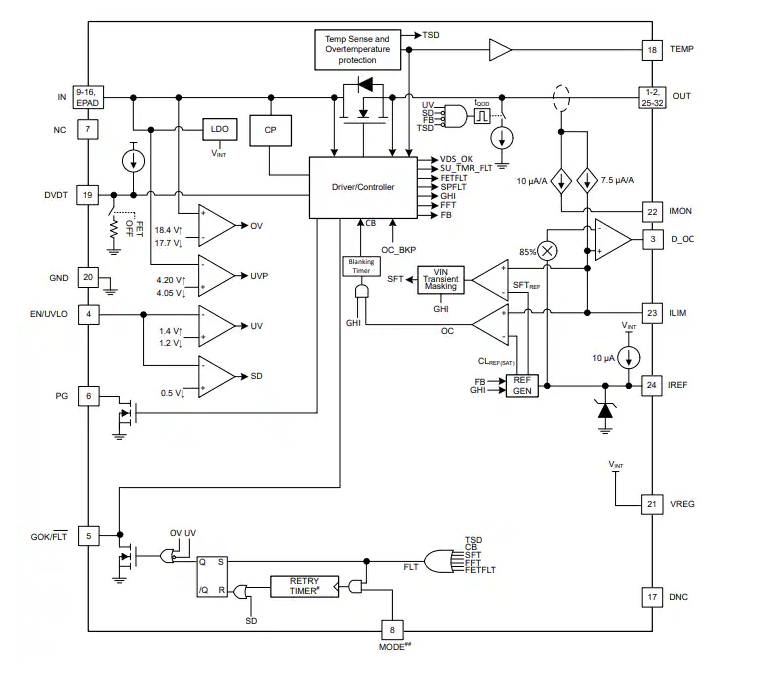

除了邏輯型BEOL器件,研究團隊還通過集成鉿鋯氧化物(HZO)鐵電層,開發出兼具存儲功能的BEOL晶體管。選擇鉿基鐵電材料是基于實際應用考量——鉿氧化物基鐵電材料已在CMOS兼容存儲與計算領域展現出巨大潛力。據報道,該類器件的尺寸達到20納米級別,開關速度可達10納秒(已接近測試設備的測量極限),且工作電壓低于同類型傳統器件。

圖2:BEOL鐵電場效應晶體管(FE-FET)結構示意圖

值得關注的是,該成果并非單一器件演示,而是可擴展的堆疊平臺技術。其中一篇論文聚焦于增強型BEOL氧化銦FET的制備與建模,另一篇則針對BEOL納米級鐵電場效應晶體管的鐵電開關動力學特性展開研究。MIT同時提及與滑鐵盧大學在性能建模方面的合作——這一步驟對于技術從孤立器件向電路級集成的轉化至關重要。

潛在應用場景

MIT的這項研究并非旨在用氧化物電子器件替代先進制程硅基芯片,而是通過在現有芯片的布線區域添加新的功能層,實現垂直集成,從而降低數據密集型計算的能耗成本。最直接的受益場景包括AI推理、深度學習以及需要反復傳輸激活值和權重的視覺處理任務等存儲訪問密集型工作負載。

該技術還具備架構層面的創新價值:BEOL層中兼具存儲功能的晶體管能夠為內存內計算和近內存計算方案提供存儲與計算的緊密耦合。特別是鐵電器件,其在高密度非易失性存儲以及支持神經形態計算的模擬或多電平操作方面已被廣泛研究。MIT強調,將鐵電存儲晶體管縮小至納米尺度,為研究單個鐵電單元的物理特性提供了理想平臺,這一基礎研究成果有望影響未來存儲與計算原語的設計思路。

從短期來看,該研究是工具與材料領域的重要里程碑——它提供了一條低溫、缺陷可控的技術路徑,能夠在已完成的芯片后端集成有源晶體管和存儲元件,且不損傷現有電路。MIT透露,下一步的研究方向將是將BEOL存儲晶體管集成到單一電路中,在提升器件性能的同時,進一步優化對鐵電層特性的控制。

-

芯片

+關注

關注

463文章

54007瀏覽量

465900 -

CMOS

+關注

關注

58文章

6217瀏覽量

242814 -

晶體管

+關注

關注

78文章

10395瀏覽量

147723

原文標題:MIT顛覆芯片堆疊挑戰

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

不同于HBM垂直堆疊,英特爾新型內存ZAM技術采用交錯互連拓撲結構

SK海力士HBS存儲技術,基于垂直導線扇出VFO封裝工藝

簡單認識高帶寬存儲器

Texas Instruments TPS25984B可堆疊電子保險絲數據手冊

國際首創新突破!中國團隊以存算一體排序架構攻克智能硬件加速難題

下一代高速芯片晶體管解制造問題解決了!

芯片晶圓堆疊過程中的邊緣缺陷修整

一種分段氣隙的CLLC變換器平面變壓器設計

一種多模態駕駛場景生成框架UMGen介紹

一種可堆疊和交錯的多相高壓反相降壓-升壓控制器設計

一種高效堆疊負載原型亮相:450W滿載下效率超越95%

MIT團隊提出一種垂直集成的BEOL堆疊架構

MIT團隊提出一種垂直集成的BEOL堆疊架構

評論