文章來(lái)源:學(xué)習(xí)那些事

原文作者:小陳婆婆

本文主要講述SOI晶圓片結(jié)構(gòu)及表征。

SOI晶圓片結(jié)構(gòu)特性由硅層厚度、BOX層厚度、Si-SiO?界面狀態(tài)及薄膜缺陷與應(yīng)力分布共同決定,其厚度調(diào)控范圍覆蓋MEMS應(yīng)用的微米級(jí)至先進(jìn)CMOS的納米級(jí)。

除SIMOX工藝外,BOX層厚度可獨(dú)立調(diào)節(jié)至納米至微米量級(jí),制造工藝通過(guò)表面制備步驟確保頂層硅平滑性——傳統(tǒng)CMP工藝雖能實(shí)現(xiàn)減薄,但材料去除量達(dá)數(shù)十納米易引發(fā)厚度非均勻性;而Eltran工藝采用的氫退火技術(shù)則可將SOI層厚度減少量控制在1nm以內(nèi),同時(shí)實(shí)現(xiàn)原子級(jí)平坦表面,厚度均勻性顯著優(yōu)于CMP工藝。

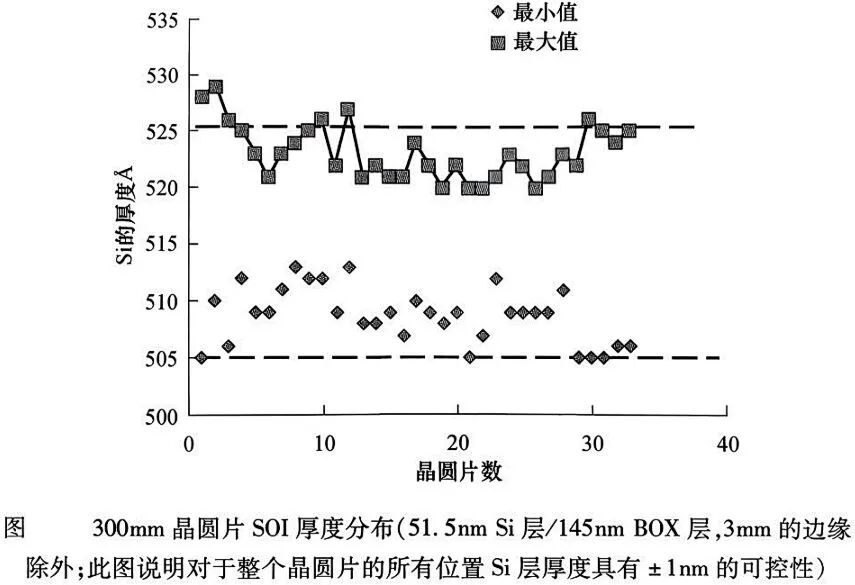

隨著晶圓尺寸向大直徑演進(jìn),20世紀(jì)90年代主流的100mm、150mm、200mm晶圓已逐步被300mm量產(chǎn)取代,450mm晶圓亦完成試產(chǎn)驗(yàn)證。以Smart CutTM工藝制備的300mm SOI晶圓片為例,其硅層厚度控制精度達(dá)±0.5nm,BOX層厚度150nm時(shí),晶圓片內(nèi)及片間厚度波動(dòng)小于1nm,滿足全耗盡SOI技術(shù)的大批量生產(chǎn)需求,這對(duì)測(cè)量技術(shù)提出更高要求——需實(shí)現(xiàn)亞納米級(jí)重復(fù)性與精度以支撐工藝監(jiān)控。

結(jié)構(gòu)表征技術(shù)

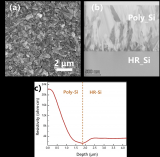

結(jié)構(gòu)表征方面,常規(guī)物理化學(xué)技術(shù)如橢偏儀、X射線衍射/反射、RBS、SIMS、FTIR、TEM及AFM廣泛應(yīng)用于在線/離線檢測(cè),其中AFM在1μm2面積測(cè)得的表面粗糙度有效值通常低于0.15nm。針對(duì)CMOS應(yīng)用對(duì)膜層完整性的嚴(yán)苛要求,行業(yè)開(kāi)發(fā)了專(zhuān)用表征技術(shù):稀釋Secco腐蝕通過(guò)缺陷周?chē)鷳?yīng)力優(yōu)先腐蝕形成腐蝕坑,結(jié)合HF腐蝕暴露埋氧化層缺陷,實(shí)現(xiàn)缺陷密度光學(xué)測(cè)量;KLA-Tencor SP-DLS系統(tǒng)可掃描整個(gè)晶圓片表面,結(jié)合SEM驗(yàn)證缺陷穿透性,使智能剝離工藝制備的300mm SOI晶圓片HF缺陷密度降至0.05個(gè)/cm2以下。界面質(zhì)量表征顯示,低劑量SIMOX晶圓片經(jīng)1320℃退火6小時(shí)后,頂硅-BOX界面呈現(xiàn)粗糙方形鑲嵌圖案,源于氧注入損傷與結(jié)晶硅層混合;延長(zhǎng)退火時(shí)間可促使界面平滑化,形成螺旋/階梯型圖案,階梯高度為硅晶格常數(shù)倍數(shù)。鍵合SOI晶圓片通過(guò)1100℃退火可獲高質(zhì)量頂硅-BOX界面,透射電鏡觀察證實(shí)其結(jié)構(gòu)完整性。

電學(xué)性能表征

電學(xué)性能表征是SOI應(yīng)用的核心,偽MOS晶體管技術(shù)通過(guò)測(cè)量頂層硅摻雜類(lèi)型、載流子遷移率、界面陷阱密度及載流子復(fù)合壽命,補(bǔ)充霍爾效應(yīng)、擴(kuò)展電阻、光電導(dǎo)等標(biāo)準(zhǔn)方法。研究表明,智能剝離工藝制備的SOI晶圓片經(jīng)高溫退火后,氫完全擴(kuò)散,單晶性質(zhì)得以保留,載流子遷移率達(dá)電子650cm2/Vs、空穴240cm2/Vs,界面陷阱密度低于3×1011 eV?1·cm?2,載流子壽命超100μs,優(yōu)于SIMOX工藝。300mm SIMOX與智能剝離SOI晶圓片已證實(shí)具備可靠性與可重復(fù)性,可滿足高性能晶體管及試驗(yàn)器件制造需求,其頂層硅為高質(zhì)量單晶,電學(xué)性能優(yōu)異,埋氧化層與界面質(zhì)量達(dá)應(yīng)用要求。

當(dāng)前,SOI晶圓片表征技術(shù)正朝著更高精度、非破壞性及智能化方向發(fā)展。例如,納米束電子衍射(NBD)可實(shí)現(xiàn)亞納米級(jí)缺陷定位,機(jī)器學(xué)習(xí)算法應(yīng)用于缺陷分類(lèi)與良率預(yù)測(cè),顯著提升檢測(cè)效率。在綠色制造方面,Soitec通過(guò)供體晶圓重復(fù)利用與低能耗沉積工藝,將碳化硅基板生產(chǎn)碳排放降低四倍,契合半導(dǎo)體產(chǎn)業(yè)低碳化趨勢(shì)。

新興應(yīng)用領(lǐng)域如量子計(jì)算中,SOI基硅鍺異質(zhì)結(jié)量子點(diǎn)陣列實(shí)現(xiàn)單量子比特操控保真度99.9%;5G/6G通信中,SOI基射頻器件插入損耗較傳統(tǒng)硅基器件降低30%,成為毫米波前端模塊首選方案。這些進(jìn)展共同推動(dòng)SOI技術(shù)在射頻、功率、光電子及量子計(jì)算等前沿領(lǐng)域的持續(xù)創(chuàng)新與價(jià)值重構(gòu)。

-

SOI

+關(guān)注

關(guān)注

4文章

83瀏覽量

18464 -

晶圓片

+關(guān)注

關(guān)注

1文章

14瀏覽量

7864

原文標(biāo)題:SOI晶圓片結(jié)構(gòu)及表征

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

什么是晶圓測(cè)試?怎樣進(jìn)行晶圓測(cè)試?

硅晶圓是什么?硅晶圓和晶圓有區(qū)別嗎?

晶圓封裝有哪些優(yōu)缺點(diǎn)?

全球晶圓片廠有哪些_全球十大晶圓片廠排名

制備出國(guó)際一流的SOI晶圓片 王曦發(fā)布豪杰壯語(yǔ)

Soitec與三星晶圓代工廠擴(kuò)大合作 保障FD-SOI晶圓供應(yīng)

SOI晶圓目前的發(fā)展現(xiàn)況與未來(lái)規(guī)劃

環(huán)球晶圓將為格芯供應(yīng)12英寸的SOI晶圓

上海微系統(tǒng)所在300mm RF-SOI晶圓制造技術(shù)方面實(shí)現(xiàn)突破

國(guó)內(nèi)第一片300mm射頻(RF)SOI晶圓的關(guān)鍵技術(shù)

淺談SOI晶圓制造技術(shù)的四大成熟工藝體系

SOI晶圓片的結(jié)構(gòu)特性及表征技術(shù)

SOI晶圓片的結(jié)構(gòu)特性及表征技術(shù)

評(píng)論