文章來源:Jeff的芯片世界

原文作者:Jeff的芯片世界

本文介紹了自對準硅化物工藝的特點、優勢、以及挑戰。

什么是Salicide

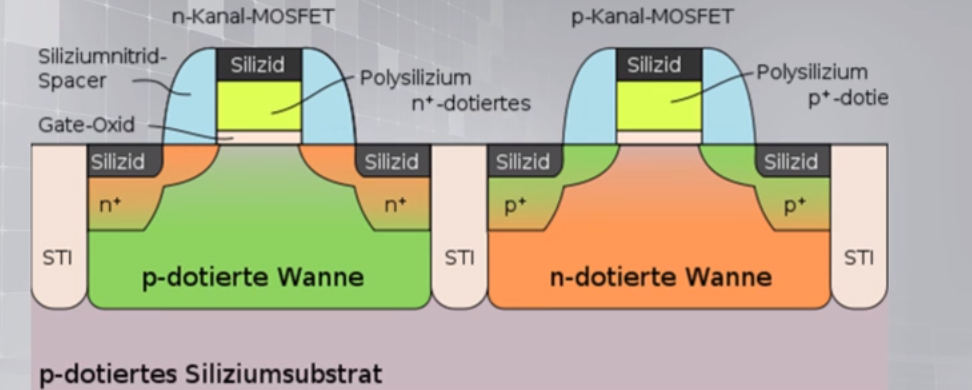

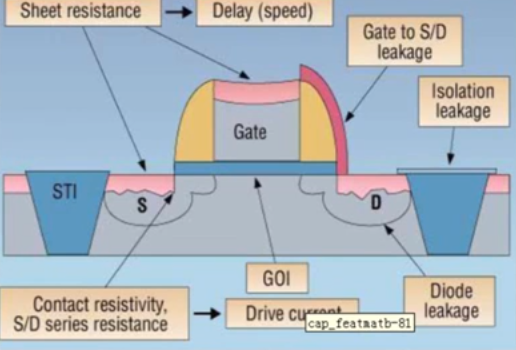

Salicide(Self-Aligned Silicide,自對準硅化物)是一種通過選擇性金屬沉積與硅反應,在半導體器件的源/漏極(Source/Drain)和柵極(Poly Gate)表面形成低電阻金屬硅化物的工藝。其核心在于“自對準”特性:無需額外光刻步驟,僅通過阻擋層(如SAB,Salicide Block)控制硅化物形成區域,從而簡化流程并提高精度。

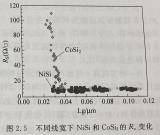

早期工藝采用TiSi?(硅化鈦),但其窄線條效應導致電阻率上升,逐漸被CoSi?(硅化鈷)取代。隨著制程微縮至90nm以下,NiSi(硅化鎳)因更低電阻、更少硅消耗及低溫工藝優勢成為主流。例如,NiSi在30nm線寬下仍能保持低電阻,而CoSi?在40nm以下電阻急劇升高。

硅化物通過減少多晶硅和單晶硅的接觸電阻(Contact Resistance)及薄層電阻(Sheet Resistance),顯著提升器件速度。以0.15μm CMOS工藝為例,TiSi?工藝可將柵極和源/漏極的方塊電阻降至45Ω/□,使環形振蕩器延遲縮短至1.9 ps。

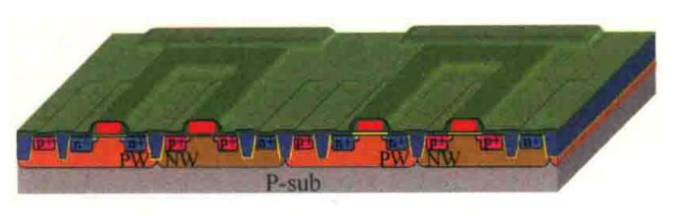

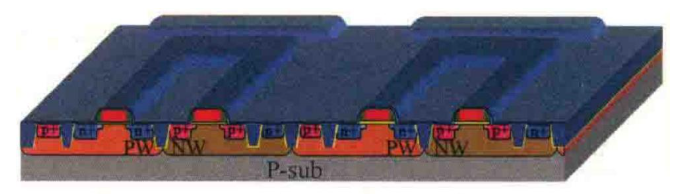

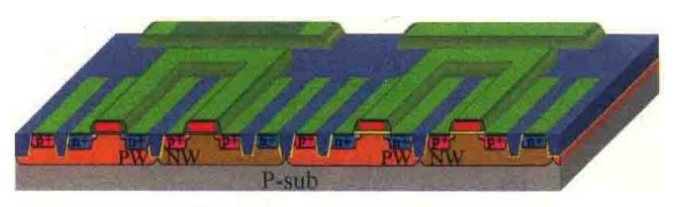

Salicide工藝的制造流程

1. 阻擋層(SAB)的沉積與圖形化

通過PECVD(等離子體增強化學氣相沉積)在晶圓表面覆蓋SiO?阻擋層,并利用光刻技術定義非硅化物區域。例如,SAB光刻需與有源區(AA)嚴格對準,避免后續金屬硅化物在非目標區域形成,導致短路。

2. 金屬沉積與退火反應

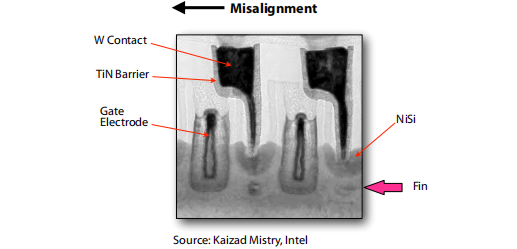

采用PVD(物理氣相沉積)濺射鈷(Co)或鎳(Ni)等金屬,覆蓋TiN作為抗氧化層。隨后進行兩步快速熱退火(RTA):

第一步RTA(約550°C):形成高阻態硅化物(如Co?Si);

第二步RTA(約850°C):轉化為低阻態硅化物(如CoSi?或NiSi)。

此過程需精準控制溫度,防止硅化物橫向過度生長引發柵漏短路。

3. 選擇性刻蝕與后處理

通過濕法刻蝕(如NH?OH+H?O?)去除未反應的金屬和TiN層,并清洗殘留氧化物。最后沉積SiON保護層,防止后續工藝中硼磷雜質擴散影響器件性能。

Salicide工藝的優勢與技術挑戰

1. 性能提升的核心貢獻

降低電阻:源/漏極接觸電阻降低30%-50%,柵極電阻減少至傳統工藝的1/5,顯著縮短RC延遲。

提升集成度:自對準特性避免光刻對準誤差,支持更小線寬設計,例如0.18μm工藝中CoSi?取代TiSi?,突破窄線條效應限制。

2. 工藝中的關鍵挑戰

ESD防護能力下降:低阻硅化物成為ESD電流優先路徑,大電流導致局部高溫燒毀器件。解決方案包括引入SAB工藝形成非硅化區域,或通過ESD IMP(注入工藝)調整擊穿電壓。

熱穩定性問題:NiSi在600°C以上會相變為高阻態NiSi?,需采用尖峰退火(Spike Anneal)或毫秒級退火(MSA)優化熱預算。

Salicide在先進制程中的應用與未來

1. 當前主流應用場景

邏輯芯片:90nm以下CMOS工藝中,NiSi廣泛用于CPU和GPU,支持高頻運算;

存儲器:DRAM和閃存通過Salicide降低位線電阻,提升讀寫速度。

2. 未來技術演進方向

新型材料探索:鉑(Pt)或稀土金屬硅化物因更高熱穩定性進入研究視野;

3D集成兼容性:FinFET和GAA結構中,需開發低溫激光退火工藝,避免多層堆疊的熱應力損傷。

Salicide工藝是半導體微縮化進程中不可或缺的技術,其自對準特性與材料創新持續推動器件性能突破。然而,ESD防護、熱穩定性等問題仍需跨學科協作攻克。

-

半導體

+關注

關注

339文章

30725瀏覽量

264041 -

晶圓

+關注

關注

53文章

5408瀏覽量

132280 -

工藝技術

+關注

關注

0文章

21瀏覽量

9772

原文標題:Salicide工藝技術介紹

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

半導體制造的合金化熱處理工藝

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

雙面柔性PCB板制造工藝及流程

揭秘十一道獨門芯片工藝流程

芯片制造工藝流程步驟

集成電路芯片制造中的3種硅化物工藝介紹

自對準硅化物 (Self -Aligned Silicide) 工藝

IBC技術新突破:基于物理氣相沉積(PVD)的自對準背接觸SABC太陽能電池開發

Salicide自對準硅化物工藝的定義和制造流程

Salicide自對準硅化物工藝的定義和制造流程

評論