文章來源:半導體與物理

原文作者:jjfly686

本文介紹了晶體管的輸出特性曲線的構成、意義、影響與調整措施。

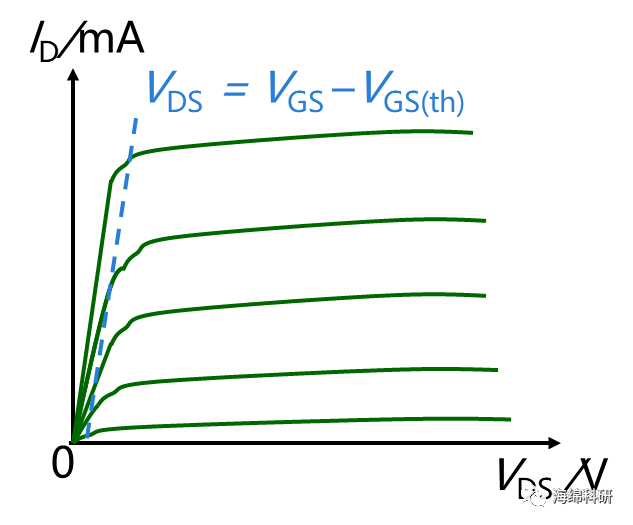

晶體管的輸出特性曲線是半導體器件物理與芯片電路設計之間最關鍵的橋梁。這張圖表描繪了在固定柵極電壓下,晶體管的漏極電流如何隨漏源電壓變化,它本質上是一張揭示晶體管作為電子開關或放大器工作能力的“性能儀表盤”。對于芯片工程師而言,理解曲線上的每一個細節,不僅關乎單個器件的性能,更直接影響著處理器的速度、能效和最終成敗。

輸出特性曲線的構成與核心區域

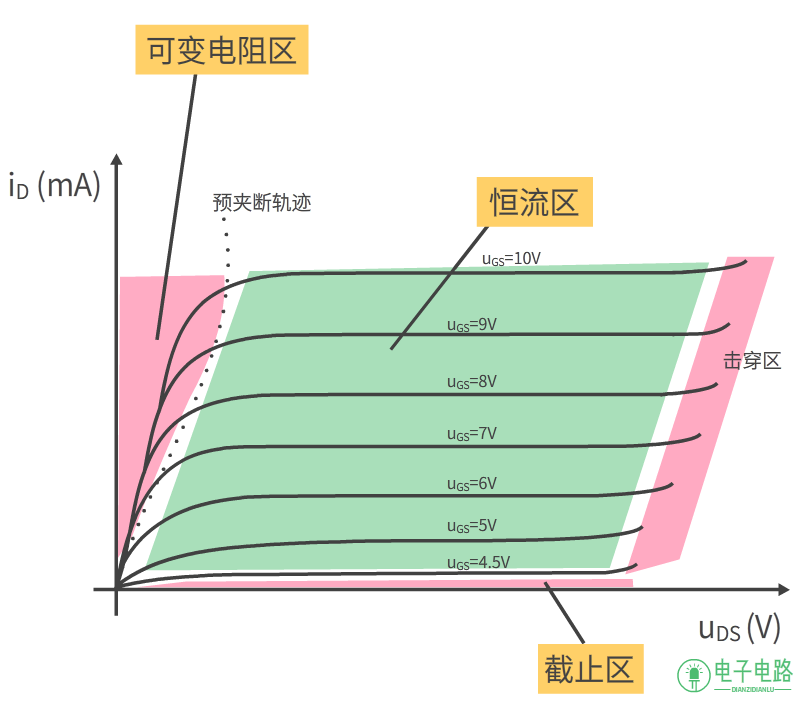

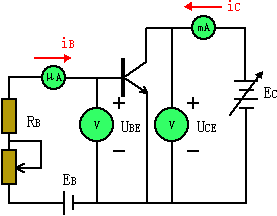

典型的輸出特性曲線呈現為一族曲線。每一條曲線對應一個特定的柵極電壓值。當柵壓從零逐漸增大時,曲線從靠近橫軸的位置逐級向上移動,直觀展示了柵壓對電流的強大控制力。

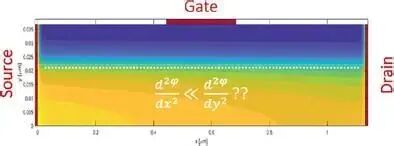

曲線主要分為兩個特征鮮明的區域。第一個區域是線性區,當漏源電壓較小時,漏極電流與之呈近似線性增長關系。此時晶體管溝道完整,其行為類似于一個受柵壓控制的可變電阻。第二個區域是飽和區,當漏源電壓超過某個臨界值后,電流增長趨勢急劇放緩,曲線變得平坦。這是因為溝道在漏極一端被“夾斷”,電流大小主要取決于柵極電壓所形成的溝道導電能力,而對漏源電壓的變化不再敏感。飽和區是晶體管用于放大信號和實現穩定數字開關的核心工作區。

曲線關鍵參數的意義與電路影響

特性曲線上幾個特定的參數點,為工程師提供了量化的性能標尺。

閾值電壓是晶體管從“關斷”到“開啟”的臨界柵極電壓。它決定了芯片的靜態功耗和動態性能的平衡點。在曲線上,它對應于能夠產生第一條可觀測電流曲線的柵壓值。閾值電壓過低會導致關態漏電過大,過高則會使晶體管開啟困難,影響工作速度。

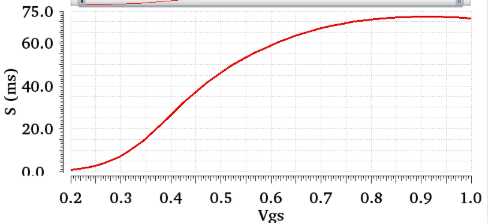

跨導衡量柵極電壓控制漏極電流的效率,定義為漏極電流變化量與柵極電壓變化量的比值。在曲線族上,它直接表現為不同柵壓曲線之間的垂直間距。間距越大、越均勻,意味著跨導越高,晶體管的放大能力和開關電流的驅動能力就越強。

飽和電流是指在給定柵壓下,晶體管進入飽和區后所能提供的最大電流。它對應著每條曲線平坦部分的電流高度。這個參數直接決定了邏輯門驅動后續負載的快慢,以及芯片在最高性能下所需的供電能力。

輸出電阻描述了在飽和區,漏極電流對漏源電壓變化的敏感性。在理想情況下,飽和區曲線應完全水平,輸出電阻無窮大。在實際曲線中,它表現為飽和區曲線略微上翹的斜率。輸出電阻越大,意味著晶體管作為恒流源或放大器的性能越穩定,電壓增益也越高。

飽和電壓是使晶體管從線性區進入飽和區所需的最小漏源電壓。它是每條曲線拐點所對應的電壓值。更低的飽和電壓意味著晶體管能在更低的電源電壓下高效工作,這對于降低芯片整體功耗至關重要。

制造工藝如何塑造特性曲線

芯片制造工藝的每一次微調,本質上都是在重繪晶體管的輸出特性曲線。關鍵工藝參數通過以下方式直接影響電氣性能:

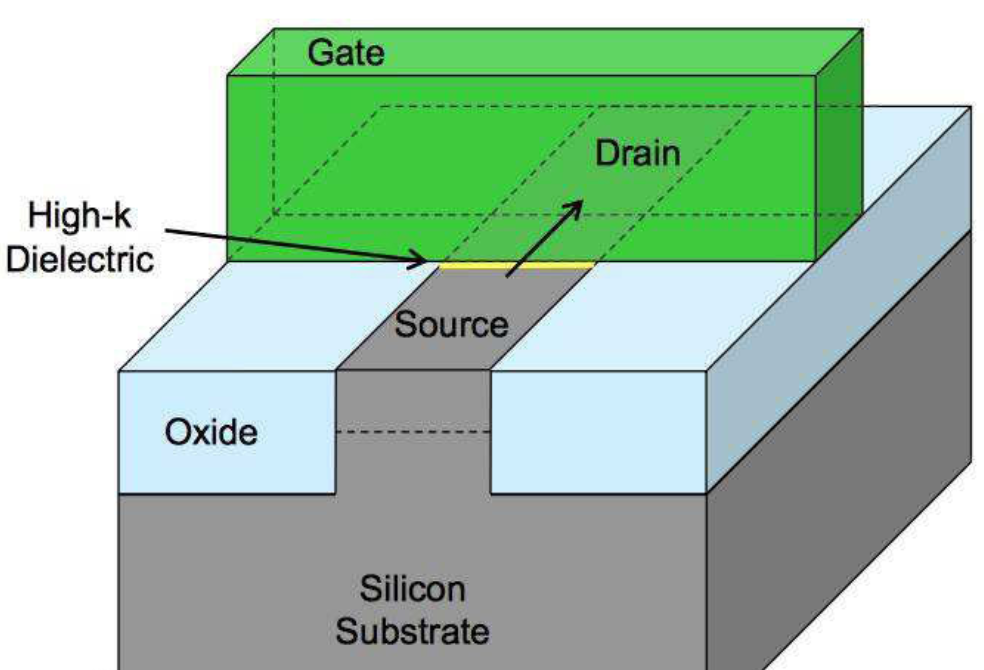

柵氧厚度的變化是對曲線影響最劇烈的因素之一。柵氧層作為柵極控制溝道的介質屏障,其厚度的減小會顯著增大柵電容,從而大幅提升跨導和飽和電流,使整個曲線族向上、向左移動(性能提升,工作電壓降低)。然而,柵氧過薄會引發嚴重的量子隧穿漏電,并威脅可靠性。在先進制程中,通過引入高介電常數介質,可以在維持物理厚度的前提下實現電學上的等效薄化。

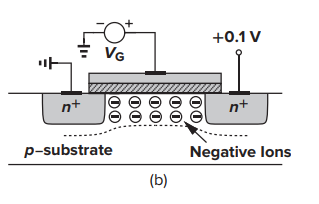

溝道摻雜濃度是精確調控閾值電壓的主要手段。通過離子注入技術提高溝道摻雜濃度,需要更強的柵電場才能開啟晶體管,因此閾值電壓會隨之升高。工程師通過精確的摻雜設計,為芯片中不同功能的晶體管(如高速核心晶體管與低漏電外圍晶體管)設定不同的閾值電壓,以實現全局性能與功耗的最優平衡。

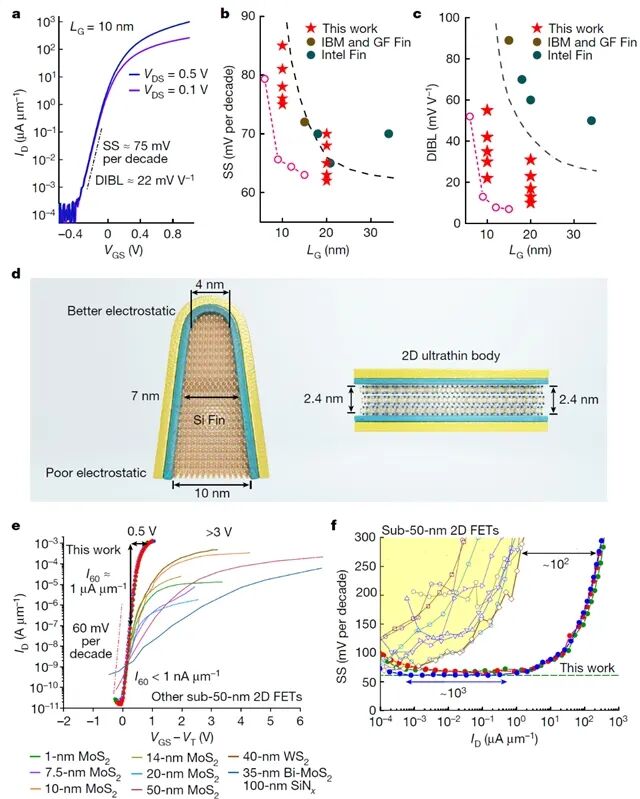

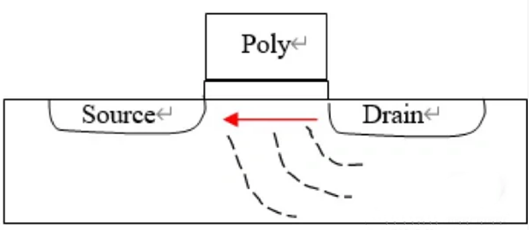

溝道長度的縮短是驅動芯片性能代際提升的核心。縮短溝道能直接減少載流子渡越時間,從而提升速度。在曲線上,這表現為飽和電流的顯著增加和飽和電壓的降低。但溝道長度微縮到一定程度會引發短溝道效應,導致閾值電壓下降、關態漏電激增,并使飽和區曲線傾斜加劇(輸出電阻惡化)。為此,工業界發展出鰭式場效應晶體管和全環繞柵極晶體管等三維結構,來加強對溝道的控制。

溝道寬度的增加能等比例提升晶體管的飽和電流,這常用于設計需要大驅動能力的輸入輸出電路。此外,應變硅技術通過引入鍺硅或應力襯墊來改變硅晶格常數,從而提高載流子遷移率。這項技術能同時提升跨導和飽和電流,卻不增加關態漏電,是提升性能的“免費午餐”,在現代工藝中被廣泛采用。

-

放大器

+關注

關注

146文章

14356瀏覽量

222402 -

晶體管

+關注

關注

78文章

10431瀏覽量

148432 -

輸出特性

+關注

關注

0文章

17瀏覽量

7445

原文標題:晶體管輸出特性曲線

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

晶體管輸出特性曲線的構成與核心區域

晶體管輸出特性曲線的構成與核心區域

評論