文章來(lái)源:Jeff的芯片世界

原文作者:Jeff的芯片世界

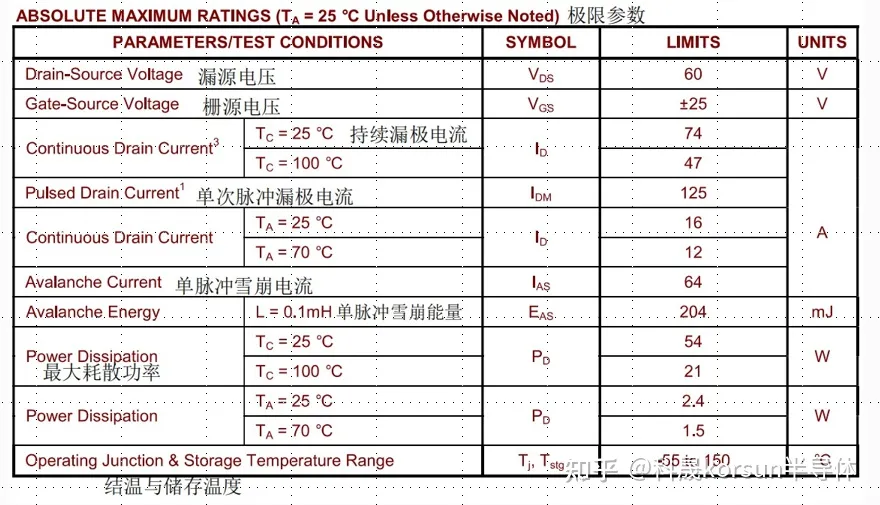

在功率MOSFET器件的設(shè)計(jì)與選型中,單脈沖雪崩能量(Single Pulse Avalanche Energy, EAS)是一個(gè)至關(guān)重要的參數(shù)。它量化了器件在極端過(guò)壓條件下,單次承受雪崩能量的能力,其單位是焦耳(J)。EAS值越大,意味著器件在遭遇瞬間電壓尖峰時(shí)越不易損壞。

EAS的基本概念與重要性

EAS,全稱為單次雪崩能量,用于衡量MOSFET在漏源(DS)端承受過(guò)壓應(yīng)力的能量耐受極限。該參數(shù)的形象描述來(lái)源于測(cè)試過(guò)程:當(dāng)電壓升高至臨界點(diǎn)后,電流會(huì)迅速崩塌,類似雪崩現(xiàn)象。在器件手冊(cè)中,EAS為設(shè)計(jì)者提供了明確的耐受能力參考,是評(píng)估器件可靠性與電路安全性的關(guān)鍵指標(biāo)之一。

在實(shí)際應(yīng)用中,EAS主要描述單次雪崩事件。器件手冊(cè)中還存在另一個(gè)參數(shù)EAR(可重復(fù)雪崩能量),其限定值通常遠(yuǎn)小于EAS,對(duì)芯片長(zhǎng)期可靠性的影響較小。因此,電路設(shè)計(jì)中應(yīng)重點(diǎn)考慮并避免大能量EAS事件的發(fā)生。

EAS的測(cè)試原理與評(píng)估方法

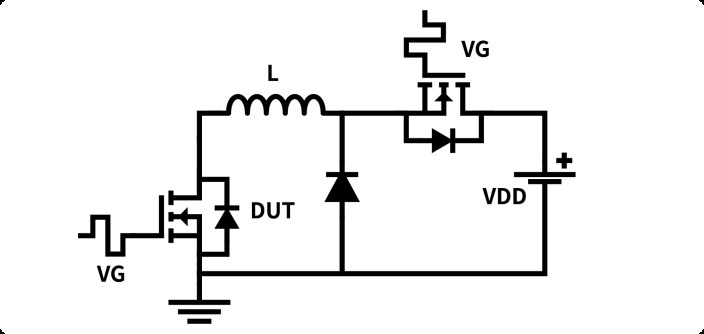

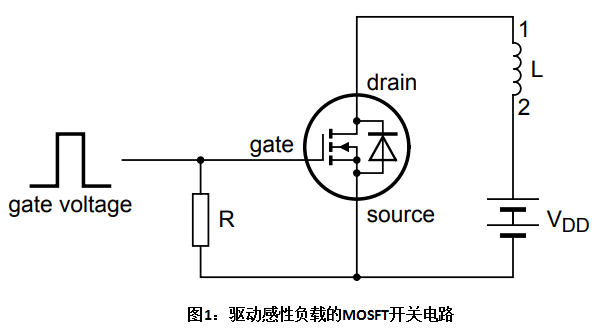

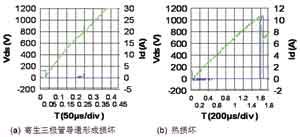

EAS的測(cè)試通常基于感性負(fù)載開關(guān)電路。其基本原理是:通過(guò)柵極信號(hào)控制MOSFET導(dǎo)通,為串聯(lián)的電感充電;關(guān)斷MOSFET時(shí),電感中儲(chǔ)存的能量會(huì)通過(guò)器件釋放,迫使漏源電壓VDS上升并可能超過(guò)其擊穿電壓BV_DSS,進(jìn)入雪崩狀態(tài)。測(cè)試直至器件失效,并根據(jù)失效前的電流等參數(shù)計(jì)算所消耗的能量。

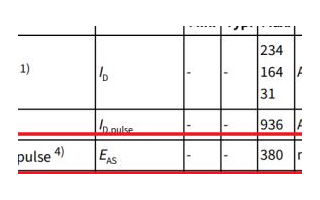

一種典型的測(cè)試方法是:設(shè)定母線電壓V_DD,在柵源極間施加一個(gè)脈沖電壓(如10V)使器件導(dǎo)通,電感電流上升至特定值I_AS后關(guān)斷器件。電感能量釋放導(dǎo)致雪崩,通過(guò)測(cè)量或計(jì)算得到EAS。需要注意的是,準(zhǔn)確的EAS計(jì)算應(yīng)使用實(shí)際測(cè)試中測(cè)得的BV_DSS值,而非直接采用手冊(cè)標(biāo)稱值,且不同廠家的測(cè)試條件可能存在差異,因此不能僅憑規(guī)格書數(shù)值直接比較不同器件的EAS能力。

影響EAS的關(guān)鍵因素

EAS的大小并非固定值,它受到芯片溫度、測(cè)試電路電感及電流等多重因素影響。

1. 溫度的影響:EAS導(dǎo)致?lián)p壞的本質(zhì)是芯片過(guò)熱。芯片的初始結(jié)溫(Tj)直接影響其EAS能力——初始溫度越高,可承受的EAS能量越小。在雪崩過(guò)程中,能量轉(zhuǎn)化為熱量導(dǎo)致溫升,其關(guān)系可表述為:在電流不變的條件下,溫升與吸收的能量成正比。

2. 電感與電流的影響:手冊(cè)中給出的EAS值通常對(duì)應(yīng)特定的測(cè)試電流I_D。EAS能量與電感中儲(chǔ)存的能量直接相關(guān)。根據(jù)能量公式推導(dǎo),在保持溫升和最大雪崩電壓不變的條件下,若電感量增加,為了達(dá)到相同的溫升,所允許的雪崩電流會(huì)減小。綜合來(lái)看,電感量增大數(shù)倍,EAS能量會(huì)增加,但同時(shí)雪崩電流會(huì)減小。

EAS的失效模式與機(jī)理

當(dāng)雪崩能量超過(guò)器件極限時(shí),會(huì)導(dǎo)致破壞性失效,主要模式有兩種。

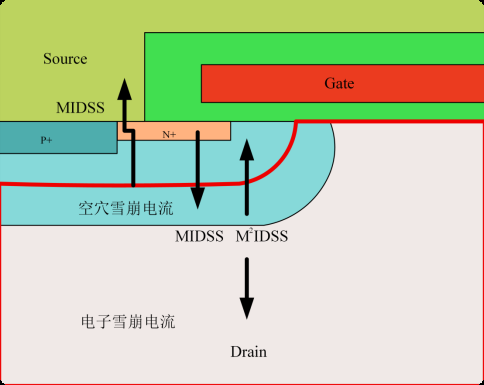

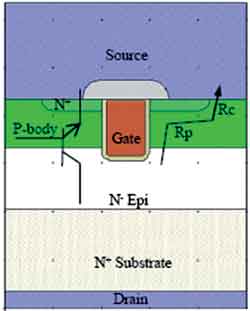

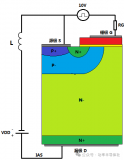

第一種是寄生二極管雪崩燒毀。MOSFET內(nèi)部存在一個(gè)體二極管(寄生二極管)。當(dāng)器件關(guān)斷,感性負(fù)載續(xù)流時(shí),寄生二極管承受反向電壓。若電壓尖峰使其進(jìn)入雪崩擊穿狀態(tài),大電流和高電壓將在芯片內(nèi)部產(chǎn)生大量熱量,若無(wú)法及時(shí)散熱,將導(dǎo)致器件因過(guò)熱而燒毀。

第二種是寄生雙極型晶體管(BJT)開啟。MOSFET結(jié)構(gòu)內(nèi)部還存在一個(gè)由源極、P基區(qū)和N-漂移區(qū)形成的寄生NPN晶體管。正常情況下其處于關(guān)閉狀態(tài)。當(dāng)寄生二極管發(fā)生雪崩擊穿時(shí),流經(jīng)P基區(qū)橫向電阻RB的電流增大,可能導(dǎo)致RB兩端的壓降超過(guò)寄生BJT的開啟電壓(VBE),從而使其導(dǎo)通。一旦寄生BJT開啟,會(huì)形成大電流通道,使MOSFET失效短路。為抑制此失效模式,現(xiàn)代MOSFET設(shè)計(jì)會(huì)致力于減小RB電阻。目前,大多數(shù)EAS失效案例仍以寄生二極管雪崩擊穿過(guò)熱為主。

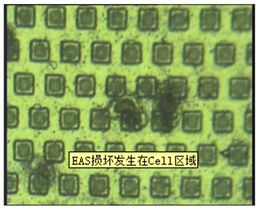

EAS燒毀點(diǎn)常集中在柵極焊盤(PAD)附近。這是因?yàn)榫嚯x柵極越近的元胞,其寄生參數(shù)越小,關(guān)斷速度越快,在雪崩事件中會(huì)先于其他區(qū)域承受應(yīng)力并發(fā)生擊穿。

電路設(shè)計(jì)中的保護(hù)措施

為避免EAS事件損壞器件,可在電路設(shè)計(jì)中采取保護(hù)措施。例如,在變壓器或感性負(fù)載兩端并聯(lián)RCD吸收回路,以箝位和吸收反向尖峰電壓。也可以在MOSFET的漏源極之間并聯(lián)RC吸收電路。此外,適當(dāng)增大柵極串聯(lián)電阻可以減緩關(guān)斷速度(抑制dv/dt),從而降低電壓尖峰,但需權(quán)衡由此增加的關(guān)斷損耗。優(yōu)化PCB布局,加粗大電流路徑并縮短走線,有助于降低線路寄生電感,從根源上減少電壓尖峰能量。

-

開關(guān)電路

+關(guān)注

關(guān)注

62文章

568瀏覽量

68524 -

MOSFET

+關(guān)注

關(guān)注

151文章

9998瀏覽量

234245 -

電路設(shè)計(jì)

+關(guān)注

關(guān)注

6744文章

2719瀏覽量

219851 -

晶體管

+關(guān)注

關(guān)注

78文章

10415瀏覽量

148159

原文標(biāo)題:MOSFET參數(shù)中的EAS是什么?

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

MOSFET規(guī)格書中單脈沖雪崩能量EAS如何理解?電路設(shè)計(jì)咋用它計(jì)算MOS會(huì)損壞嗎?

MOSFET雪崩擊穿圖解 MOSFET避免雪崩失效的方法

功率MOSFET重復(fù)雪崩電流及重復(fù)雪崩能量

MOSFET數(shù)據(jù)表之UIS/雪崩額定值

中文圖解功率MOS管的參數(shù),詳細(xì)實(shí)用資料!

MOSFET雪崩能量的應(yīng)用考慮

MOSFET雪崩能量與器件的熱性能和狀態(tài)相關(guān)性能

功率MOSFET的雪崩強(qiáng)度限值

MOSFET雪崩特性參數(shù)解析

什么是雪崩擊穿?單脈沖雪崩與重復(fù)雪崩有何不同?

MOSFET參數(shù)的理解

功率MOSFET器件的單脈沖雪崩能量參數(shù)解讀

功率MOSFET器件的單脈沖雪崩能量參數(shù)解讀

評(píng)論