文章來源:學(xué)習(xí)那些事

原文作者:小陳婆婆

在此輸入導(dǎo)語本文主要講述3D SOI集成電路概述。

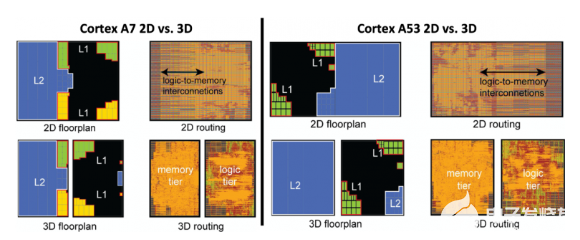

在半導(dǎo)體技術(shù)邁向“后摩爾時(shí)代”的進(jìn)程中,3D集成電路(3D IC)憑借垂直堆疊架構(gòu)突破平面縮放限制,成為提升性能與功能密度的核心路徑。

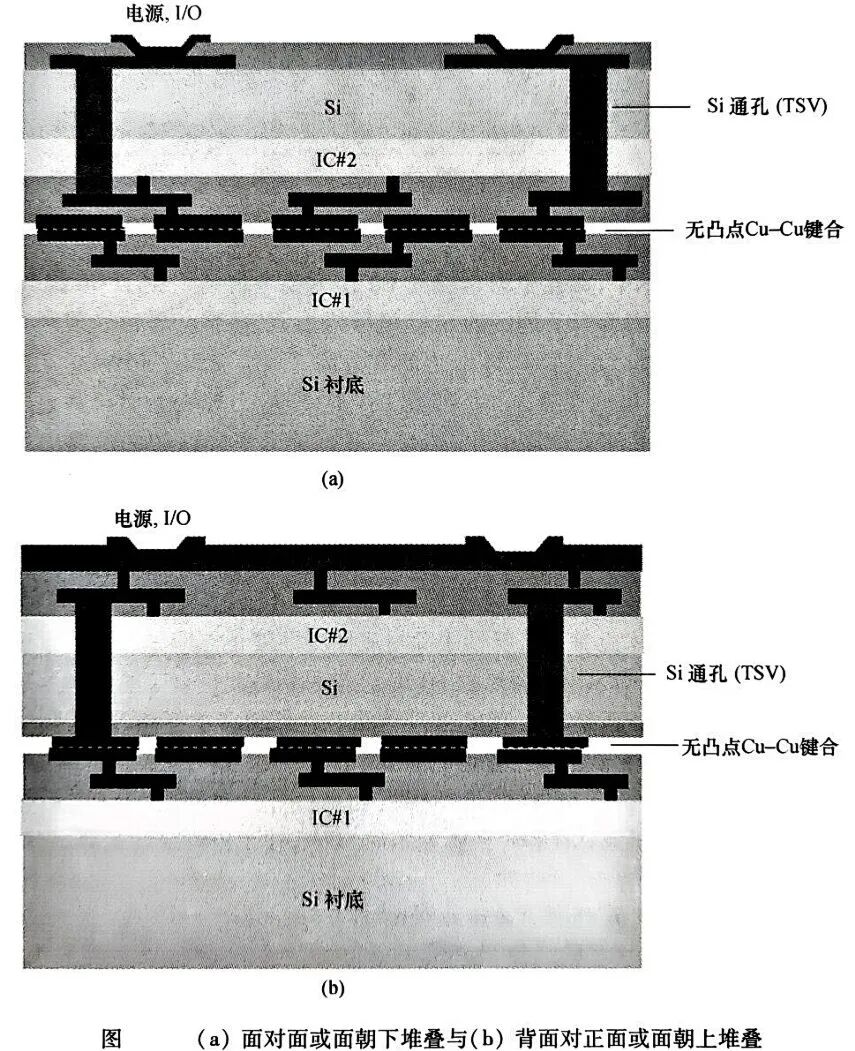

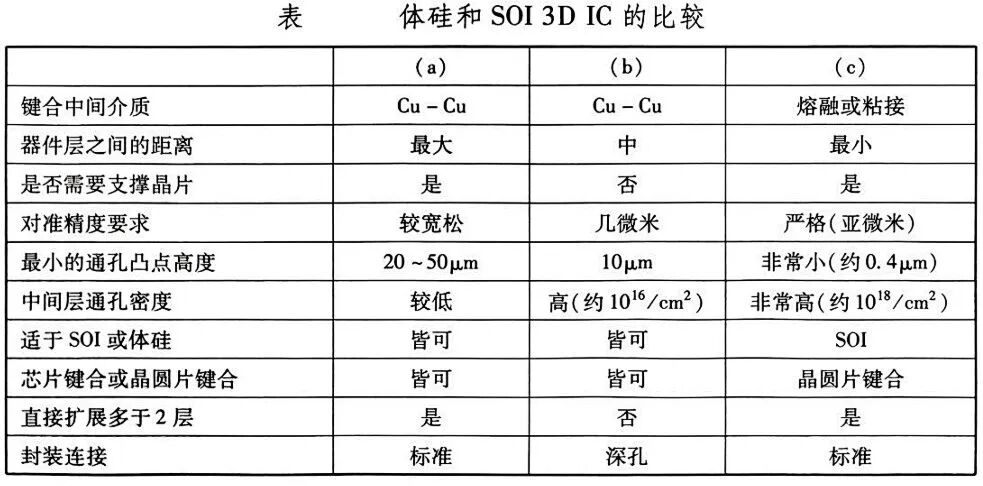

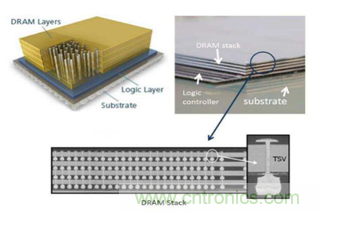

其中,絕緣體上硅(SOI)平臺(tái)因獨(dú)特材料特性與工藝優(yōu)勢(shì),在3D集成領(lǐng)域展現(xiàn)出不可替代的價(jià)值。SOI晶圓通過埋氧化層實(shí)現(xiàn)超薄硅層(厚度可降至亞微米級(jí))的精準(zhǔn)轉(zhuǎn)移與堆疊,規(guī)避了體硅技術(shù)中高深寬比硅通孔(TSV)的工藝瓶頸——傳統(tǒng)體硅需依賴深寬比10:1~20:1的TSV實(shí)現(xiàn)垂直互連,而SOI平臺(tái)可采用深寬比低于5:1的TSV甚至后端工藝兼容的通孔技術(shù),結(jié)合低溫鍵合工藝(如直接Cu-Cu鍵合或絕緣層鍵合),在降低工藝復(fù)雜度與成本的同時(shí),顯著提升互連密度與信號(hào)傳輸速度。

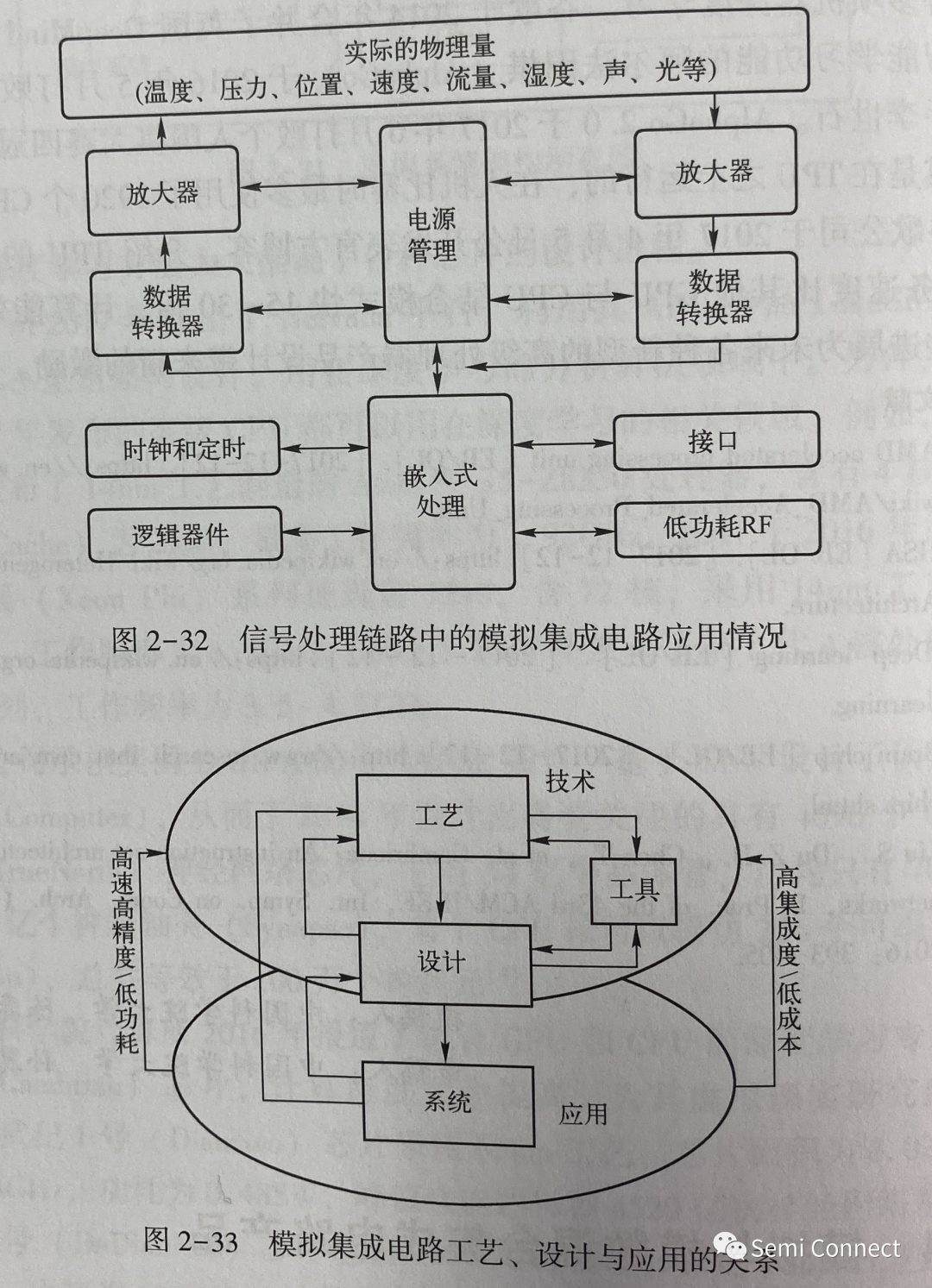

當(dāng)前SOI基3D IC的技術(shù)突破聚焦于材料-工藝-設(shè)計(jì)的全鏈條協(xié)同創(chuàng)新。在材料層面,外延層轉(zhuǎn)移技術(shù)(如ELTRAN)通過多孔硅控制晶圓分裂,實(shí)現(xiàn)硅層厚度均勻性優(yōu)于1%,注氧隔離技術(shù)(SIMOX)結(jié)合高溫退火優(yōu)化散熱與抗輻射性能,鍵合注入結(jié)合技術(shù)(Smart-Cut)則通過離子注入與層轉(zhuǎn)移實(shí)現(xiàn)亞微米級(jí)超薄硅層的精準(zhǔn)制備。

工藝層面,TSV技術(shù)正從后道封裝向前道制造延伸,與FinFET晶體管工藝協(xié)同優(yōu)化——例如采用化學(xué)鍍鎳合金填充工藝將TSV工序縮減至6道,良率提升至98%以上,深反應(yīng)離子刻蝕(DRIE)實(shí)現(xiàn)30-100μm孔徑的高精度加工,配合PECVD沉積0.5-2μm二氧化硅絕緣層與200-500nm阻擋層/種子層,構(gòu)建高可靠性垂直互連結(jié)構(gòu)。

設(shè)計(jì)層面,EDA工具鏈(如新思科技3DIC編譯器)通過跨工藝互聯(lián)規(guī)劃、寄生參數(shù)評(píng)估與熱應(yīng)力預(yù)測(cè),實(shí)現(xiàn)從架構(gòu)探索到簽核的全流程協(xié)同,例如AMD Zen 4處理器采用3D V-Cache技術(shù),通過TSV與微凸點(diǎn)將64MB SRAM緩存堆疊于CPU核心上方,垂直互連距離縮短至傳統(tǒng)2D設(shè)計(jì)的1/10,緩存延遲降低85%至10ns,帶寬提升至1.2TB/s,面積效率提升70%;NVIDIA H100 GPU則集成8層HBM3內(nèi)存,通過TSV實(shí)現(xiàn)3.3TB/s內(nèi)存帶寬,功耗降低30%,支撐AI訓(xùn)練對(duì)超高內(nèi)存帶寬的需求。

應(yīng)用場(chǎng)景方面,SOI基3D IC在高性能計(jì)算、AI、存儲(chǔ)與傳感器領(lǐng)域持續(xù)拓展邊界。在高性能計(jì)算領(lǐng)域,蘋果M1 Ultra通過UltraFusion封裝技術(shù)連接兩個(gè)M1 Max芯片,實(shí)現(xiàn)2.5TB/s芯片間帶寬,GPU核心擴(kuò)展至64核,AI算力達(dá)192 TOPS,能效比提升3倍;Xilinx UltraScale+ FPGA集成3D堆疊的邏輯切片與高速收發(fā)器,TSV密度達(dá)10?個(gè)/cm2,內(nèi)部帶寬提升至1.6TB/s,延遲降低40%,適用于5G基站與AI推理場(chǎng)景。存儲(chǔ)領(lǐng)域,三星HBM4采用12層堆疊與4納米邏輯芯片,結(jié)合TSV技術(shù)實(shí)現(xiàn)單節(jié)點(diǎn)3PB內(nèi)存容量,帶寬達(dá)281GB/s;晶方科技則通過8英寸與12英寸TSV封裝能力,構(gòu)建國(guó)內(nèi)首條300毫米“中道”TSV規(guī)模化量產(chǎn)線,支撐HBM與6G通信封裝需求。傳感器領(lǐng)域,背照式CMOS圖像傳感器通過TSV分離模擬電路與光電二極管,量子效率提升至85%以上,暗電流降低至0.5nA/cm2,索尼IMX989傳感器已實(shí)現(xiàn)1英寸光學(xué)格式。

面向未來,SOI基3D IC的技術(shù)演進(jìn)將圍繞異構(gòu)集成、智能化與國(guó)產(chǎn)化三大方向深化。異構(gòu)集成通過Chiplet架構(gòu)整合不同工藝節(jié)點(diǎn)的邏輯、存儲(chǔ)與RF模塊,平衡成本與性能,例如AMD通過臺(tái)積電CoWoS-S封裝技術(shù)實(shí)現(xiàn)TSV密度10?個(gè)/cm2,支持AI芯片的高帶寬需求。智能化則通過AI輔助設(shè)計(jì)優(yōu)化仿真驗(yàn)證效率,例如華大九天通過關(guān)鍵路徑分析與快速建模工具推動(dòng)設(shè)計(jì)與制造迭代,國(guó)產(chǎn)EDA工具正與國(guó)際標(biāo)準(zhǔn)接軌并依托AI實(shí)現(xiàn)創(chuàng)新突破。國(guó)產(chǎn)化方面,中國(guó)企業(yè)在SOI材料、晶圓鍵合設(shè)備與TSV技術(shù)領(lǐng)域持續(xù)突破——滬硅產(chǎn)業(yè)實(shí)現(xiàn)大尺寸硅片產(chǎn)業(yè)化,超硅半導(dǎo)體推進(jìn)薄層SOI研發(fā);中微公司、北方華創(chuàng)在晶圓鍵合設(shè)備領(lǐng)域取得顯著進(jìn)展,應(yīng)用材料、科磊等國(guó)際巨頭則通過技術(shù)合作與本土企業(yè)協(xié)同創(chuàng)新。

總體而言,SOI基3D IC通過超薄硅層、低深寬比TSV與低溫鍵合技術(shù)的協(xié)同,在性能、功耗與成本方面形成綜合優(yōu)勢(shì),正從實(shí)驗(yàn)室走向規(guī)模化應(yīng)用。SOI平臺(tái)在高性能計(jì)算、存儲(chǔ)擴(kuò)展與異構(gòu)集成領(lǐng)域持續(xù)釋放技術(shù)潛力,成為半導(dǎo)體產(chǎn)業(yè)突破物理極限、實(shí)現(xiàn)自主可控的關(guān)鍵支撐。

-

集成電路

+關(guān)注

關(guān)注

5456文章

12604瀏覽量

374994 -

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

30908瀏覽量

265214 -

TSV

+關(guān)注

關(guān)注

4文章

137瀏覽量

82706

原文標(biāo)題:3D SOI集成電路概述

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

3D集成電路如何實(shí)現(xiàn)

SOI和單片3D集成技術(shù) 芯片成本戰(zhàn)的殺手锏

3D集成電路的結(jié)構(gòu)和優(yōu)勢(shì)

從知識(shí)平臺(tái)角度認(rèn)識(shí)集成電路--知識(shí)平臺(tái)上SOC的高速發(fā)展

SOI和體硅集成電路工藝平臺(tái)互補(bǔ)問題的探討

從知識(shí)平臺(tái)角度認(rèn)識(shí)集成電路

從知識(shí)平臺(tái)認(rèn)識(shí)集成電路

單片型3D芯片集成技術(shù)與TSV的研究

激光直接成型實(shí)現(xiàn)低成本3D集成電路

教你認(rèn)識(shí)如何看懂集成電路的線路圖

集成電路測(cè)試技術(shù)簡(jiǎn)單介紹

硅3D集成技術(shù)全面解析

簡(jiǎn)單認(rèn)識(shí)模擬集成電路

簡(jiǎn)單認(rèn)識(shí)3D SOI集成電路技術(shù)

簡(jiǎn)單認(rèn)識(shí)3D SOI集成電路技術(shù)

評(píng)論