文章來源:學習那些事

原文作者:小陳婆婆

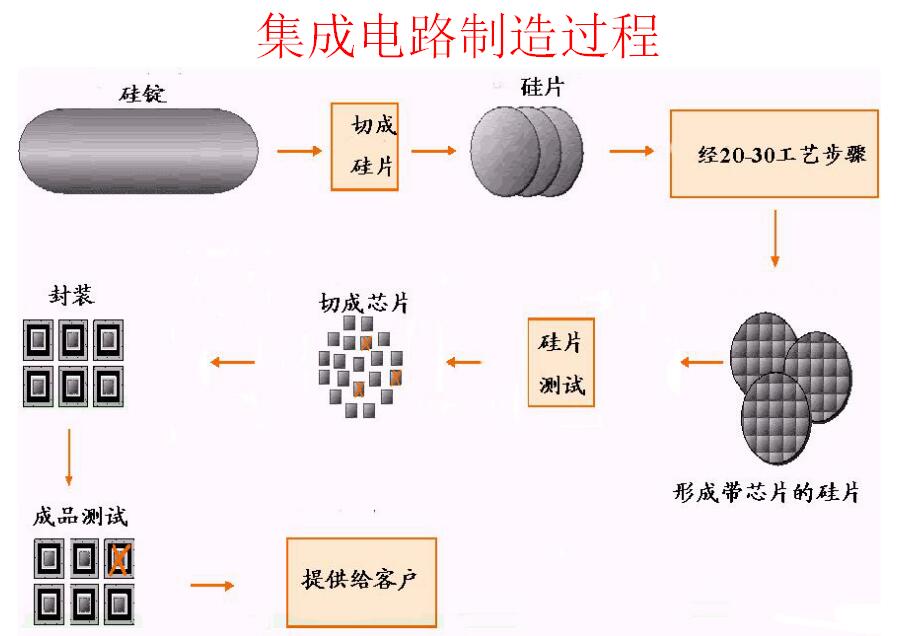

多項目圓片(MPW)與多層光掩模(MLR)顯著降低了掩模費用,而無掩模光刻技術如電子束與激光直寫,在提升分辨率與產能的同時推動原型驗證更經濟高效。刻蝕工藝則向原子級精度發展,支撐先進制程與三維集成,共同助力集成電路研發與應用降本提速。

掩模成本降低

在半導體制造的小批量生產場景中,降低掩模成本的技術創新持續推動原型驗證與教學應用的成本優化。

多項目圓片(MPW)通過將多個設計集成于同一組掩模,顯著分攤了單次流片的掩模成本,成為學術機構與初創企業驗證創新設計的首選路徑。而多層光掩模板(MLR)則通過組合同一產品的多層掩模,減少實際掩模數量,在保持設計獨立性的同時降低物理掩模的制造與存儲成本,尤其適用于工藝開發階段的快速迭代需求。

直寫技術作為無掩模光刻(MLL)的核心載體,正通過電子束與激光束系統的協同進化突破生產率瓶頸。電子束直寫憑借5nm以下的高分辨率,在關鍵層修復、小批量樣品制造中展現不可替代性,而多電子束陣列技術的引入,通過并行寫入大幅提升吞吐量,逐步縮小與傳統光刻的效率差距。激光束直寫則憑借無需真空環境、設備成本低廉的優勢,在非關鍵層圖案化中快速滲透,其通過動態聚焦與智能路徑規劃算法,實現亞微米級線條的精準控制,同時結合導電層沉積技術,有效抑制電子充電效應,保障圖形轉移的保真度。

無掩模光刻的商業化進程在2026年迎來新突破:日本NuFlare推出多電子束直寫系統,通過32束并行寫入實現每小時10片晶圓的產能,良率提升至95%,設備單價控制在2000萬美元以內,較傳統光刻機更具成本優勢。中國在激光直寫領域加速追趕,中科院蘇州納米所研發的激光直寫設備實現8nm線寬,通過智能曝光算法優化,生產率提升30%,已應用于MEMS傳感器與先進封裝基板的制造。此外,無掩模光刻在缺陷控制方面取得進展,通過實時監測與閉環反饋系統,將顆粒污染率降低至0.1%,滿足大批量生產的質量要求。

這些技術不僅降低了小批量生產的門檻,更通過設計制造協同(DFM)工具的深度融合,實現從設計到制造的全流程優化。例如,光刻友好設計通過規則化版圖、固定多晶節距,降低直寫過程中的圖形復雜度,提升生產效率;而EDA平臺集成直寫路徑規劃與缺陷預測功能,實現從設計到制造的無縫銜接。

刻蝕工藝

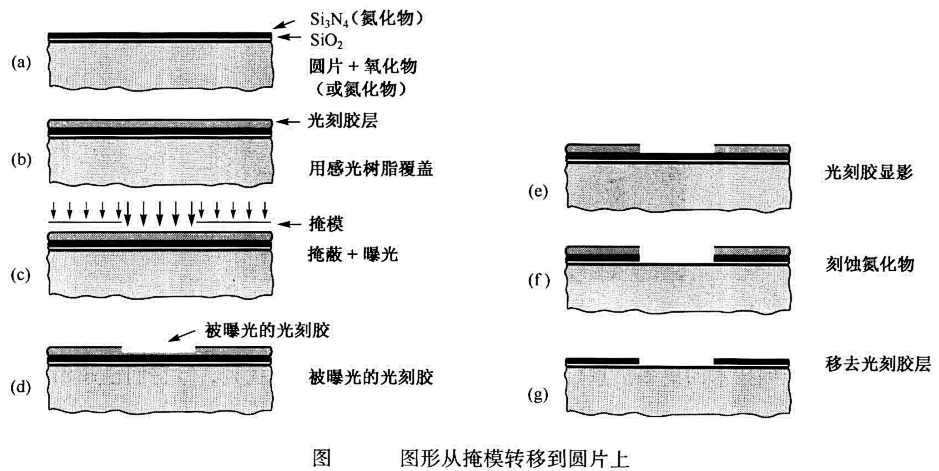

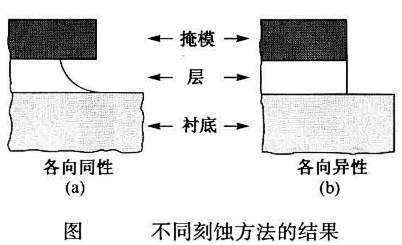

刻蝕工藝作為半導體制造中圖形轉移的關鍵環節,其核心在于實現高精度、高選擇性的各向異性刻蝕,以滿足先進制程對線寬控制、側壁垂直度及材料選擇性的嚴苛要求。

濕法刻蝕雖工藝成熟、成本低廉,但受限于各向同性特性,在亞微米節點下易引發“鉆蝕”問題,導致圖形失真,故逐漸被干法刻蝕替代。

干法刻蝕通過等離子體或離子束實現物理與化學過程的協同,其中反應離子刻蝕(RIE)憑借電場加速的活性離子與表面原子反應生成揮發性產物,在實現高各向異性的同時,通過調整氣體成分(如CHF?等碳質襯底)優化選擇性,減少對下層材料的損傷。高密度等離子(HDP)技術通過感應耦合等離子體源提升等離子密度與電離度,在低壓環境下實現高深寬比結構的精確刻蝕,廣泛應用于淺溝槽隔離(STI)、接觸孔形成等關鍵步驟。

隨著制程節點推進,刻蝕技術持續演進。原子層刻蝕(ALE)通過循環交替的表面修飾與刻蝕步驟,實現單原子層級別的精度控制,有效降低側壁粗糙度與等離子損傷,成為3nm以下節點的重要技術方向。深硅刻蝕(DSE)則通過博世工藝(交替沉積鈍化層與刻蝕)實現高深寬比硅通孔(TSV)的垂直側壁,支撐三維集成與先進封裝需求。此外,針對新型材料(如高k介質、金屬柵)的刻蝕挑戰,業界開發了專用氣體配方與工藝窗口,如采用含氟氣體與氫氣的混合氣體提升對高k材料的選擇性,同時通過實時終點檢測與閉環控制確保工藝一致性。

天線效應與等離子損傷問題在先進制程中尤為突出,工業界通過天線設計規則限制導電區域與柵氧面積的比值,并引入保護二極管、虛擬接地等措施降低電荷積累風險。例如,在邏輯門輸入端并聯保護二極管可有效泄放等離子誘導的電荷,避免柵氧擊穿。同時,工藝優化如低壓刻蝕、脈沖等離子體技術等進一步減少電荷積累與材料損傷,提升器件可靠性。

當前,刻蝕技術正與先進光刻、薄膜沉積等工藝深度協同,推動集成電路向三維集成、異構集成演進。例如,在3D NAND閃存中,深硅刻蝕與原子層沉積(ALD)的組合實現多層堆疊結構的高精度制造;在先進封裝中,刻蝕工藝支撐硅中介層、混合鍵合等技術的實現,提升系統性能與集成度。隨著新材料、新工藝的不斷涌現,刻蝕技術將持續突破物理極限,支撐半導體產業向更小節點、更高性能方向發展,延續摩爾定律的生命力。

-

集成電路

+關注

關注

5452文章

12571瀏覽量

374520 -

半導體

+關注

關注

339文章

30725瀏覽量

264040 -

刻蝕

+關注

關注

2文章

220瀏覽量

13776

原文標題:掩模成本降低與刻蝕技術

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

半導體工藝技術的發展趨勢

半導體工藝技術的發展趨勢是什么?

2020年半導體制造工藝技術前瞻

半導體boe刻蝕技術介紹

半導體刻蝕工藝技術-icp介紹

臺階儀在半導體制造中的應用 | 精準監測溝槽刻蝕工藝的臺階高度

半導體制造中刻蝕工藝技術介紹

半導體制造中刻蝕工藝技術介紹

評論