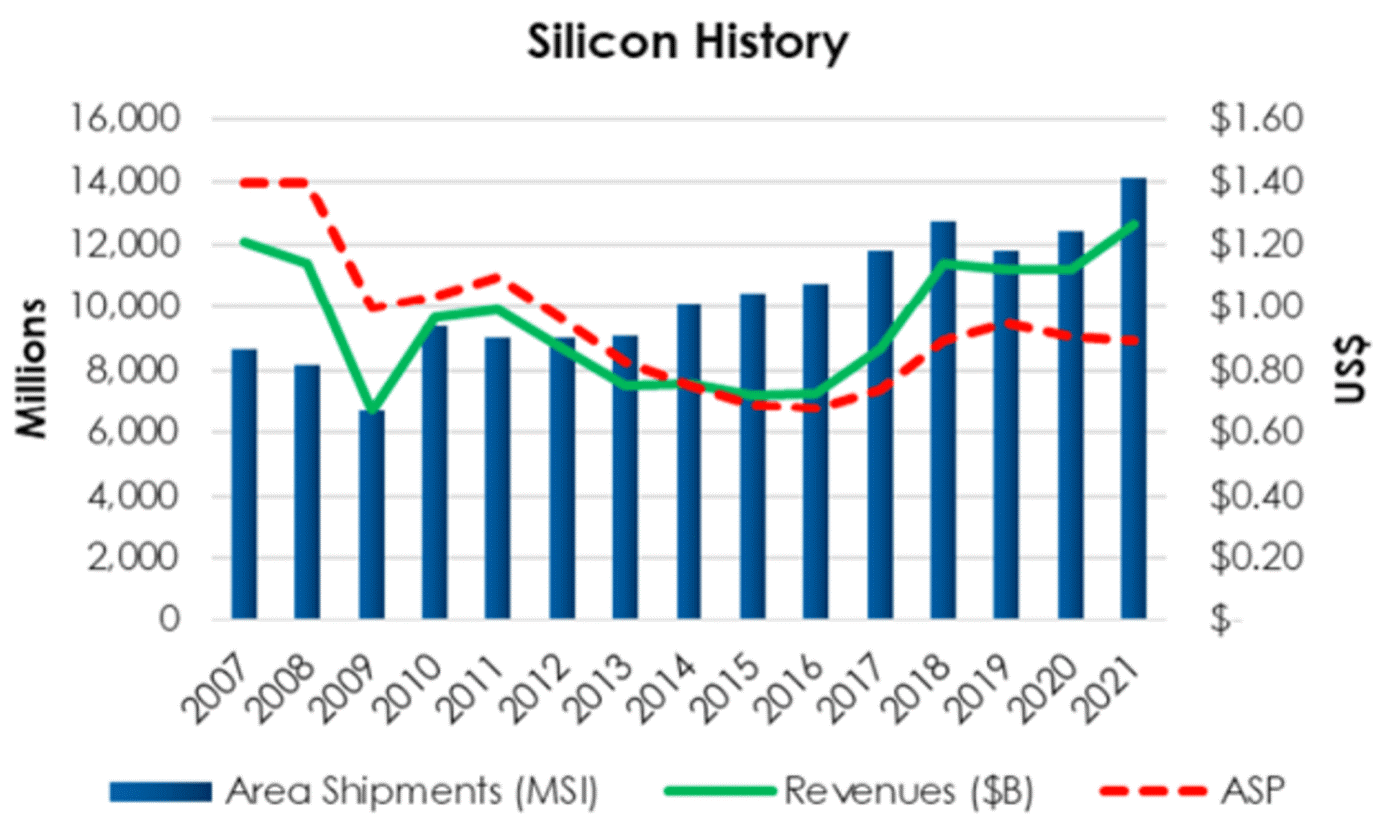

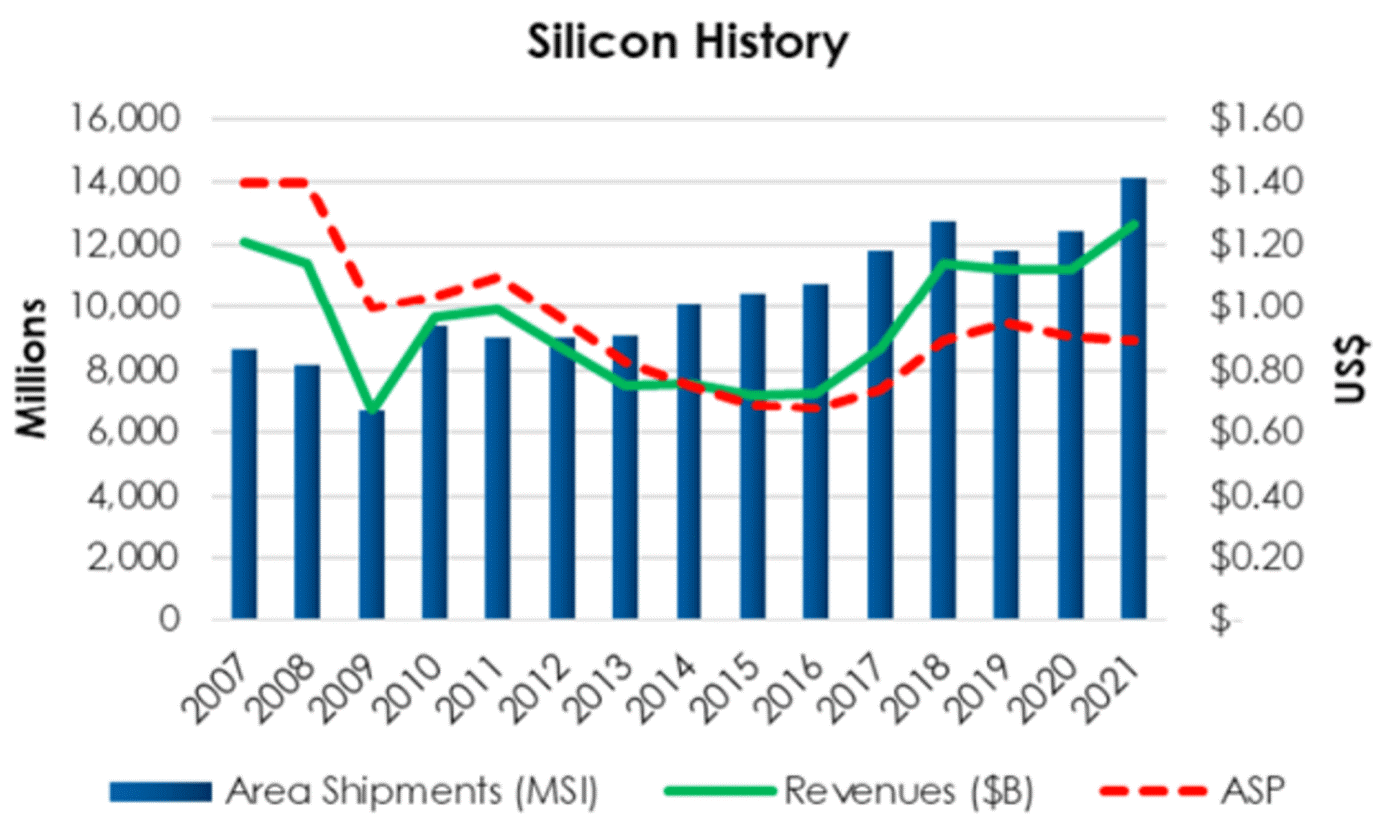

全球前五家公司的月產能都超過了100萬片晶圓,占據了全球產能的53%。

2020-02-14 12:01:01 15619

15619 晶片鍵合是指通過一系列物理過程將兩個或多個基板或晶片相互連接和化學過程。晶片鍵合用于各種技術,如MEMS器件制造,其中傳感器組件封裝在應用程序中。其他應用領域包括三維集成、先進的封裝技術和CI制造業在晶圓鍵合中有兩種主要的鍵合,臨時鍵合和永久鍵合,兩者都是在促進三維集成的技術中發揮著關鍵作用。

2022-07-21 17:27:43 3882

3882 晶圓承載系統是指針對晶圓背面減薄進行進一步加工的系統,該工藝一般在背面研磨前使用。晶圓承載系統工序涉及兩個步驟:首先是載片鍵合,需將被用于硅通孔封裝的晶圓貼附于載片上;其次是載片脫粘,即在如晶圓背面凸點制作等流程完工后,將載片分離。

2023-11-13 14:02:49 6499

6499

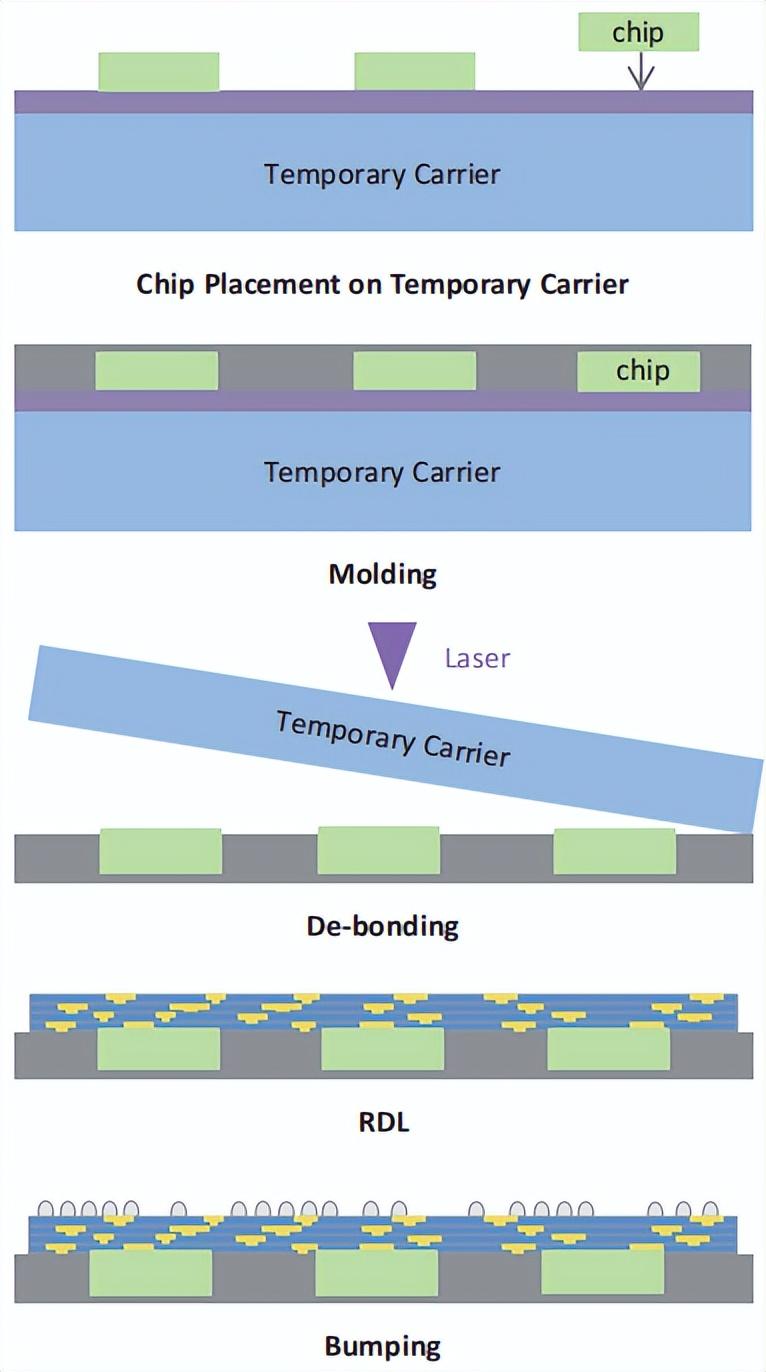

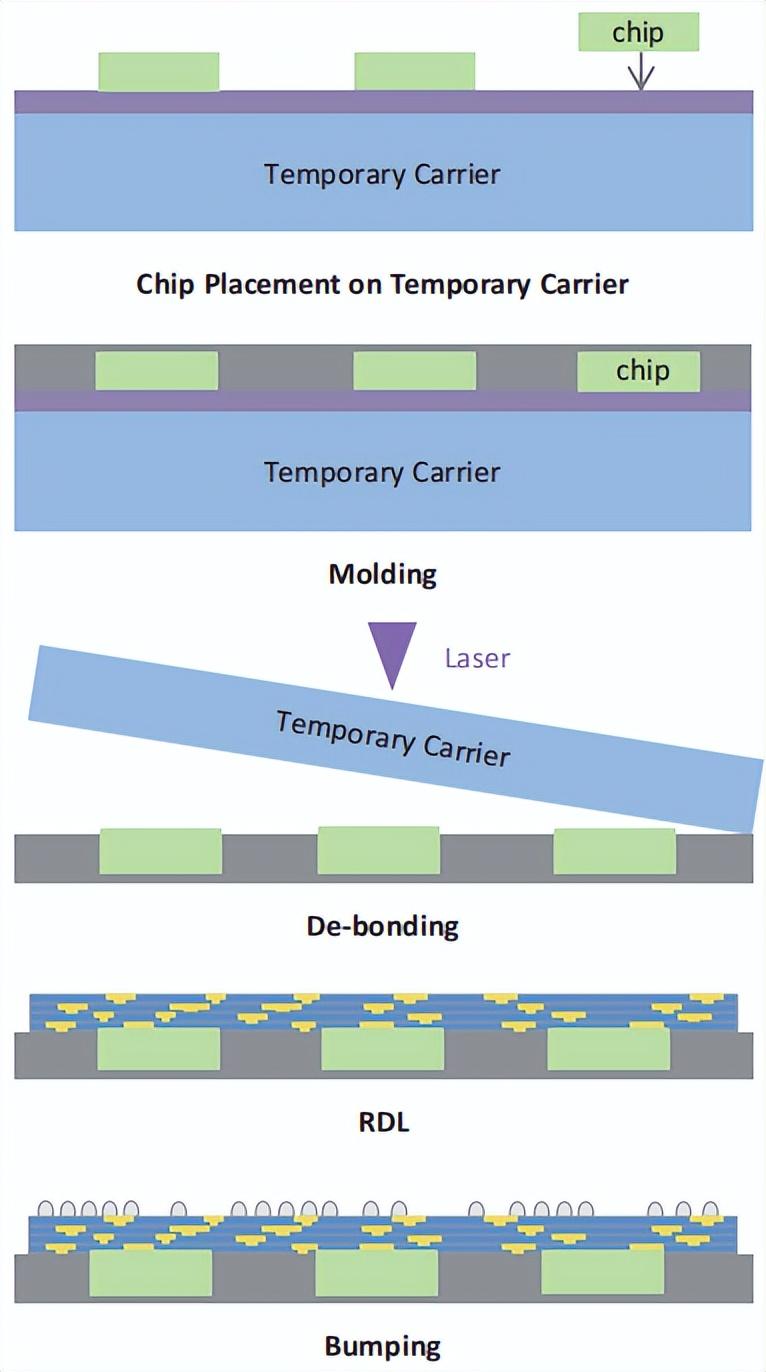

電子發燒友網報道(文/吳子鵬)在芯片制造的過程中,拆鍵合是非常重要的一步。拆鍵合工藝是通過施加熱量或激光照射將重構的晶圓與載板分離。在此過程中,熱敏或紫外線敏感膠帶層會軟化并失去附著力,從而有助于將

2024-03-26 00:23:00 4380

4380

2025年3月11日,香港——中國半導體鍵合集成技術領域的領先企業青禾晶元半導體科技(集團)有限責任公司(簡稱“青禾晶元”)宣布,正式推出全球首臺C2WW2W雙模式混合鍵合設備SAB8210CWW上

2025-03-12 13:43:56 1038

1038

2010年全球前十大晶圓代工排名出爐,臺積電繼續穩居第一,聯電依然排行第二,合并特許半導體后的全球晶圓(Globalfoundries)擠入第三,但營收與聯電才差4億多美元,三星屈居第十。 IC

2011-12-01 13:50:12

大增的刺激下,市場前景的預期下,三星和英特爾同樣瞄準了未來的晶圓代工,并且都積極投入研發費用及資本支出,由此對MAX2321EUP臺積電造成威脅。但據資料顯示,去年全球半導體晶圓代工市場約年成長5.1

2012-08-23 17:35:20

在庫存回補需求帶動下,包括環球晶、臺勝科、合晶、嘉晶等硅晶圓廠第二季下旬出貨續旺,現貨價出現明顯上漲力道,合約價亦確認止跌回升。 新冠肺炎疫情對半導體材料的全球物流體系造成延遲影響,包括晶圓

2020-06-30 09:56:29

,晶圓都是不可缺少的。所以近年來全球晶圓的緊缺不僅僅是只導致了內存條和SSD的漲價,甚至整個電子數碼產品領域都受到了非常嚴重的波及。可見晶圓的重要性。如此緊要的晶圓,我們大多數卻對它必將陌生。我們先來

2019-09-17 09:05:06

有人又將其稱為圓片級-芯片尺寸封裝(WLP-CSP),以晶圓圓片為加工對象,在晶圓上封裝芯片。晶圓封裝中最關鍵的工藝為晶圓鍵合,即是通過化學或物理的方法將兩片晶圓結合在一起,以達到密封效果。如下

2021-02-23 16:35:18

P3503EVG - P-Channel Logic Level Enhancement Mode Field Effect Transistor - List of Unclassifed Manufacturers

2022-11-04 17:22:44

P5504EVG - P-Channel Logic Level Enhancement Mode Field Effect Transistor - List of Unclassifed Manufacturers

2022-11-04 17:22:44

PCM-9361EVG-S6A1E - 3.5" Biscuit with Intel? Atom N270/VGA, LVDS, TTL, LAN, USB, SATA, SSD - Advantech Co., Ltd.

2022-11-04 17:22:44

TQFP128(EVG128) 封裝尺寸圖

2009-07-28 08:03:45

和成本控制的核心參數。通過WD4000晶圓幾何形貌測量系統在線檢測,可減少其對芯片性能的影響。

WD4000晶圓幾何量測系統適用于裸晶圓、圖案晶圓、鍵合晶圓、貼膜晶圓、超薄晶圓等復雜結構晶圓的量

2025-05-28 16:12:46

納米到底有多細微?什么晶圓?如何制造單晶的晶圓?

2021-06-08 07:06:42

` 晶圓是指硅半導體集成電路制作所用的硅晶片,由于其形狀為圓形,故稱為晶圓;在硅晶片上可加工制作成各種電路元件結構,而成為有特定電性功能之IC產品。晶圓的原始材料是硅,而地殼表面有用之不竭的二氧化硅

2011-12-01 11:40:04

的晶粒時,標有記號的不合格晶粒會被洮汰,不再進行下一個制程,以免徒增制造成本。在晶圓制造完成之后,晶圓測試是一步非常重要的測試。這步測試是晶圓生產過程的成績單。在測試過程中,每一個芯片的電性能力和電路

2011-12-01 13:54:00

`晶圓級封裝(WLP)就是在其上已經有某些電路微結構(好比古董)的晶片(好比座墊)與另一塊經腐蝕帶有空腔的晶片(好比玻璃罩)用化學鍵結合在一起。在這些電路微結構體的上面就形成了一個帶有密閉空腔的保護

2011-12-01 13:58:36

翹曲度是實測平面在空間中的彎曲程度,以翹曲量來表示,比如絕對平面的翹曲度為0。計算翹曲平面在高度方向最遠的兩點距離為最大翹曲變形量。翹曲度計算公式:晶圓翹曲度影響著晶圓直接鍵合質量,翹曲度越小,表面

2022-11-18 17:45:23

找了一圈,發現做線鍵合機的比較多,想知道做晶圓鍵合wafer bonding的中國廠家。

2021-04-28 14:34:57

看到了晶圓切割的一個流程,但是用什么工具切割晶圓?求大蝦指教啊 ?

2011-12-01 15:47:14

`什么是硅晶圓呢,硅晶圓就是指硅半導體積體電路制作所用的硅晶片。晶圓是制造IC的基本原料。硅晶圓和晶圓有區別嗎?其實二者是一個概念。集成電路(IC)是指在一半導體基板上,利用氧化、蝕刻、擴散等方法

2011-12-02 14:30:44

硅襯底和砷化鎵襯底金金鍵合后,晶圓粉碎是什么原因,偶發性異常,找不出規律,有大佬清楚嗎,求助!

2023-03-01 14:54:11

` 檢測晶圓表面粗糙度,最常使用的是AFM(原子力顯微鏡)。傳統的AFM樣品規格需小于2cm*2cm,因此在檢測時,都需破壞Wafer才能分析,卻也造成這片晶圓后續無法進行其他實驗分析。宜特引進

2019-08-15 11:43:36

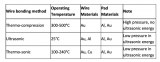

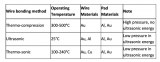

銅線以其良好的電器機械性能和低成本特點已在半導體分立器件的內引線鍵合工藝中得到廣泛應用,但銅線的金屬活性和延展性也在鍵合過程中容易帶來新的失效問題,文中對這種

2009-03-07 10:30:57 16

16 TQFP128 (EVG128) 封裝尺寸圖

2009-07-28 08:01:47 140

140 的工藝參數。【應用范圍】物理氣相沉積 (PVD)、原子層沉積 (ALD)、化學氣相沉積 (CVD)、退火爐、去膠設備、晶圓臨時鍵合、涂膠

2025-06-27 10:16:41

全球晶圓資本支出緊追臺積

全球第三大晶圓代工廠商全球晶圓(Globalfoundires)昨(15)日宣布,為擴充12寸廠產能,今年資本支出將達

2010-03-17 09:46:47 1208

1208 據EVG公司ThomasUhrmann和ThorstenMatthias了解,LED設備需求逐漸從價格驅動轉向技術驅動,LED設備呈現更復雜更高效率的趨勢

2012-02-09 08:51:02 1050

1050 微機電系統(MEMS)、納米技術以及半導體市場晶圓鍵合和光刻設備領先供應商EV集團(EVG)今日宣布推出IQ Aligner NT,旨針對大容量先進封裝應用推出的全新自動掩模對準系統。IQ

2017-03-11 01:04:32 1367

1367 將二氧化矽經過純化,融解,蒸餾之后,制成矽晶棒,晶圓廠再拿這些矽晶棒研磨,拋光和切片成為晶圓母片.目前晶圓片越來越多的受到了應用,本文詳細介紹了全球十大晶圓片的供應商。

2018-03-16 15:05:08 75274

75274 WaveOptics宣布,與EVG合作,并且表示,與 EVG 的伙伴關系將使 WaveOptics 提高生產能力, 降低波導組件的總成本, 使制造商能夠在2019年底之前提供600美元以下的 AR 設備。

2018-05-03 10:49:13 4591

4591 GEMINI FB XT在晶圓鍵合領域突破國際半導體技術藍圖標準,晶圓對晶圓排列效果提升可達三倍;同時強化生產能量,使產能增加50% EVG集團今日公布了新一代融化晶圓鍵合平臺GEMINI FB XT,該平臺匯集多項技術突破,令半導體行業向實現3D-IC硅片通道高容量生產的目標又邁進了一步。

2018-05-25 00:55:00 4599

4599 新型鍵合材料對于在高級半導體制造工藝中保持超薄晶圓的完整性至關重要。有了新型材料的配合,臨時鍵合在晶圓減薄工藝中愈發成為可能。

2018-06-25 16:48:00 10819

10819

全球最大的晶圓代工企業。臺積電成立于1987年,總部位于中國臺灣新竹,是全球第一家專注于代工的集成電路制造企業。公司經過30余年的發展,目前也已經發展為全球最大的晶圓代工企業,市場份額超過50

2018-06-26 11:14:50 9207

9207

據悉,英國光電子技術解決方案的領先開發商Plessey Semiconductor日前表示,已從晶圓鍵合和光刻設備生產商EVG購買了GEMINI晶圓鍵合系統。

2018-11-16 15:10:08 2158

2158 倍的晶圓鍵合對準和套刻性能 奧地利,圣弗洛里安,2019 年 3 月 5 日面向MEMS、納米技術和半導體市場的晶圓鍵合與光刻設備的領先供應商EV集團 (EVG) 今日宣布將在SEMICON

2019-03-05 14:21:36 2554

2554 鍵合與光刻設備的領先供應商EV集團(EVG) 今日推出了全新的BONDSCALE自動化生產熔融系統。BONDSCALE旨在滿足各種熔融/分子晶圓鍵合應用,包括工程基板制造和使用材料層轉移進行3D集成

2019-03-12 14:24:45 2693

2693 SEMICON CHINA,2019 年 3 月 20 日晶圓鍵合和光刻設備的領先供應商EV集團(EVG)今日宣布,與總部位于中國寧波的特種工藝半導體制造公司中芯集成電路(寧波)有限公司(以下簡稱中芯寧波)合作,開發業界首個砷化鎵射頻前端模組晶圓級微系統異質集成工藝技術平臺。

2019-03-20 14:00:41 2493

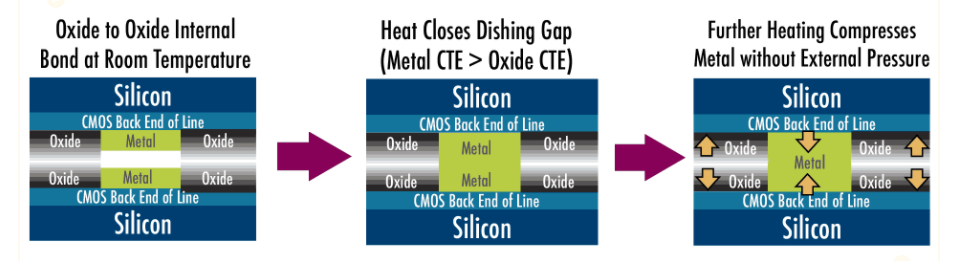

2493 根據臺積電在第二十四屆年度技術研討會中的說明,SoIC是一種創新的多芯片堆疊技術,是一種晶圓對晶圓(Wafer-on-wafer)的鍵合(Bonding)技術,這是一種3D IC制程技術,可以讓臺積電具備直接為客戶生產3D IC的能力。

2019-08-14 11:21:06 4993

4993

,圣弗洛里安微機電系統(MEMS)、納米技術和半導體市場晶圓鍵合與光刻設備領先供應商EV集團(EVG)今日宣布,與特種玻璃和微晶玻璃領域的世界領先技術集團肖特攜手合作,證明300-mm(12英寸)光刻/納米壓印(NIL)技術在下一代增強現實/混合現實(AR/MR)頭戴顯示設備的波導/光

2019-08-29 22:48:03 2854

2854 ),2019年11月27日 EV 集團 (EVG) 這一全球領先的為微機電系統、納米技術與半導體市場提供晶圓鍵合與光刻設備的供應商,今天宣布與高科技工業粘合劑制造商 DELO 在晶圓級光學元件

2019-11-27 22:35:56 2070

2070 市場提供晶圓鍵合與光刻設備的領先供應商EV Group(EVG)今天推出LITHOSCALE無掩模曝光系統,該系統也是首個采用EV集團(EVG)革命性技術MLE(無掩膜曝光)的產品平臺。EV Group

2020-09-23 10:26:05 3693

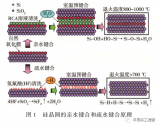

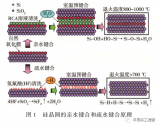

3693 目前晶圓鍵合工藝技術可分為兩大類:一類是鍵合雙方不需要介質層,直接鍵合,例如陽極鍵合;另一類需要介質層,例如金屬鍵合。如下圖2的鍵合工藝分類

2021-03-01 11:57:09 18161

18161 12月31日消息,據英文媒體報道,芯片代工市場需求強勁,也拉升了對硅晶圓的需求,硅晶圓制造商環球晶圓,已在計劃提高現貨市場的硅晶圓價格。

2020-12-31 13:42:56 2810

2810 環球晶圓是全球重要的晶圓供應商,他們擁有完整的晶圓生產線,生產高附加值的晶圓產品,除了用于制造芯片的半導體晶圓,他們也生產太陽能晶圓及晶棒。

2021-01-06 15:34:50 2652

2652 芯片是晶圓切割完成的半成品,晶圓是芯片的載體,將晶圓充分利用刻出一定數量的芯片后,進行切割就就成了一塊塊的芯片了。

2022-01-29 16:16:00 62389

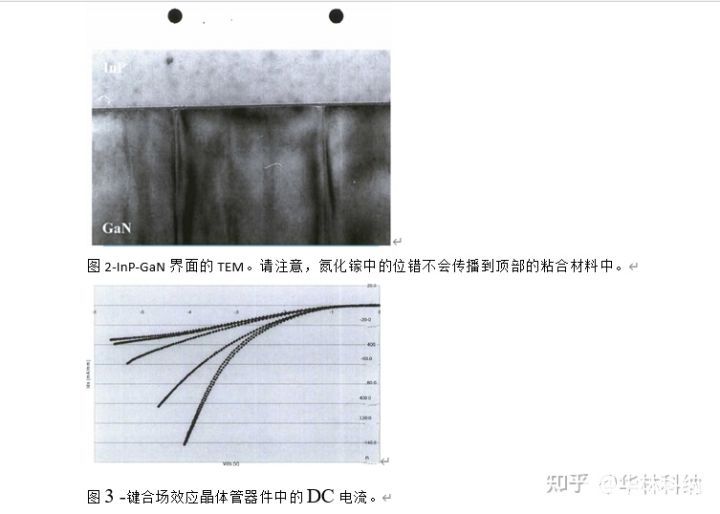

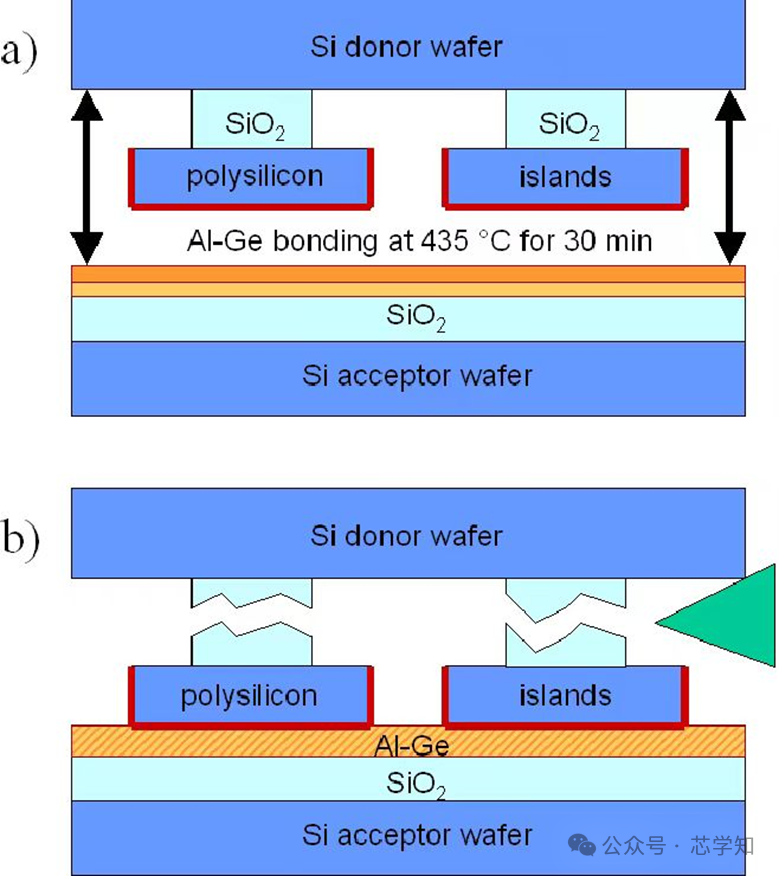

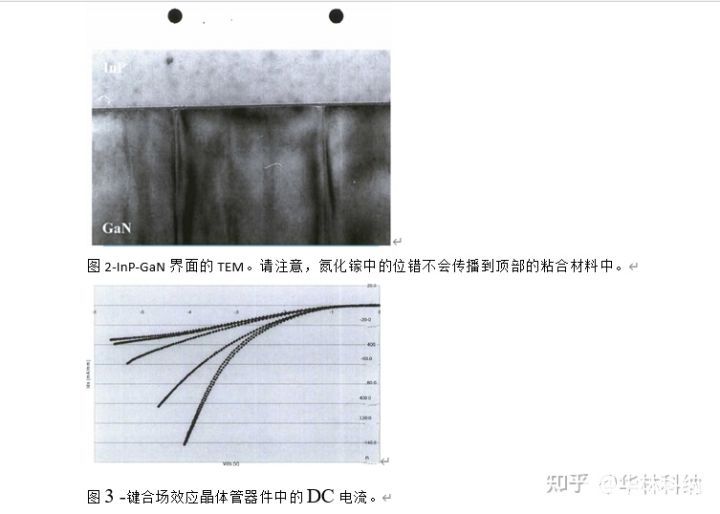

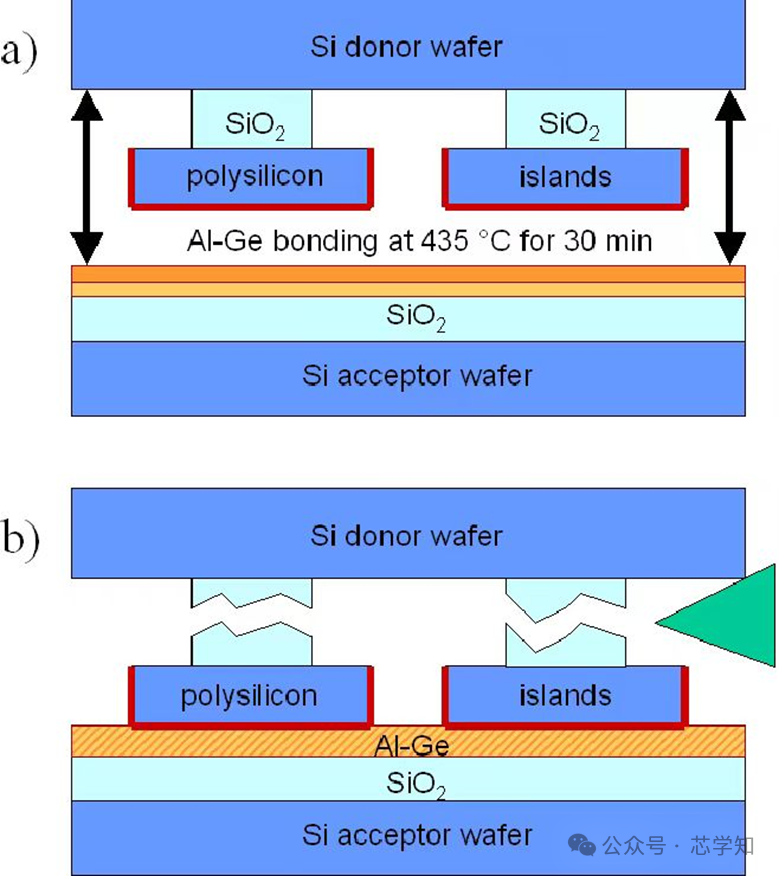

62389 到350°C,并允許硅與氮化鎵結合。 背景 許多半導體材料系統是彼此不相容的。由于晶格錯配,一些不能通過異質外延一起生長,而對于另一些,在一個上產生器件所需的過程條件會破壞另一個。半導體晶片鍵合是這兩個問題的解決方案之一。粘結允許這兩種材料系統分別

2022-01-24 16:57:47 1419

1419

來源:半導體芯科技 Simon編譯 近幾年,全球晶圓供求失衡,200mm晶圓短缺會持續數年。晶圓生產的全球五大廠商——日本SEH、Sumco、德國Siltronic、臺灣GlobalWafter

2022-06-17 16:24:08 1836

1836

通過控制單一變量的試驗方法,研究了金絲變形度、超聲功率、超聲時間和鍵合壓力等參數對自動鍵合一致性和可靠性的影響,分析了每個參數對自動鍵合的影響規律,給出了自動鍵合參數的參考范圍。

2023-02-01 17:37:31 2972

2972 結束前工序的每一個晶圓上,都連接著500~1200個芯片(也可稱作Die)。 為了將這些芯片用于所需之處,需要將晶圓切割(Dicing)成單獨的芯片后,再與外部進行連接、通電。 此時,連接

2023-03-13 15:49:58 7088

7088

這是一種晶圓鍵合方法,其中兩個表面之間的粘附是由于兩個表面的分子之間建立的化學鍵而發生的。

2023-04-20 09:43:57 5918

5918 當的方式為激光解鍵合。鴻浩半導體設備所生產的UV激光解鍵合設備具備低溫、不傷晶圓等技術特點,并且提供合理的制程成本,十分適合應用于扇出晶圓級封裝。 01 扇出晶圓級封裝簡介 扇出晶圓級封裝(Fan Out Wafer Level Packaging, FOWLP,簡稱扇出

2023-04-28 17:44:43 2743

2743

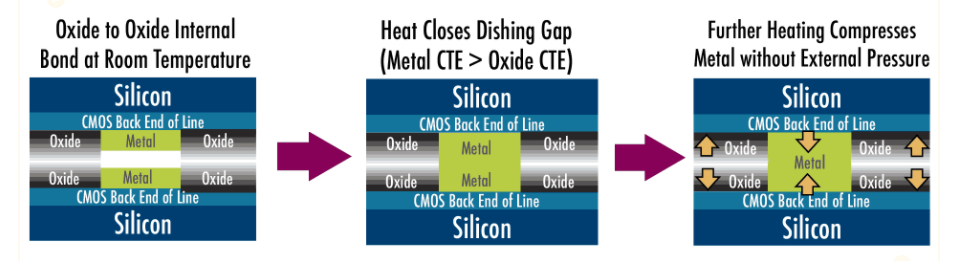

兩片晶圓面對面鍵合時是銅金屬對銅金屬、介電值對介電質,兩邊鍵合介面的形狀、位置完全相同,晶粒大小形狀也必須一樣。所以使用混合鍵合先進封裝技術的次系統產品各成分元件必須從產品設計、線路設計時就開始共同協作。

2023-05-08 09:50:30 2600

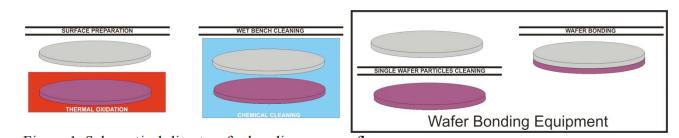

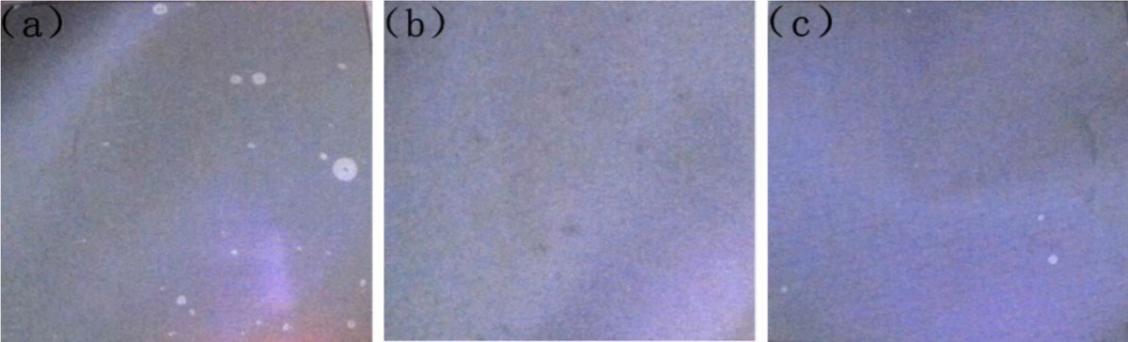

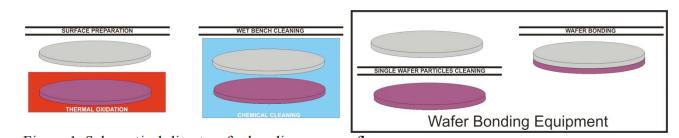

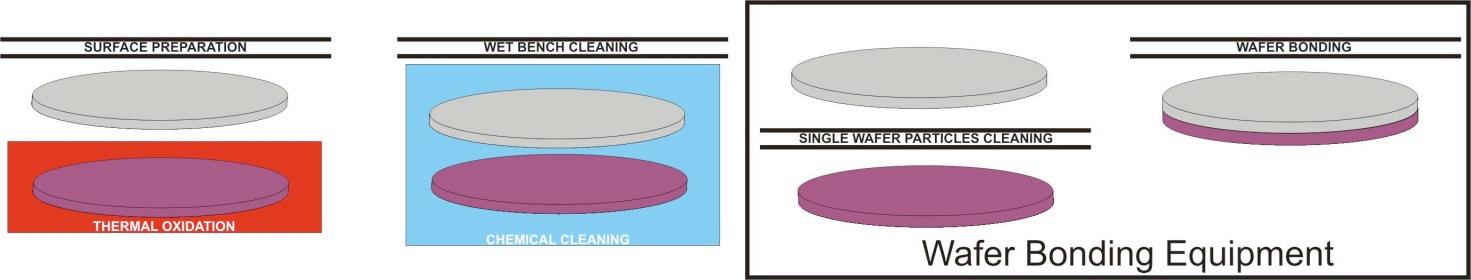

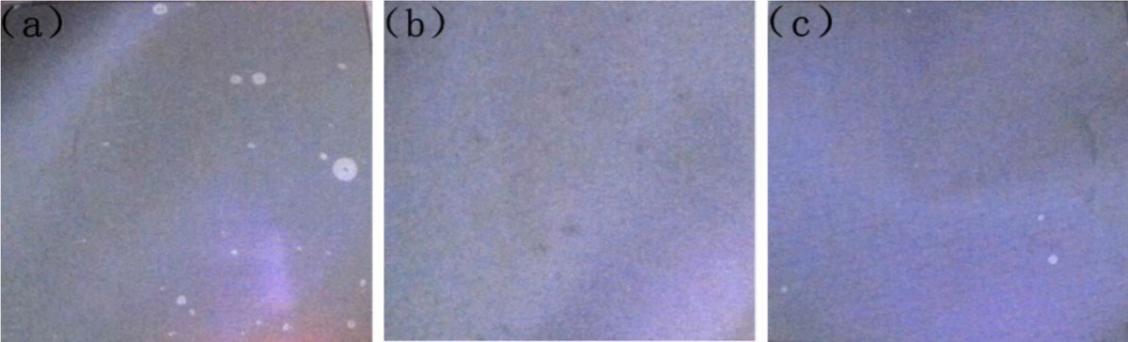

2600 就微粒污染而言,不同的微電子工藝需要非常干凈的表面。其中,直接晶片粘接在顆粒清潔度方面有非常積極的要求。直接晶圓鍵合是將兩種材料結合在一起,只需將它們光滑干凈的表面接觸即可(圖1)。在常溫常壓下,兩種材料表面的分子/原子之間形成的范德華力會產生附著力

2023-05-09 14:52:19 1767

1767

晶圓鍵合是半導體行業的“嫁接”技術,通過化學和物理作用將兩塊已鏡面拋光的晶片緊密地結合起來,進而提升器件性能和功能,降低系統功耗、尺寸與制造成本。

2023-06-02 16:45:04 960

960

晶圓直接鍵合技術可以使經過拋光的半導體晶圓,在不使用粘結劑的情況下結合在一起,該技術在微電子制造、微機電系統封裝、多功能芯片集成以及其他新興領域具有廣泛的應用。對于一些溫度敏感器件或者熱膨脹系數差異

2023-06-14 09:46:27 3533

3533

晶圓鍵合機主要用于將晶圓通過真空環境, 加熱, 加壓等指定的工藝過程鍵合在一起, 滿足微電子材料, 光電材料及其納米等級微機電元件的制作和封裝需求. 晶圓鍵合機需要清潔干燥的高真空工藝環境, 真空度

2023-05-25 15:58:06 1696

1696

InP 材料在力學方面具有軟脆的特性,導致100 mm(4 英寸)InP 晶圓在化合物半導體工藝中有顯著的形變和碎裂的風險;同時,InP 基化合物半導體光電子器件芯片大部分采用雙面工藝,在晶圓的雙面進行半導體工藝。

2023-06-27 11:29:32 18334

18334

結束前工序的每一個晶圓上,都連接著500~1200個芯片(也可稱作Die)。為了將這些芯片用于所需之處,需要將晶圓切割(Dicing)成單獨的芯片后,再與外部進行連接、通電。此時,連接電線(電信號

2023-08-09 09:49:47 6419

6419

不同的微電子工藝需要非常干凈的表面以防止顆粒污染。其中,晶圓直接鍵合對顆粒清潔度的要求非常嚴格。直接晶圓鍵合包括通過簡單地將兩種材料的光滑且干凈的表面接觸來將兩種材料連接在一起(圖1)。在室溫和壓力下,兩種材料表面的分子/原子之間形成的范德華力會產生粘附力。

2023-09-08 10:30:18 840

840

隨著產業和消費升級,電子設備不斷向小型化、智能化方向發展,對電子設備提出了更高的要求。可靠的封裝技術可以有效提高器件的使用壽命。陽極鍵合技術是晶圓封裝的有效手段,已廣泛應用于電子器件行業。其優點是鍵合時間短、鍵合成本低。溫度更高,鍵合效率更高,鍵合連接更可靠。

2023-09-13 10:37:36 1239

1239

引線鍵合是在硅芯片上的 IC 與其封裝之間創建互連的常用方法,其中將細線從器件上的鍵合焊盤連接到封裝上的相應焊盤(即引線)。此連接建立了從芯片內部電路到連接到印刷電路板 (PCB) 的外部引腳的電氣路徑。

2023-10-24 11:32:13 3691

3691

晶圓鍵合技術是將兩片不同結構/不同材質的晶圓,通過一定的物理方式結合的技術。晶圓鍵合技術已經大量應用于半導體器件封裝、材料及器件堆疊等多種半導體應用領域。

2023-10-24 12:43:24 2895

2895

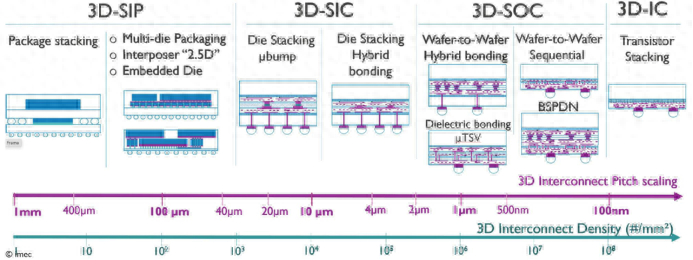

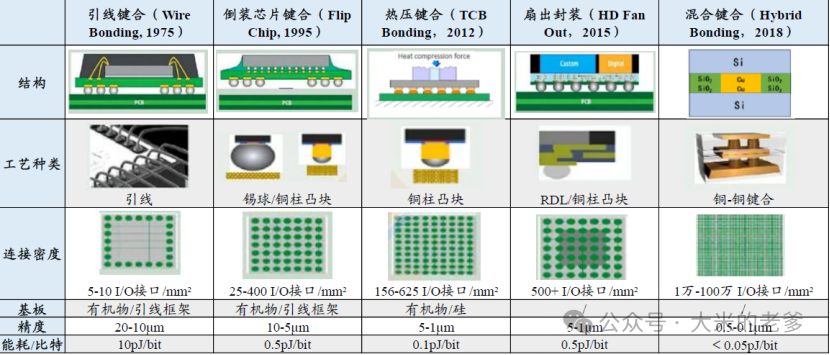

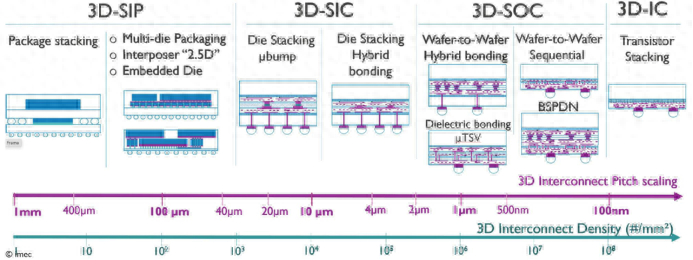

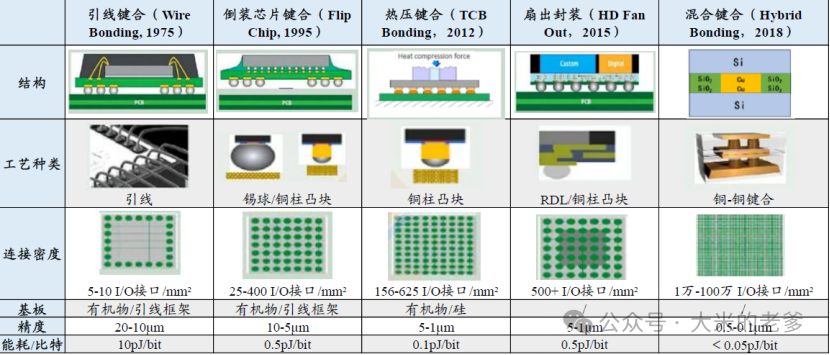

要了解混合鍵合,需要了解先進封裝行業的簡要歷史。當電子封裝行業發展到三維封裝時,微凸塊通過使用芯片上的小銅凸塊作為晶圓級封裝的一種形式,在芯片之間提供垂直互連。凸塊的尺寸范圍很廣,從 40 μm 間距到最終縮小到 20 μm 或 10 μm 間距。

2023-11-22 16:57:42 6765

6765

的無機脫模材料,能夠以納米級精度從硅載體襯底上脫模鍵合、沉積或生長的層。因此,EVG850 NanoCleave 消除了對玻璃載體的需求,從而實

2023-12-13 17:26:46 1405

1405

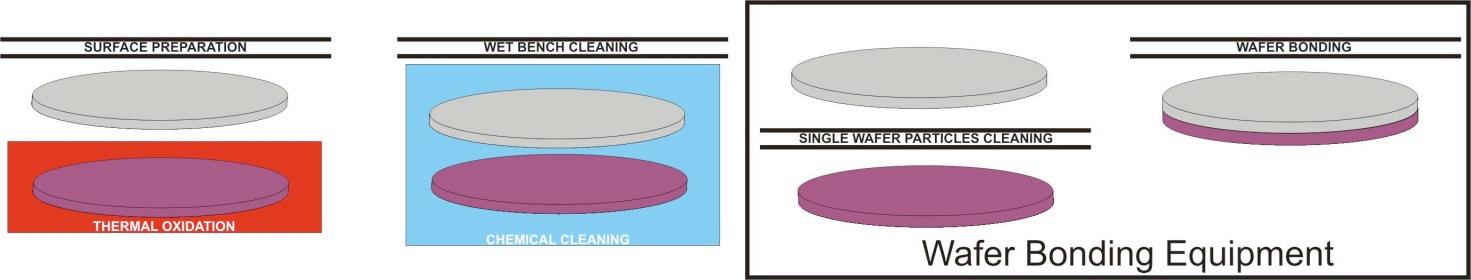

隨著半導體產業的飛速發展,晶圓鍵合設備及工藝在微電子制造領域扮演著越來越重要的角色。晶圓鍵合技術是一種將兩個或多個晶圓通過特定的工藝方法緊密地結合在一起的技術,以實現更高性能、更小型化的電子元器件。本文將詳細介紹晶圓鍵合設備的結構、工作原理以及晶圓鍵合工藝的流程、特點和應用。

2023-12-27 10:56:38 3181

3181

晶圓鍵合是一種將兩片或多片半導體晶片通過特定的工藝條件,使其緊密結合并形成一個整體的技術。這種技術在微電子、光電子以及MEMS(微機電系統)等領域有著廣泛的應用。晶圓鍵合工藝能夠實現不同材料、不同功能層之間的集成,從而提高器件的性能和可靠性。

2024-02-21 09:48:44 3232

3232

來源:IMEC Cu/SiCN鍵合技術的創新是由邏輯存儲器堆疊需求驅動的 晶圓到晶圓混合鍵合的前景 3D集成是實現多芯片異構集成解決方案的關鍵技術,是業界對系統級更高功耗、性能、面積和成本收益需求

2024-02-21 11:35:29 1454

1454

芯片堆疊封裝存在著4項挑戰,分別為晶圓級對準精度、鍵合完整性、晶圓減薄與均勻性控制以及層內(層間)互聯。

2024-02-21 13:58:34 9340

9340

近日,芯碁微裝又推出WA 8晶圓對準機與WB 8晶圓鍵合機,此兩款設備均為半導體加工過程中的關鍵設備。

2024-03-21 13:58:20 2165

2165 的容量和功能。在過去的幾十年中,基于薄晶圓 ( 通常厚度小于 100 μm) 的硅穿孔(Through-Silicon Via,TSV) 技術已經實現了 3D-IC 封裝。但是由于薄晶圓的易碎性和易翹曲的傾向,在對器件晶圓進行背部加工過程中,需要利用膠粘劑將其固定在載體上,并使薄晶圓在背部

2024-03-29 08:37:59 2196

2196 FRAM SF25C20晶圓合封MCU,滿足小尺寸和高性能需求

2024-04-22 09:49:21 1574

1574

5 月 10 日報道,據全球半導體產業協會 SEMI 的統計,今年首季全球半導體硅晶圓出貨量為 28.34 億平方英寸(約合 2500 萬片 12 英寸晶圓),比去年四季度下滑 5.4%,比去年同期更是大減 12.2%。

2024-05-10 10:27:48 1026

1026 Luminex machines set a new standard when it comes to flexibility, cost-effectiveness, and throughput "臨時鍵合和解鍵合是基板(晶圓或面板)減薄和封裝工藝不

2024-05-29 17:39:58 1072

1072

發展空間較大。對半導體芯片鍵合裝備進行了綜述,具體包括主要組成機構和工作原理、關鍵技術、發展現狀。半導體芯片鍵合裝備的主要組成機構包括晶圓工作臺、芯片鍵合頭、框架輸送系統、機器視覺系統、點膠系統。半導體芯片鍵合裝備的關鍵技

2024-06-27 18:31:14 3142

3142

共讀好書歡迎掃碼添加小編微信掃碼加入知識星球,領取公眾號資料

原文標題:晶圓鍵合工藝技術詳解(69頁

2024-11-01 11:08:07 1096

1096 定位技術專家 TomTom和 East View Geospatial (EVG) 宣布合作,向澳大利亞政府國防部提供全球地圖數據。

2024-09-02 14:01:50 1084

1084 DieBound芯片鍵合,是在封裝基板上安裝芯片的工藝方法。本文詳細介紹一下幾種主要的芯片鍵合的方法和工藝。什么是芯片鍵合在半導體工藝中,“鍵合”是指將晶圓芯片連接到基板上。連接可分為兩種類型,即

2024-09-20 08:04:29 2714

2714

晶圓鍵合技術是一種先進的半導體制造工藝,它通過將兩塊或多塊晶圓在一定的工藝條件下緊密結合,形成一個整體結構。這種技術廣泛應用于微電子、光電子、MEMS(微機電系統)等領域,是實現高效封裝和集成的重要步驟。晶圓鍵合技術不僅能夠提高器件的性能和可靠性,還能滿足市場對半導體器件集成度日益提高的需求。

2024-10-21 16:51:40 2444

2444 隨著半導體產業的快速發展,集成電路(IC)的小型化、高密度集成、多功能高性能集成以及低成本集成成為行業發展的必然趨勢。在這一背景下,3D集成晶圓鍵合技術應運而生,成為實現這些目標的關鍵技術之一。本文

2024-11-12 17:36:13 2457

2457

將兩個晶圓永久性或臨時地粘接在一起的膠黏材料。 怎么鍵合與解鍵合? 如上圖,鍵合過程: 1.清潔和處理待鍵合晶圓表面。 2.將兩個待鍵合的晶圓對準并貼合在一起。 3.施加壓力和溫度,促進鍵合膠之間的粘接。 4.繼續保溫,使鍵合材料達到最佳粘接強度。 ? 解鍵合

2024-11-14 17:04:44 3586

3586

去除晶圓鍵合邊緣缺陷的方法主要包括以下幾種:

一、化學氣相淀積與平坦化工藝

方法概述:

提供待鍵合的晶圓。

利用化學氣相淀積的方法,在晶圓的鍵合面淀積一層沉積量大于一定閾值(如1.6TTV

2024-12-04 11:30:18 584

584

工藝中常用的材料包括:

芯片粘結劑:作為漿料涂覆到晶圓背面,之后再烘干。采用這種方法,成本較低,同時可以控制鍵合層厚度并且提高單位時間產量。

WBC膠水:其成分

2024-12-19 09:54:10 620

620

金屬共晶鍵合是利用金屬間的化學反應,在較低溫度下通過低溫相變而實現的鍵合,鍵合后的金屬化合物熔點高于鍵合溫度。該定義更側重于從材料科學的角度定義。

2025-03-04 14:14:41 1922

1922

鍵合技術主要分為直接鍵合和帶有中間層的鍵合。直接鍵合如硅硅鍵合,陽極鍵合等鍵合條件高,如高溫、高壓等。而帶有中間層的鍵合,所需的溫度更低,壓力也更小。帶金屬的中間層鍵合技術主要包括共晶鍵合、焊料鍵合、熱壓鍵合和反應鍵合等。本文主要對共晶鍵合進行介紹。

2025-03-04 17:10:52 2636

2636

全新強力鍵合腔室設計,賦能更大尺寸晶圓高均勻性鍵合與量產良率提升 2025年3月18日,奧地利圣弗洛里安 —全球領先的半導體創新工藝解決方案和專業知識提供商,為前沿和未來的半導體設計和芯片集成

2025-03-20 09:07:58 889

889

,半導體制造商傾向于采用厚度小于 100 μm的薄晶圓。然而,晶圓越薄就越容易破損,為此,行業開發了各種臨時鍵合和解鍵 (TBDB) 技術,利用專用鍵合膠將器件晶圓臨時固定在剛性載板上,以提升制造過程的穩定性和良率。 現有解鍵方法的局限

2025-03-28 20:13:59 790

790 芯片封裝是半導體制造的關鍵環節,承擔著為芯片提供物理保護、電氣互連和散熱的功能,這其中的鍵合技術(Bonding)就是將晶圓芯片固定于基板上。

2025-04-10 10:15:38 2844

2844

關鍵詞:鍵合晶圓;TTV 質量;晶圓預處理;鍵合工藝;檢測機制 一、引言 在半導體制造領域,鍵合晶圓技術廣泛應用于三維集成、傳感器制造等領域。然而,鍵合過程中諸多因素會導致晶圓總厚度偏差(TTV

2025-05-26 09:24:36 854

854

方式可分為: 機械夾持:通過物理接觸固定晶圓邊緣。 真空吸附:利用真空力吸附晶圓背面。 靜電吸附:通過靜電力固定晶圓(較少使用,因可能引入電荷損傷)。 2. 機械夾持設計 (1)邊緣夾持 原理: 使用可開合的機械臂(如爪狀結構)夾

2025-07-23 14:25:43 931

931 )今日發布EVG?40 D2W——業界首款專用于晶粒對晶圓(Die-to-Wafer, D2W)套刻精度計量的測量平臺。該系統可在300毫米晶圓上實現每顆芯片的100%套刻精度測量,同時具備量產所需

2025-09-11 15:22:57 713

713 在半導體封裝工藝中,芯片鍵合(Die Bonding)是指將晶圓芯片固定到封裝基板上的關鍵步驟。鍵合工藝可分為傳統方法和先進方法:傳統方法包括芯片鍵合(Die Bonding)和引線鍵合(Wire

2025-10-21 17:36:16 2062

2062

電子發燒友App

電子發燒友App

評論