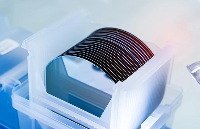

在 EVG 的 NILPhotonics? 解決方案支援中心,雙方合作研發用于制造光學傳感器的新材料,以及適用于大眾化市場的晶圓級光學元件。

ST. FLORIAN(奧地利)與 WINDACH (德國),2019年11月27日 —— EV 集團 (EVG) 這一全球領先的為微機電系統、納米技術與半導體市場提供晶圓鍵合與光刻設備的供應商,今天宣布與高科技工業粘合劑制造商 DELO 在晶圓級光學元件 (WLO) 領域開展合作。這兩家公司均在光學傳感器制造領域處于領先地位。它們的合作將充分利用 EVG 的透鏡注塑成型與納米壓印光刻 (NIL) 加工設備與 DELO 先進的粘合劑與抗蝕材料,在工業,汽車,消費類電子產品市場開發與應用新型光學設備,例如生物特征身份認證,面部識別。

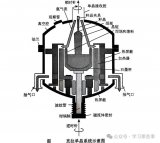

目前雙方正在 EVG 的 NILPhotonics? 解決方案支援中心 (位于 EVG 總部,奧地利 Florian)以及 DELO 在德國 Windach 的總部展開合作。雙方致力于改善與加快材料研發周期。EVG 的 NILPhotonics 解決方案支援中心為 NIL 供應鏈的客戶與合作伙伴提供了開放的創新孵化器,旨在通過合作來縮短創新設備與應用的研發與推廣周期。該中心的基礎設施包括最先進的潔凈室與支持 NIL 制造的主要步驟的設備,例如分步重復母版,透鏡模制,以及 EVG 的 SmartNIL? 技術,晶圓鍵合與必要的測量設備。它為晶圓級光學元件開發、原型設計和制造提供了一種獨特的方法,可以方便地接觸最新研發技術與材料。

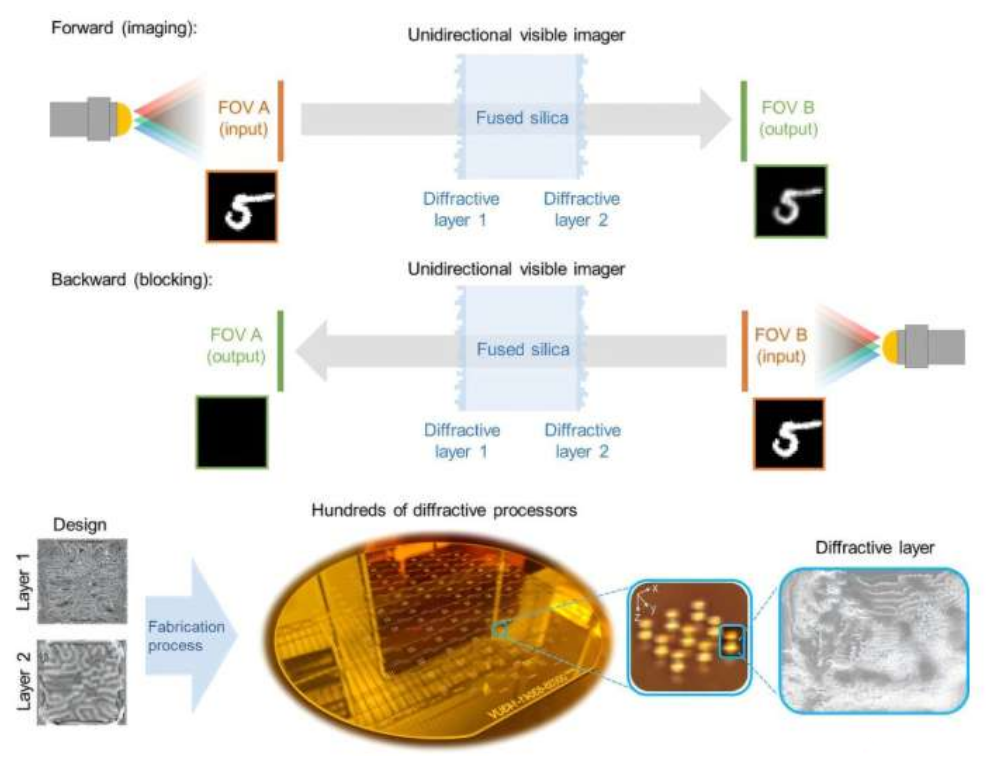

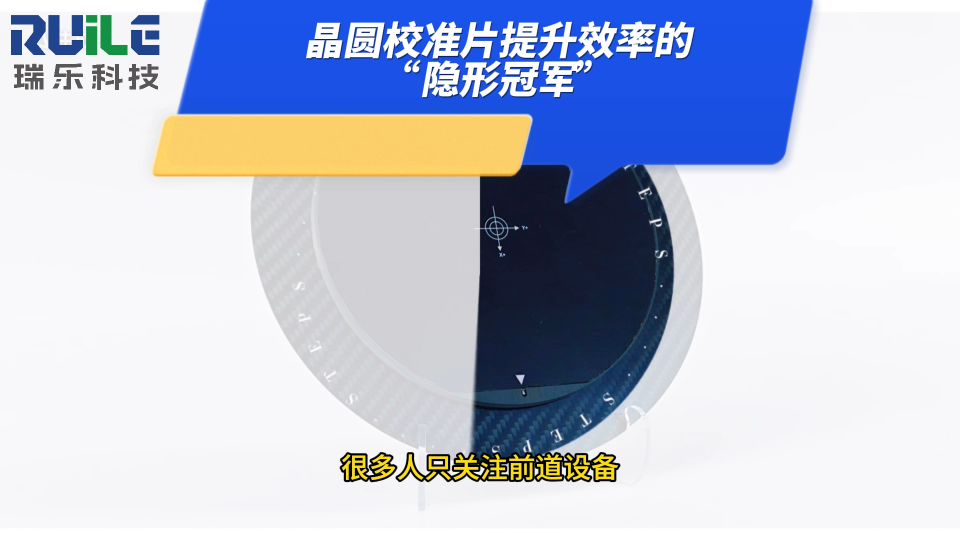

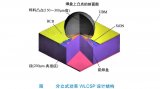

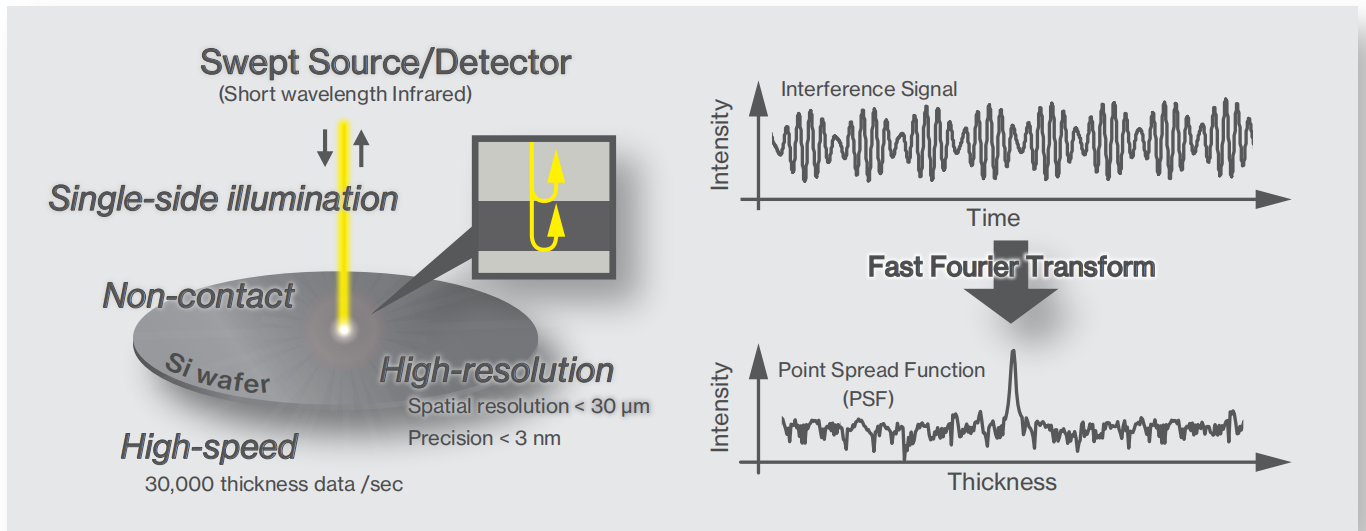

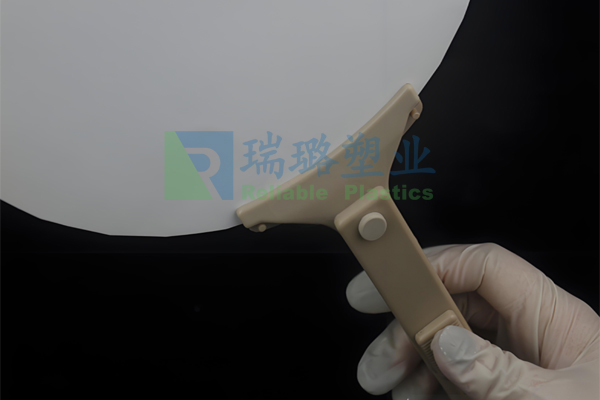

晶圓級納米壓印光刻和透鏡注塑成型技術確保在如3D感應的應用中使用小尺寸的高分辨率光學傳感器

供應鏈合作推動晶圓級光學元件應用

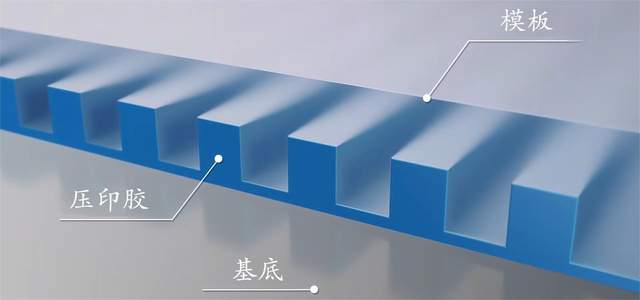

要在下一代光學傳感器的大眾化市場中推廣晶圓級生產,先進的粘合劑與抗蝕材料發揮著不可取代的作用。開發先進的光學材料,需要充分地研究化學、機械與光學特性,以及已被證實的大規模生產(HVM)的可擴展性。擁有在NIL 圖形壓印和抗蝕工藝方面的材料兼容性,以及自動化模制和脫模的專業知識,才能在已驗證的大規模生產中,以最小的形狀因子達到晶圓級光學元件的最佳性能。

材料供應商與加工設備制造商之間的密切合作,促成了工藝流程的研發與改善,確保晶圓級光學元件的高質量和制造的可靠性。EVG 和 DELO 的合作將支持雙方改善工藝流程與產品,并增強雙方的專業技能,從而適應當前與未來市場的要求。雙方的合作提供了成熟的材料與專業的工藝技術,并將加快新產品設計與原型制造的速度,為雙方的客戶保駕護航。

“NILPhotonics 解決方案支援中心的獨特之處是:它解決了行業內部需要用更短時間研發產品的需求,同時保障最高的保密性,” EV集團的技術研發與 IP 主管Markus Wimplinger說, “通過與供應鏈的關鍵企業的合作,例如 DELO,我們能夠進一步提高效率,作為與工藝和設備專家們一同研究并建立關鍵的新生產線制造步驟的中心。”

“EVG 和 DELO 分別是晶圓級光學儀器與 NIL 設備與光學材料的技術與市場領先企業。雙方在將技術與工藝流程應用于大規模生產方面有可靠的經驗,” ?DELO 的董事總經理 Robert Saller 說道。“通過合作,我們將提供自己獨特的技術,將晶圓級工藝技術應用于光學器件和光電器件制造中,EVG也成為我們最新產品開發的理想合作伙伴。這種合作還將使我們以應用專家和頂級合作伙伴的身份為客戶服務。"

晶圓級光學元件的應用解決方案

EVG 的晶圓級光學器件解決方案為移動式消費電子產品提供多種新型的光學傳感設備。主要的例子是: 3D 感應,飛行時間,結構光,生物特征身份認證,面部識別, 虹膜掃描,光學指紋,頻譜檢測,環境感應與紅外線成像。其它應用領域包括汽車照明,光地毯,平視顯示器,車內感應,激光雷達,內窺鏡照相機醫學成像,眼科設備與手術機器人。EVG 的晶圓級光學儀器解決方案得到公司的 NILPhotonics 解決方案支援中心的支持。

DELO 創新的多功能材料幾乎可以在世界上每部手機上找到。該公司的高科技粘合劑以功能與可靠性聞名于世。根據客戶的專門需求,公司對這些聚合物作出調整,使其具備其它特征。它們極其適合工業環境,在較短的生產周期時間內粘合各種微小的元件。此外, DELO 紫外線 LED 固化設備與點膠閥的可靠度十分杰出。

關于德路

德路 (DELO) 是世界領先的工業粘合劑制造商,總部位于德國慕尼黑附近的 Windach 。在美國、中國、新加坡及日本均設有子公司。2019財政年,公司的780名員工創造了1.56億歐元的銷售額。該公司產品在全球范圍內廣泛應用于汽車、消費類電子產品與工業電子產品。幾乎每一部智能手機與超過一半的汽車上都使用該公司產品。DELO 的客戶包括博世、戴姆勒、華為、歐司朗、西門子以及索尼等。

關于 EV Group (EVG)

EV 集團 (EVG) 是為生產半導體、微機電系統 (MEMS)、化合物半導體、功率器件以及納米技術器件制造提供設備與工藝解決方案的領先供應商。該公司主要產品包括晶圓鍵合、薄晶圓處理、光刻/納米壓印光刻技術(NIL)與計量設備,,以及涂膠機、清洗機與檢測系統。EV集團創辦于1980年,可為遍及全球的眾多客戶與合作伙伴提供各類服務與支持。

電子發燒友App

電子發燒友App

評論