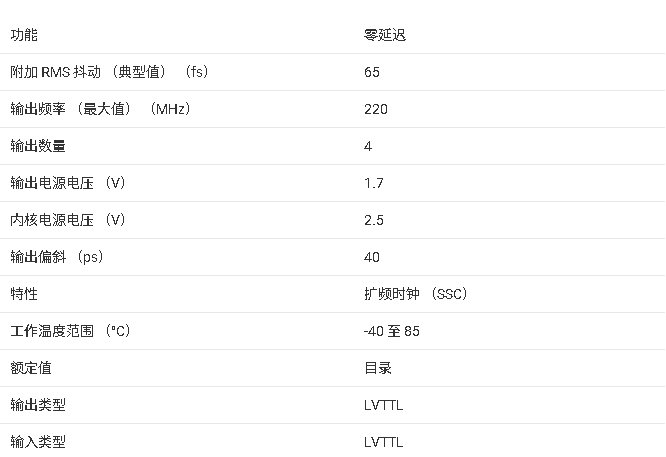

9DBL02x2/9DBL04x2/9DBL06x1/9DBL08x1C:PCIe零延遲/扇出緩沖器的卓越之選 在PCIe設(shè)計(jì)領(lǐng)域,時(shí)鐘緩沖器的性能直接影響著整個(gè)系統(tǒng)的穩(wěn)定性和數(shù)據(jù)傳輸效率。今天

2025-12-30 09:35:06 112

112 數(shù)據(jù)采集是化工企業(yè)數(shù)字化轉(zhuǎn)型的關(guān)鍵第一步,這套30天部署、零延遲運(yùn)行的實(shí)測方案,以高可靠性提供可復(fù)制路徑。當(dāng)設(shè)備數(shù)據(jù)實(shí)現(xiàn)“即時(shí)感知、分析、應(yīng)用”,化工生產(chǎn)的安全與效率將實(shí)現(xiàn)質(zhì)的飛躍。

2025-12-26 10:30:10 195

195

在 “雙碳” 目標(biāo)驅(qū)動下,零碳園區(qū)已成為城市低碳轉(zhuǎn)型的核心載體,其實(shí)施并非單一技術(shù)的堆砌,而是需貫穿 “規(guī)劃 - 建設(shè) - 運(yùn)營 - 優(yōu)化” 全周期的系統(tǒng)工程。不同類型園區(qū)(如產(chǎn)業(yè)園區(qū)、園區(qū)、文旅

2025-12-22 09:34:22 543

543

只需要將 FLASH 內(nèi)的校準(zhǔn)值讀出并寫入 SYSCTRL_LSI.TRIM 即可獲得精準(zhǔn)的 32.8kHz 時(shí)鐘。32.8kHz 頻率校準(zhǔn)值存放地址:0x00012602 - 0x0001 2603。如需其它頻率的時(shí)鐘則需要用戶自行調(diào)整 SYSCTRL_LSI.TRIM 的值。

2025-12-11 07:58:55

FLASH 內(nèi)的校準(zhǔn)值讀出并寫入 SYSCTRL_HSI.TRIM 即可獲得精準(zhǔn)的 48MHz 時(shí)鐘。48MHz 頻率校準(zhǔn)值存放地址為:0x0001 2600 – 0x0001 2601。如需其它頻率

2025-12-08 07:42:39

硬件置 1。注意時(shí)鐘穩(wěn)定標(biāo)志只針對時(shí)鐘啟動過程而言,在時(shí)鐘穩(wěn)定運(yùn)行過程中,檢測到時(shí)鐘運(yùn)行失效不會影響該時(shí)鐘穩(wěn)定標(biāo)志。以 HSE 時(shí)鐘源為例,針對 HSE 時(shí)鐘穩(wěn)定標(biāo)志和時(shí)鐘穩(wěn)定中斷標(biāo)志,說明如下

2025-12-03 06:15:52

Cypress賽普拉斯512Kbit FRAM憑借微秒級寫入、10^14次擦寫壽命及151年數(shù)據(jù)保留,為車載黑匣子EDR提供高可靠數(shù)據(jù)存儲。其-40℃~105℃車規(guī)級工作范圍確保碰撞數(shù)據(jù)完整記錄,滿足汽車安全法規(guī)嚴(yán)苛要求。

2025-12-01 09:47:00 246

246

本文介紹瑞芯微RK3588芯片平臺RT-Linux系統(tǒng)實(shí)時(shí)性及硬件中斷延遲測試,基于觸覺智能RK3588核心板/開發(fā)板演示。Linux-RT實(shí)時(shí)性測試測試環(huán)境說明本次測試是使用Cyclictest

2025-11-28 18:57:35 284

284

實(shí)時(shí)工業(yè)圖像采集卡作為自動化生產(chǎn)線機(jī)器視覺系統(tǒng)的核心硬件,憑借接口、芯片、傳輸協(xié)議等多方面的硬件優(yōu)化實(shí)現(xiàn)低延遲傳輸,適配不同生產(chǎn)線的檢測與控制需求,以下從核心技術(shù)、接口類型、場景適配及選型要點(diǎn)展開說明

2025-11-26 16:23:37 425

425

今年,“零碳園區(qū)”首次被寫入政府工作報(bào)告,正式邁入規(guī)模化發(fā)展“元年”,園區(qū)作為產(chǎn)業(yè)發(fā)展的重要載體,其綠色低碳轉(zhuǎn)型成為了“雙碳”目標(biāo)實(shí)現(xiàn)的強(qiáng)有力抓手。

2025-11-26 11:43:17 566

566 詳細(xì)說明LUA腳本函數(shù)功能和對應(yīng)的應(yīng)用實(shí)例。對于LUA腳本編程有很大的幫助和提高技能。

2025-11-24 16:43:50 0

0 時(shí)鐘周期:

是硬件的時(shí)間單位,由主頻直接決定。類似于音樂的節(jié)拍器,所有操作按此節(jié)奏同步。例如,72MHz 的 CPU 每秒完成 7200 萬次時(shí)鐘周期。

指令周期:

指令周期是軟件視角的耗時(shí)

2025-11-21 07:01:25

富士通16Kbit FRAM憑借微秒級寫入速度與10萬億次擦寫壽命,為圖傳模塊提供高可靠性數(shù)據(jù)存儲。其SPI接口與工業(yè)級溫度范圍(-40℃~85℃)完美適配無人機(jī)、安防監(jiān)控等場景的實(shí)時(shí)數(shù)據(jù)記錄需求。

2025-11-18 09:48:00 317

317

時(shí)鐘周期:一個(gè)時(shí)鐘脈沖所需要的時(shí)間。在計(jì)算機(jī)組成原理中又叫T周期或節(jié)拍脈沖。是CPU和其他單片機(jī)的基本時(shí)間單位。它可以表示為時(shí)鐘晶振頻率(1秒鐘的時(shí)鐘脈沖數(shù))的倒數(shù)(也就是1S/時(shí)鐘脈沖數(shù),比如1

2025-11-17 07:54:39

CW32L010F8U6, 按器件庫CW32L010_StandardPeripheralLib_V1.0.5ExamplesPWRPWR_ConsumptionTest實(shí)例,測試功耗有78uA, 和實(shí)例標(biāo)的電流差太多,另外說明一下,CW32L010F8U6所有IO都沒有連任何其它電路!什么原因?

2025-11-14 07:50:14

我看了下ADC采樣周期可以選擇

00:5 個(gè) ADCCLK 時(shí)鐘周期

01:6 個(gè) ADCCLK 時(shí)鐘周期

10:8 個(gè) ADCCLK 時(shí)鐘周期

11:10 個(gè) ADCCLK 時(shí)鐘周期

那么不同的采樣周期會引起什么樣的變化呢?

2025-11-12 06:25:15

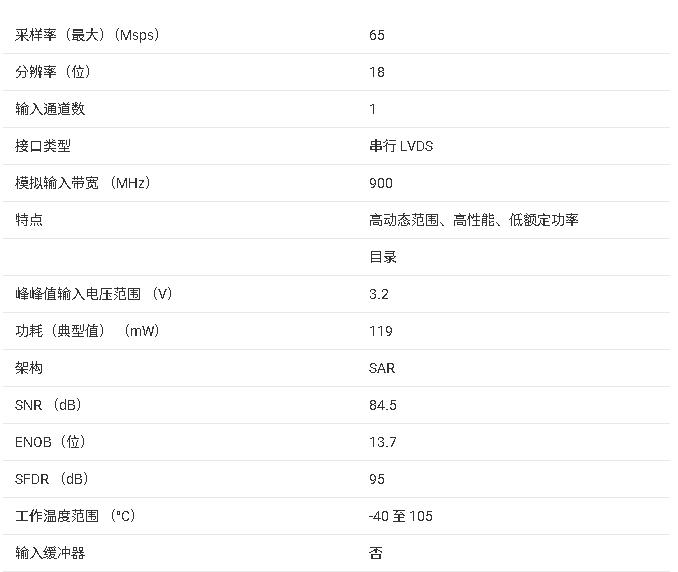

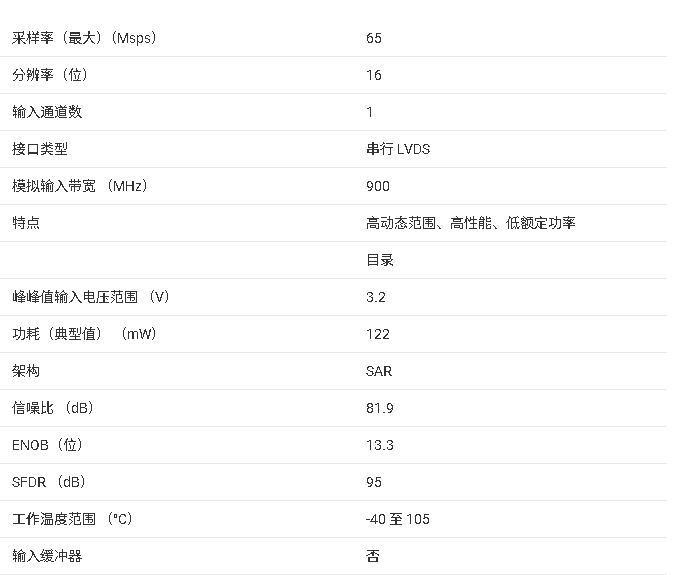

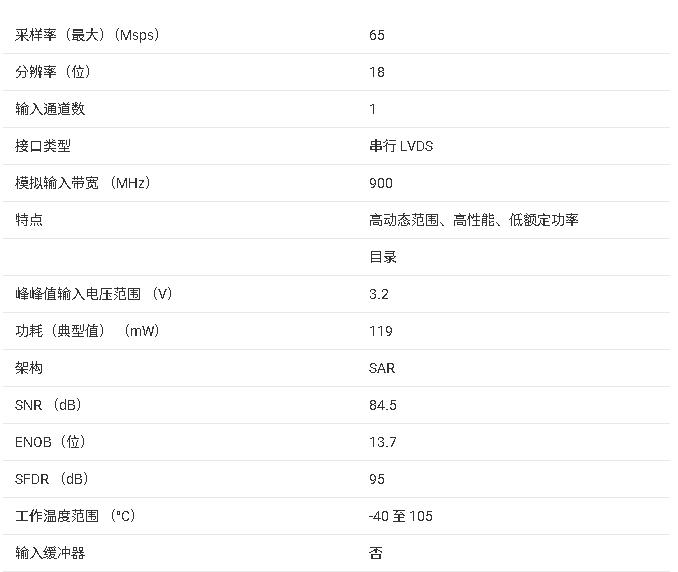

以及出色的線性度和動態(tài)范圍。ADC368x 提供出色的直流精度以及 IF 采樣支持,使其適用于廣泛的應(yīng)用。高速控制環(huán)路受益于低至1個(gè)時(shí)鐘周期的短延遲。ADC在65 Msps時(shí)僅消耗94 mW/ch,其功耗在較低的采樣率下可以很好地?cái)U(kuò)展。

2025-11-01 10:15:54 836

836

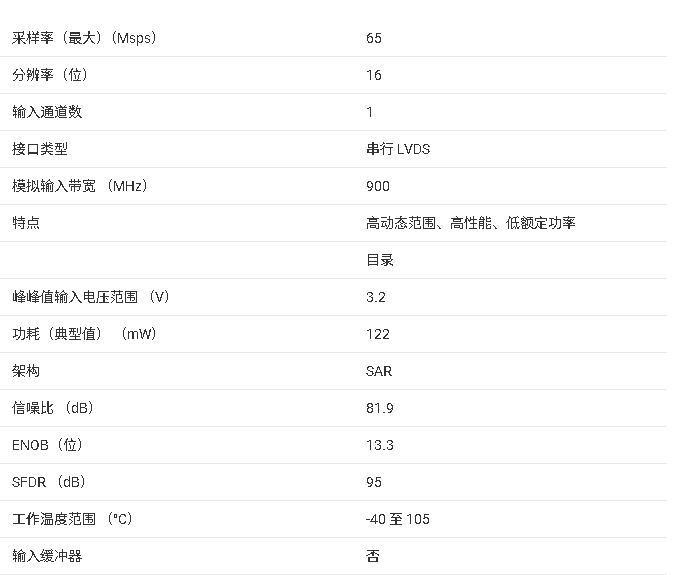

。ADC358x 提供非常好的直流精度以及 IF 采樣支持,使其適用于廣泛的應(yīng)用。高速控制環(huán)路受益于低至1個(gè)時(shí)鐘周期的短延遲。ADC在65 Msps時(shí)僅消耗119 mW,其功耗在較低采樣率下可很好地?cái)U(kuò)展。

2025-10-31 18:14:31 1320

1320

計(jì),可提供–158 dBFS/Hz的噪聲頻譜密度,并結(jié)合出色的線性度和動態(tài)范圍。ADC356x 提供良好的直流精度和 IF 采樣支持,使該器件適用于廣泛的應(yīng)用。高速控制環(huán)路受益于僅一個(gè)時(shí)鐘周期的短延遲。ADC在65 MSPS時(shí)僅消耗122 mW,功耗在較低采樣率下也能很好地?cái)U(kuò)展。

2025-10-31 15:06:13 585

585

身處時(shí)間精度要求極高的行業(yè),我們對時(shí)鐘的守時(shí)能力有著嚴(yán)苛的考量。過去依賴多種授時(shí)手段,總不免遇到些細(xì)微的困擾,比如局部的信號延遲或偶爾的波動。近年來,因工作需要深入接觸了北斗衛(wèi)星校時(shí)時(shí)鐘,它帶來了一種不同的體驗(yàn)。

2025-10-28 14:38:32 234

234

優(yōu)化電路設(shè)計(jì):在電路設(shè)計(jì)中,優(yōu)化關(guān)鍵路徑和信號傳輸路線,使用更高速的邏輯單元和存儲器元件來降低延遲,從而縮短乘法器的運(yùn)算周期。

利用流水線技術(shù):使用流水線技術(shù)將乘法操作分成多個(gè)階段,使每個(gè)階段的操作

2025-10-21 13:17:04

晨控智能采用RFID技術(shù)解決汽車零部件噴涂線體識別難題,實(shí)現(xiàn)高效、穩(wěn)定、精準(zhǔn)的全生命周期追溯。

2025-10-15 15:27:36 274

274 本質(zhì)上就是對數(shù)據(jù)進(jìn)行多級寄存器緩存,延遲時(shí)間以clk的一個(gè)周期為單位,消耗的就是寄存器。比較適合延遲固定周期以及延遲周期比較短的情況。

2025-10-15 10:23:34 539

539

富士通MB85RC04VPNF-G-JNERE1 4Kbit工業(yè)級FRAM,150ns極速寫入、1萬億次擦寫、-40℃~+85℃寬溫,I2C接口低功耗,SOP-8小封裝,為PLC、電表、編碼器等邊緣節(jié)點(diǎn)提供高可靠非易失存儲。

2025-10-10 09:45:00 307

307

理解并掌握先進(jìn)的時(shí)鐘設(shè)計(jì)策略。 下圖展示了典型的時(shí)鐘樹結(jié)構(gòu)(Clock Tree),用于平衡時(shí)鐘延遲與偏斜。 2、核心技術(shù)詳解 I. CTS 優(yōu)化:消除時(shí)序違例的第一步 時(shí)鐘樹綜合(CTS) 是物理設(shè)計(jì)中構(gòu)建平衡時(shí)鐘網(wǎng)絡(luò)的關(guān)鍵步驟,通過插入緩沖器和反相器,實(shí)現(xiàn)最

2025-10-09 10:07:29 361

361 ,零級波片的帶寬較高,而且對溫度變化的敏感性較低。這些波片在各種波長下提供λ/4或λ/2延遲性,并在廣泛光譜范圍內(nèi)提供高效的延遲,是多種紅外線(IR)應(yīng)用的理想之選

2025-09-29 14:29:18

“翻車”;醫(yī)院手術(shù)中設(shè)備停擺,危及患者生命……這些災(zāi)難的背后,都指向一個(gè)關(guān)鍵問題:電力中斷的瞬間,為什么有些設(shè)備能“零延遲”切換到備用電源?答案就藏在UPS(不間斷電

2025-09-28 09:35:16 1977

1977

電壓為 3.3V ~CC~ .

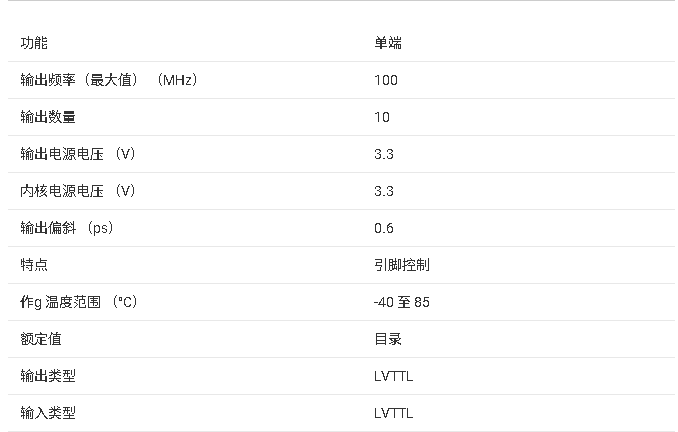

傳播延遲在工廠使用 P0 和 P1 引腳進(jìn)行調(diào)整。工廠調(diào)整可確保零件到零件的偏斜最小化,并保持在指定的窗口內(nèi)。引腳 P0 和 P1 不適合客戶使用,應(yīng)連接到 GND。

2025-09-23 10:26:07 587

587

該CDCVF25084是一款高性能、低偏斜、低抖動、鎖相環(huán)時(shí)鐘乘法器。它使用 PLL 在頻率和相位上將輸出時(shí)鐘精確對齊輸入時(shí)鐘信號,包括 4 的乘法因子。該CDCVF25084在 3.3 V 的標(biāo)稱電源電壓下工作。該器件還在輸出驅(qū)動器中集成了串聯(lián)阻尼電阻器,使其成為驅(qū)動點(diǎn)對點(diǎn)負(fù)載的理想選擇。

2025-09-22 11:30:51 477

477

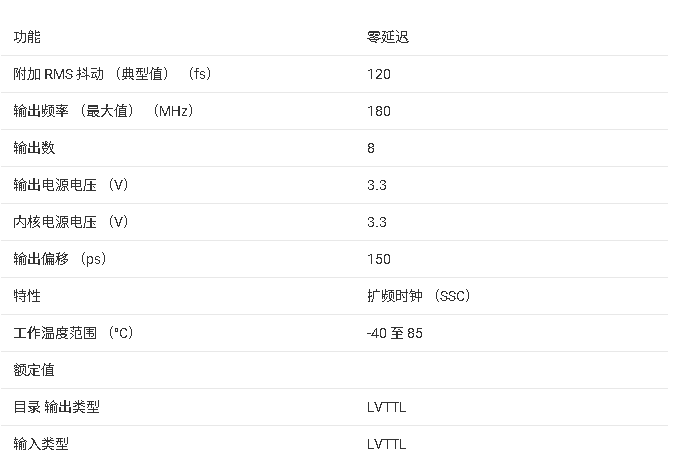

該CDCVF857是一款高性能、低偏斜、低抖動、零延遲緩沖器,可將差分時(shí)鐘輸入對(CLK、CLK)分配給10個(gè)差分時(shí)鐘輸出對(Y[0:9]、Y[0:9])和1個(gè)差分反饋時(shí)鐘輸出對(FBOUT

2025-09-22 09:59:19 503

503

CDCM1802時(shí)鐘驅(qū)動器將一對差分時(shí)鐘輸入分配給一個(gè)LVPECL差分時(shí)鐘輸出對Y0和Y0,以及一個(gè)單端LVCMOS輸出Y1。它專為驅(qū)動 50 Ω輸電線路而設(shè)計(jì)。LVCMOS 輸出在 PECL 輸出級上延遲 1.6 ns,以最大限度地減少信號轉(zhuǎn)換期間的噪聲影響。

2025-09-22 09:28:08 488

488

該CDCU877是一款高性能、低抖動、低偏斜、零延遲緩沖器,可分配差分時(shí)鐘輸入 對(CK、CK)到十個(gè)差分時(shí)鐘輸出對(Yn、Yn)和一個(gè)差分對反饋時(shí)鐘輸出 (FBOUT,F(xiàn)BOUT)。時(shí)鐘輸出由輸入時(shí)鐘

2025-09-19 15:31:17 604

604

該CDCU877是一款高性能、低抖動、低偏斜、零延遲緩沖器,可分配差分時(shí)鐘輸入 對(CK、CK)到十個(gè)差分時(shí)鐘輸出對(Yn、Yn)和一個(gè)差分對反饋時(shí)鐘輸出 (FBOUT,F(xiàn)BOUT)。時(shí)鐘輸出由輸入時(shí)鐘

2025-09-19 14:17:34 643

643

1.3 mUI步長。這種獨(dú)特的功能允許器件通過將需要對齊的時(shí)鐘饋送到DLYCTRL和LEADLAG引腳,在CLKOUT/CLKOUTB和系統(tǒng)中的任何其他CLK之間進(jìn)行相位對齊(零延遲)。此外,它還

2025-09-19 14:07:10 628

628

資源浪費(fèi)” 之間找到動態(tài)平衡。其具體方法可分為四大類,每類均包含 “狀態(tài)感知 - 閾值判斷 - 周期調(diào)整 - 反饋驗(yàn)證” 的閉環(huán)邏輯,以下為詳細(xì)說明: 一、基于 “同步誤差反饋” 的動態(tài)調(diào)整(核心基礎(chǔ)方法) 該方法以 “實(shí)際同步誤差”

2025-09-19 11:31:56 531

531 該CDCVF855是一款高性能、低偏斜、低抖動、零延遲緩沖器,可將差分時(shí)鐘輸入對(CLK、CLK)分配給4個(gè)差分時(shí)鐘輸出對(Y[0:3]、Y[0:3])和1對差分反饋時(shí)鐘輸出(FBOUT、FBOUT

2025-09-19 10:01:29 472

472

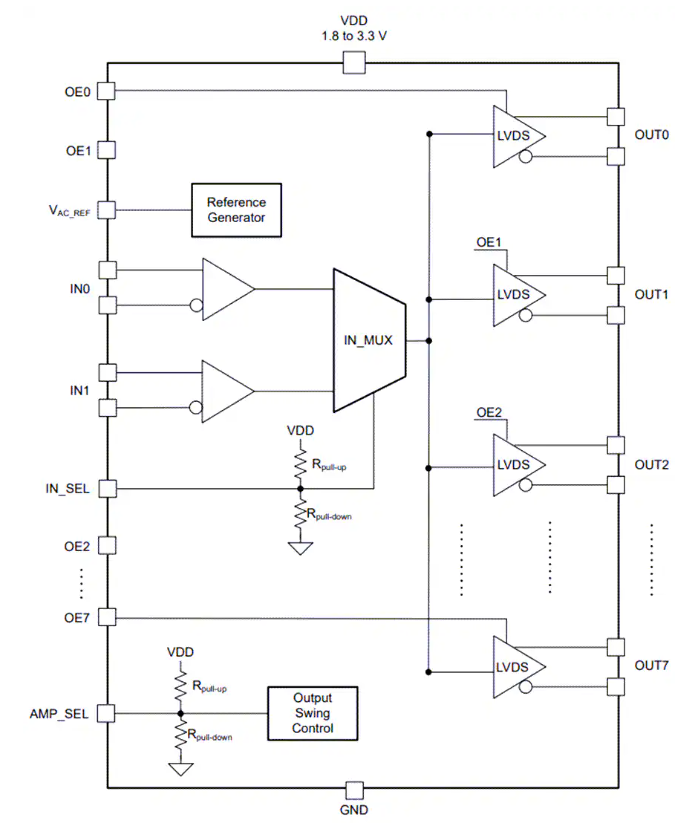

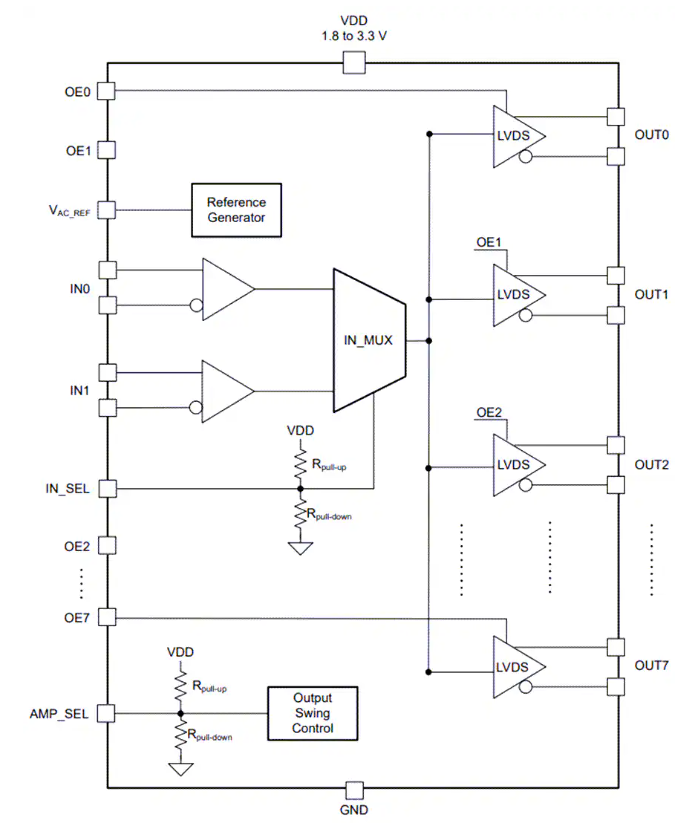

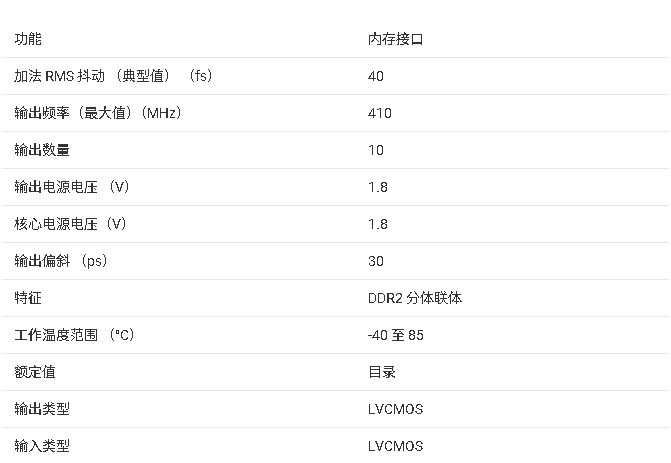

Texas Instruments LMK1D1208P 8通道輸出LVDS時(shí)鐘緩沖器將兩個(gè)中的一個(gè)可選時(shí)鐘輸入(IN0和IN1)分配給八對差分LVDS時(shí)鐘輸出(OUT0至OUT7)。通過超小延遲實(shí)現(xiàn)時(shí)鐘分配。輸入可以為LVDS、LVPECL、LVCMOS、HCSL或CML。

2025-09-18 09:52:54 651

651

該CDCUA877是一款高性能、低抖動、低偏斜、零延遲緩沖器,可將差分時(shí)鐘輸入對(CK、CK)分配給十個(gè)差分時(shí)鐘輸出對(Yn、Yn)和一個(gè)差分反饋時(shí)鐘輸出對(FBOUT、FBOUT)。時(shí)鐘輸出由輸入時(shí)鐘

2025-09-12 09:52:57 602

602

5G網(wǎng)絡(luò)的高速率、低延遲、廣連接,都離不開一個(gè)關(guān)鍵支撐——高精度時(shí)鐘。在基站、核心網(wǎng)和終端設(shè)備中,晶振就是保證時(shí)鐘精度的“隱形英雄”。 一、5G對時(shí)鐘的嚴(yán)苛要求 毫秒級延遲→納秒級同步:5G要實(shí)現(xiàn)

2025-09-11 14:46:06 529

529 富士通256Kbit FRAM MB85RS256BPNF-G-JNERE1為LED顯示系統(tǒng)提供高速、高耐久性數(shù)據(jù)存儲方案,支持納秒級寫入與10^12次擦寫,解決傳統(tǒng)存儲器延遲高、壽命短問題,適用于智能交通、戶外廣告等嚴(yán)苛環(huán)境,顯著提升系統(tǒng)響應(yīng)與可靠性。

2025-09-11 09:45:00 480

480

影響)

SYNC(異步) + SYSREF(周期性參考)

中等精度同步需求(如通信基站)

Subclass 2

嚴(yán)格同步(SYSREF 周期性觸發(fā) + 時(shí)鐘對齊)

支持亞周期級可重復(fù)確定性延遲(精度達(dá)樣本周期

2025-09-05 21:18:18

在電子系統(tǒng)設(shè)計(jì)中,時(shí)鐘信號的穩(wěn)定與可靠性對于整個(gè)系統(tǒng)的正常運(yùn)行至關(guān)重要。為了確保時(shí)鐘信號在傳輸過程中不會受到干擾或延遲,工程師們通常會使用一種名為“時(shí)鐘緩沖器”的裝置。本文將探討時(shí)鐘緩沖器的應(yīng)用條件

2025-09-04 15:01:45 673

673

Cypress 64Kbit FRAM以納秒寫入、萬億次擦寫、微瓦功耗,破解手持檢測器數(shù)據(jù)丟幀、壽命及續(xù)航痛點(diǎn),覆蓋-40℃~85℃,50G抗震,直接替代EEPROM,30天續(xù)航,零掉電丟數(shù)。

2025-08-28 09:45:00 434

434

1.文件運(yùn)行 導(dǎo)入工程 雙擊運(yùn)行桌面GraniStudio.exe。 通過引導(dǎo)界面導(dǎo)入IO寫入例程,點(diǎn)擊導(dǎo)入按鈕。 打開IO寫入例程所在路徑,選中IO寫入.gsp文件,點(diǎn)擊打開,完成導(dǎo)入。 2.功能說明

2025-08-22 16:47:07 667

667

至1MHz,還具有包括逐周期電流限制、UVLO和過溫保護(hù)等功能。

產(chǎn)品特點(diǎn)#增強(qiáng)型零電壓開關(guān)(ZVS)范圍#直接同步整流器(SR)控制#輕負(fù)載效率管理包括突發(fā)模式運(yùn)行斷續(xù)導(dǎo)通模式(DCM),支持可編程

2025-08-18 11:23:23

零時(shí)刻信號。

純分享帖,點(diǎn)擊下方附件免費(fèi)獲取完整資料~~~

內(nèi)容有幫助可以關(guān)注、點(diǎn)贊、評論支持一下,謝謝!

【免責(zé)聲明】本文系網(wǎng)絡(luò)轉(zhuǎn)載,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請第一時(shí)間告知,刪除內(nèi)容,謝謝!

2025-08-07 14:37:39

本文通過分析反電動勢過零點(diǎn)硬件檢測電路,研究了該電路使反電動勢過零點(diǎn)信號延遲角度大小的計(jì)算問題。得出已有延遲角度計(jì)算公式不符合該電路,重新推導(dǎo)了延遲角度計(jì)算公式,并通過Multisum軟件搭建仿真

2025-08-07 14:13:22

零時(shí)刻信號。

純分享帖,點(diǎn)擊下方附件免費(fèi)獲取完整資料~~~

內(nèi)容有幫助可以關(guān)注、點(diǎn)贊、評論支持一下,謝謝!

【免責(zé)聲明】本文系網(wǎng)絡(luò)轉(zhuǎn)載,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請第一時(shí)間告知,刪除內(nèi)容,謝謝!

2025-08-05 14:41:06

EV12AS200A的“采樣延遲微調(diào)”功能本質(zhì)上是在 ADC采樣時(shí)鐘路徑里插入一條可編程、步進(jìn) 24 fs 的延遲線(Delay Line)。通過亞皮秒級的時(shí)間位移,把不同通道或不同芯片的采樣沿拉到

2025-08-04 08:46:00

融智興科技推出的RFID超高頻零售標(biāo)簽,專為零售場景高頻次、多品類、快速周轉(zhuǎn)而設(shè)計(jì),具備遠(yuǎn)距離群讀、批量寫入、耐環(huán)境干擾等特點(diǎn),并通過了ARC(Auburn RFID Lab)認(rèn)證,滿足沃爾瑪、山姆會員店等全球零售巨頭的標(biāo)準(zhǔn)。

2025-07-30 16:32:48 640

640

賽普拉斯2 Mbit FRAM FM25V20A-DG以40 MHz SPI總線、1012次擦寫壽命和100 krad(Si)抗輻射能力,取代呼吸機(jī)中EEPROM與SRAM加電池的傳統(tǒng)方案,為智能生命支持系統(tǒng)提供原子級可靠的數(shù)據(jù)存儲基石。

2025-07-24 11:25:44 520

520

,當(dāng)時(shí)鐘信號需要在長距離傳輸時(shí),信號的抖動和延遲問題會變得尤為突出。時(shí)鐘信號的抖動是指信號的頻率波動或不穩(wěn)定,這可能導(dǎo)致系統(tǒng)中的時(shí)序問題和數(shù)據(jù)錯(cuò)誤。而時(shí)鐘信號的延

2025-07-15 17:27:11 506

506

在高速數(shù)字通信和射頻系統(tǒng)中,信號從發(fā)送端到接收端的傳輸過程中會遇到各種失真和畸變。群延遲(Group Delay)作為描述系統(tǒng)相位線性度的重要參數(shù),直接影響著信號保真度和系統(tǒng)性能。本文將深入淺出地介紹群延遲的基本概念、應(yīng)用場景,并通過仿真示例展示其在實(shí)際工程中的重要性。

2025-07-08 15:14:51 1693

1693

CYW20706的生命周期狀態(tài)如何? 我注意到CYW20706不再列在AIROC? Bluetooth? LE& Bluetooth? 下。貿(mào)澤現(xiàn)在還將該器件列為不建議用于未來設(shè)計(jì)。

對于CYW20706來說,什么是好的更換零件。 還會有支持 LE Audio 的雙棧藍(lán)牙 SoC 嗎?

2025-07-04 07:25:41

汽車零部件的疲勞耐久測試是保障整車可靠性的核心環(huán)節(jié),其通過模擬復(fù)雜工況下的交變載荷、環(huán)境因素等,驗(yàn)證零部件在全生命周期內(nèi)的抗疲勞破壞能力。本文從測試對象分類、典型測試項(xiàng)目、技術(shù)要點(diǎn)及新能源趨勢等維度展開說明。

2025-06-17 09:12:28 2018

2018

汽車零部件開發(fā)項(xiàng)目管理是一個(gè)涉及多環(huán)節(jié)、多部門協(xié)作的復(fù)雜過程,需從項(xiàng)目啟動到交付全流程進(jìn)行科學(xué)規(guī)劃與管控。以下從 核心流程 、 關(guān)鍵要素 、 管理工具 及 挑戰(zhàn)與應(yīng)對策略 四方面展開說明: 一、核心

2025-06-09 13:26:35 1270

1270 STC8H 單片機(jī) + RA8889/RA6809:重新定義嵌入式觸控交互_高流暢、低延遲、零基礎(chǔ)的人機(jī)界面

2025-05-28 16:01:58 956

956

ServiceAbility的生命周期

開發(fā)者可以根據(jù)業(yè)務(wù)場景重寫生命周期相關(guān)接口。ServiceAbility生命周期接口說明見下表。

表1 ServiceAbility生命周期接口說明

接口名

2025-05-28 08:22:01

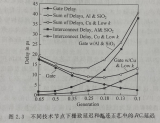

隨著集成電路技術(shù)節(jié)點(diǎn)的不斷減小以及互連布線密度的急劇增加,互連系統(tǒng)中電阻、電容帶來的 RC耦合寄生效應(yīng)迅速增長,影響了器件的速度。圖2.3比較了不同技術(shù)節(jié)點(diǎn)下門信號延遲(gate delay)和互連

2025-05-23 10:43:25 1266

1266

時(shí),它顯示“取決于水印級別”。 我們?nèi)绾未_定這個(gè)值? 緩沖區(qū)寫入超過水印級別和 WATERMARK 標(biāo)志置位之間的周期延遲是多少?

為了解釋上述(1)和(2),我們還需要將這些狀態(tài)納入我們的狀態(tài)機(jī),以便

2025-05-20 07:15:52

UIAbility組件生命周期

概述

當(dāng)用戶打開、切換和返回到對應(yīng)應(yīng)用時(shí),應(yīng)用中的UIAbility實(shí)例會在其生命周期的不同狀態(tài)之間轉(zhuǎn)換。UIAbility類提供了一系列回調(diào),通過這些回調(diào)可以

2025-05-16 08:28:23

的啟動頁面

應(yīng)用中的UIAbility在啟動過程中,需要指定啟動頁面,否則應(yīng)用啟動后會因?yàn)闆]有默認(rèn)加載頁面而導(dǎo)致白屏。可以在UIAbility的onWindowStageCreate()生命周期回調(diào)中

2025-05-16 06:32:33

實(shí)例。

圖1 單實(shí)例模式演示效果

說明:

應(yīng)用的UIAbility實(shí)例已創(chuàng)建,該UIAbility配置為單實(shí)例模式,再次調(diào)用startAbility()方法啟動該UIAbility實(shí)例。由于啟動

2025-05-16 06:10:19

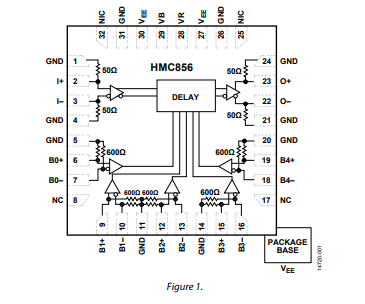

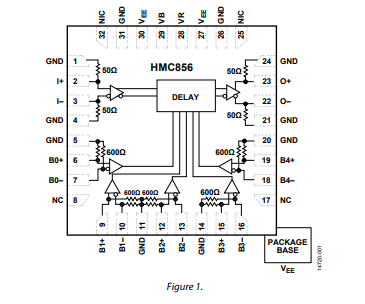

HMC856LC5是一款寬帶時(shí)間延遲器件,具有5位數(shù)字控制功能,設(shè)計(jì)用于時(shí)序補(bǔ)償或時(shí)鐘偏斜管理應(yīng)用。 時(shí)間延遲提供接近100 ps的延遲范圍,具有3 ps分辨率,支持28 Gbps數(shù)據(jù)。 單調(diào)延遲針對電源和溫度變化范圍內(nèi)的穩(wěn)定工作進(jìn)行補(bǔ)償。 延遲直流耦合,并支持寬帶工作。

2025-04-16 11:31:59 813

813

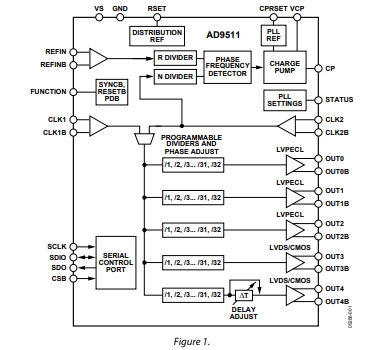

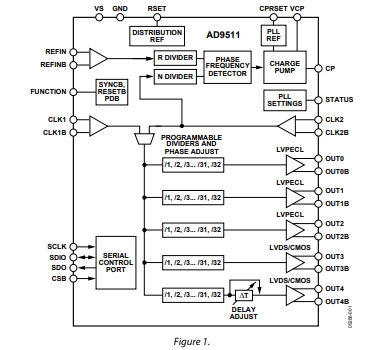

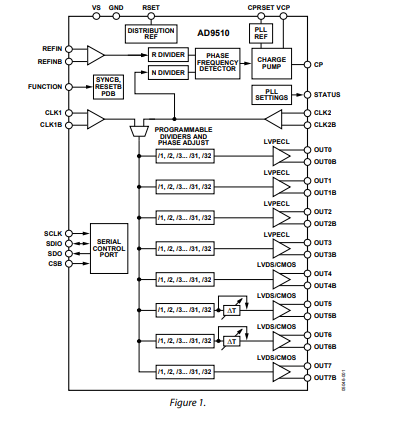

AD9511提供多路輸出時(shí)鐘分配功能,并集成一個(gè)片內(nèi)鎖相環(huán)(PLL)內(nèi)核。它具有低抖動和低相位噪聲特性,能夠極大地提升數(shù)據(jù)轉(zhuǎn)換器的時(shí)鐘性能。3路獨(dú)立的LVPECL時(shí)鐘輸出和2路LVDS時(shí)鐘輸出工作頻率分別為1.2 GHz和800 MHz。可選的CMOS時(shí)鐘輸出工作頻率為250 MHz。

2025-04-15 13:48:04 959

959

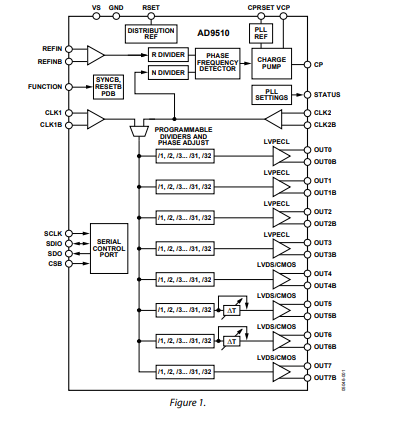

AD9510提供多路輸出時(shí)鐘分配功能,并集成一個(gè)片內(nèi)鎖相環(huán)(PLL)內(nèi)核。它具有低抖動和低相位噪聲特性,能夠極大地提升數(shù)據(jù)轉(zhuǎn)換器的時(shí)鐘性能。4路獨(dú)立的LVPECL時(shí)鐘輸出和4路LVDS時(shí)鐘輸出工作頻率分別為1.2 GHz和800 MHz。可選的CMOS時(shí)鐘輸出工作頻率為250 MHz。

2025-04-15 11:41:58 809

809

,在網(wǎng)上找到的一些解釋都比較模糊,沒有具體的案例說明問題出現(xiàn)的原因和解決方案。

把其他的代碼全部注釋掉,只保留Flash和串口打印相關(guān)的代碼,再次執(zhí)行,發(fā)現(xiàn)返回值都是9,說明擦除和寫入無異常。

請問

2025-03-11 06:08:09

充電樁的CCC認(rèn)證周期通常為2-4個(gè)月,具體時(shí)間取決于產(chǎn)品類型、測試項(xiàng)目復(fù)雜度、工廠檢查安排等因素。以下是詳細(xì)的認(rèn)證周期分解:一、前期準(zhǔn)備(1-2周)1.資料準(zhǔn)備:-產(chǎn)品技術(shù)文件(電氣原理圖、關(guān)鍵件

2025-03-07 17:37:44 3591

3591

【硬件資源】

RTC 時(shí)鐘模塊是一個(gè)時(shí)間外設(shè),主要用于日期時(shí)間的存儲和控制,有別于一般 MCU中的 Timer,RTC 時(shí)鐘有兩種計(jì)時(shí)模式,日期模式和計(jì)時(shí)模式,在日期模式下,RTC可以準(zhǔn)確地記錄年

2025-03-07 16:45:02

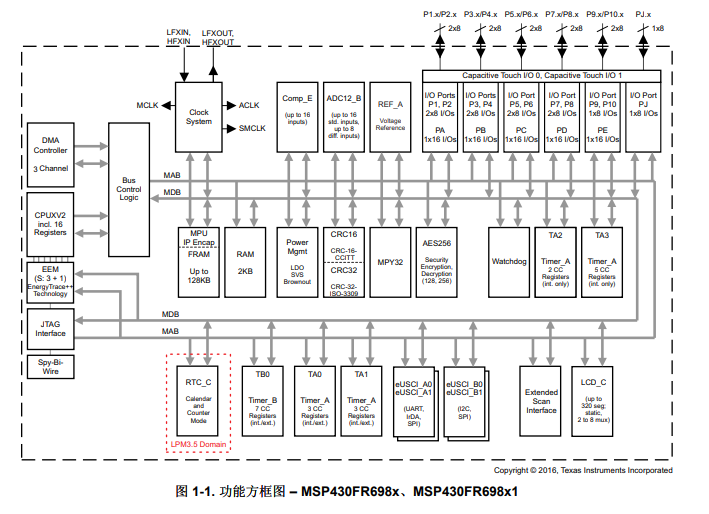

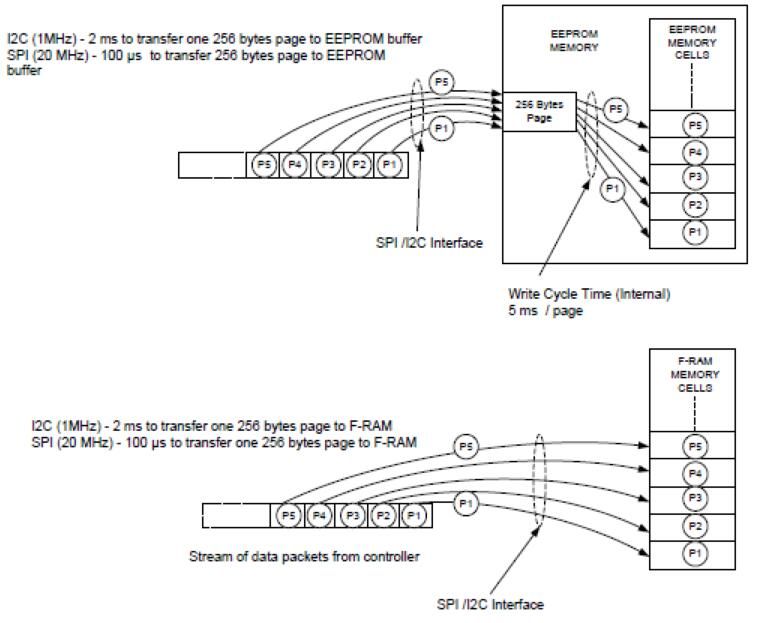

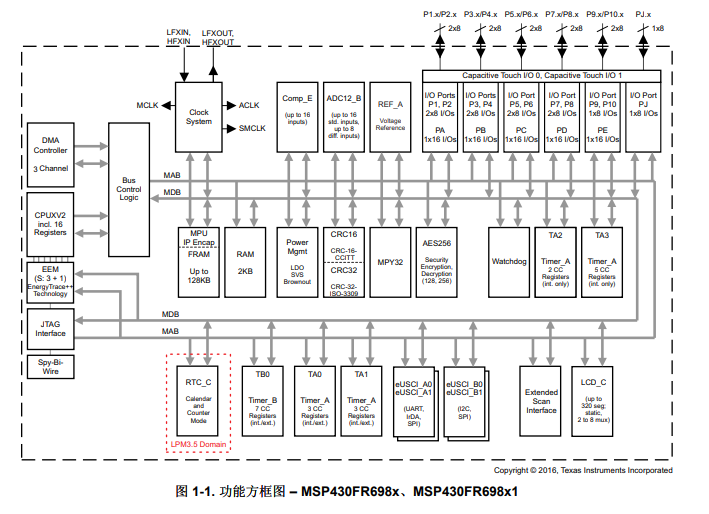

MSP430?超低功耗(ULP)FRAM平臺將獨(dú)特的嵌入式FRAM和整體超低功耗系統(tǒng)架構(gòu)組合在一起,從而使得創(chuàng)新人員能夠以較少的能源預(yù)算增加性能。FRAM技術(shù)以低很多的功耗將SRAM的速度、靈活性和耐久性與閃存的穩(wěn)定性和可靠性組合在一起。

2025-03-04 17:11:15 1073

1073

你好,請問關(guān)于DVALID信號,load、reset、以及noop操作都需要行周期的最后一個(gè)時(shí)鐘拉低嗎?拉低的這一個(gè)時(shí)鐘周期是以200MHZ為單位還是400MHz?

2025-02-24 06:59:27

所有數(shù)字延遲發(fā)生器都通過計(jì)算快速時(shí)鐘(通常為 100 MHz)的周期來測量時(shí)間間隔。大多數(shù)數(shù)字延遲發(fā)生器還具有較短的可編程模擬延遲,以實(shí)現(xiàn)比時(shí)鐘周期更精細(xì)的時(shí)間間隔。不幸的是,如果觸發(fā)器與時(shí)鐘不同步

2025-02-14 13:50:17

到低電平 1G 為低時(shí)的狀態(tài)。 可在 1.8V、2.5V 和 3.3V 電源電壓下工作,工作溫度范圍為-55℃~+125℃。a) 高性能 1:12 LVCMOS 時(shí)鐘緩沖器;?b) 極低的附加抖動<25fs 標(biāo)稱值?c) 輸出偏斜<55ps(典型);?d) 非常低的傳播延遲<

2025-02-13 17:43:37 0

0 到低電平 1G 為低時(shí)的狀態(tài)。 可在 1.8V、2.5V 和 3.3V 電源電壓下工作,工作溫度范圍為-55℃~+125℃。a) 高性能 1:10 LVCMOS 時(shí)鐘緩沖器;?b) 極低的附加抖動<25fs 標(biāo)稱值;?c) 輸出偏斜<55ps(典型);?d) 非常低的傳播延遲

2025-02-13 17:42:53 0

0 到低電平 1G 為低時(shí)的狀態(tài)。 可在 1.8V、2.5V 和 3.3V 電源電壓下工作,工作溫度范圍為-55℃~+125℃。a) 高性能 1:8 LVCMOS 時(shí)鐘緩沖器;b) 極低的附加抖動<25fs 標(biāo)稱值 c) 輸出偏斜<55ps(典型);d) 非常低的傳播延遲<3ns;?e) 同步輸出啟

2025-02-13 17:42:16 0

0 到低電平 1G 為低時(shí)的狀態(tài)。 可在 1.8V、2.5V 和 3.3V 電源電壓下工作,工作溫度范圍為-55℃~+125℃。a) 高性能 1:6 LVCMOS 時(shí)鐘緩沖器;?b) 極低的附加抖動<25fs 標(biāo)稱值;c) 輸出偏斜<55ps(典型);?d) 非常低的傳播延遲<3ns;e)

2025-02-13 17:41:11 0

0 到低電平 1G 為低時(shí)的狀態(tài)。 可在 1.8V、2.5V 和 3.3V 電源電壓下工作,工作溫度范圍為-55℃~+125℃。a) 高性能 1:4 LVCMOS 時(shí)鐘緩沖器;?b) 極低的附加抖動<25fs 標(biāo)稱值;?c) 輸出偏斜<55ps(典型);?d) 非常低的傳播延遲<

2025-02-13 17:40:24 1

1

ADS5560的DataSheet上只給出了在20MSPS和40MSPS采樣率下,輸入時(shí)鐘到輸出時(shí)鐘的延遲,即t_PDI;請問,當(dāng)ADS5560工作在DDR LVDS模式下,采樣率為30MSPS時(shí),對應(yīng)的時(shí)鐘延遲是多少?

2025-02-13 07:50:14

現(xiàn)有如下問題

1、如果SPI時(shí)鐘不能保證數(shù)據(jù)在tdr內(nèi)完全傳出,那么這是從SPI口出的數(shù)據(jù)是否都為0

2、tdr之前問過,ti專家說就是采樣周期。如果是這樣,那么我設(shè)定ADS1298采樣率為

2025-02-13 06:55:49

AFE5801在講解TGC 控制reg時(shí),說Tclk是通道采樣時(shí)鐘,是設(shè)備輸入時(shí)鐘周期的兩倍,這是為什么?采樣時(shí)鐘跟輸入時(shí)鐘不是應(yīng)該一樣的嗎?比如說我的采樣率為1.8MHz,那么輸入時(shí)鐘fclkin應(yīng)該輸入多少?Tclk又等于多少?

2025-02-11 07:01:21

HMC856LC5是一款寬帶時(shí)間延遲器件,具有5位數(shù)字控制功能,設(shè)計(jì)用于時(shí)序補(bǔ)償或時(shí)鐘偏斜管理應(yīng)用。 時(shí)間延遲提供接近100 ps的延遲范圍,具有3 ps分辨率,支持28 Gbps數(shù)據(jù)。 單調(diào)延遲

2025-02-10 11:45:55

1、數(shù)據(jù)手冊第16頁給出的雙通道掃描模式的時(shí)序圖中,READ信號是芯片內(nèi)部產(chǎn)生的信號還是外部施加的信號?如果是內(nèi)部產(chǎn)生的,第19管腳的/RD信號需要施加怎樣的信號?按照說明,數(shù)據(jù)是在每個(gè)時(shí)鐘的下降

2025-02-10 08:36:33

HMC856LC5是一款寬帶時(shí)間延遲器件,具有5位數(shù)字控制功能,設(shè)計(jì)用于時(shí)序補(bǔ)償或時(shí)鐘偏斜管理應(yīng)用。 時(shí)間延遲提供接近100 ps的延遲范圍,具有3 ps分辨率,支持28 Gbps數(shù)據(jù)。 單調(diào)延遲

2025-02-08 14:46:52

HMC856LC5是一款寬帶時(shí)間延遲器件,具有5位數(shù)字控制功能,設(shè)計(jì)用于時(shí)序補(bǔ)償或時(shí)鐘偏斜管理應(yīng)用。 時(shí)間延遲提供接近100 ps的延遲范圍,具有3 ps分辨率,支持28 Gbps數(shù)據(jù)。 單調(diào)延遲

2025-02-08 11:01:07

發(fā)送寄存器數(shù)目和數(shù)據(jù),每個(gè)字節(jié)的間隔滿足5個(gè)時(shí)鐘周期的要求,但讀出寄存器的值始終為零。不解問題出現(xiàn)在哪里,三否在發(fā)送每個(gè)字節(jié)前應(yīng)該先判斷/DRDY為0時(shí),然后再發(fā)送?硬件電路按參考電路來的,也測試過,不存在問題,肯定問題在SPI上,始終搞不定,急死,望各位高手指點(diǎn)一二,非常感激!!!

2025-02-06 08:32:39

1、數(shù)據(jù)手冊第16頁給出的雙通道掃描模式的時(shí)序圖中,READ信號是芯片內(nèi)部產(chǎn)生的信號還是外部施加的信號?如果是內(nèi)部產(chǎn)生的,第19管腳的/RD信號需要施加怎樣的信號?按照說明,數(shù)據(jù)是在每個(gè)時(shí)鐘的下降

2025-02-05 07:45:44

這時(shí)序圖是說明ADS805E這款芯片的轉(zhuǎn)換結(jié)果要延后六個(gè)采樣周期才輸出嗎?即圖中的Analog In中的N點(diǎn)對應(yīng)的轉(zhuǎn)換后的Data Out中的N 嗎?還是說,這時(shí)序圖是說明此芯片在上電后的前六個(gè)

2025-01-23 07:50:40

運(yùn)行。 ? Flexus X 實(shí)例具備優(yōu)異的 靈活性和擴(kuò)展性 ,支持按需調(diào)整計(jì)算、存儲和網(wǎng)絡(luò)資源,以滿足各種業(yè)務(wù)需求。其增強(qiáng)的安全性和可靠性,結(jié)合按需付費(fèi)模式,提供了更高的性價(jià)比和成本控制能力。 說了這么多,眼見為實(shí),讓我們用 零信任訪問 Next

2025-01-22 17:57:41 807

807

影響25Q20D閃存芯片寫入速度和使用壽命的因素有哪些?首先我們來談?wù)動绊?b class="flag-6" style="color: red">寫入速度九個(gè)方面:存儲容量和架構(gòu):存儲容量的增加會導(dǎo)致芯片內(nèi)部的數(shù)據(jù)管理和尋址更為復(fù)雜,從而影響寫入速度。較大的閃存芯片在寫數(shù)據(jù)時(shí),需要更多時(shí)間來定位和管理數(shù)據(jù)。此外,如果閃存的存儲架構(gòu)未經(jīng)優(yōu)化,同樣會限制寫入速度。

2025-01-22 16:48:25 1099

1099

等于轉(zhuǎn)換速率。

當(dāng)我在看TLC5510的datasheet時(shí),發(fā)現(xiàn)從模擬電壓信號輸入到數(shù)字信號輸出,要有2.5個(gè)時(shí)鐘周期的延遲,請問這個(gè)延遲時(shí)間是“ADC完成一次從模擬到數(shù)字轉(zhuǎn)換”需要的時(shí)間嗎?但是

2025-01-22 06:46:08

我在AVDD為5V,DVDD為3.3V,工作頻率為25M,SCLK為6.25M,F(xiàn)rame_Sync模式的情況下使用ADS1271,模擬輸入端為零時(shí)輸出數(shù)據(jù)的高幾位(大概是D23到D12)為什么總是高電平?理論上只有最高位才有可能是高電平的么。

2025-01-17 06:23:00

使用TM4C123GH6PGE的SSI模塊產(chǎn)生驅(qū)動信號,因?yàn)槠渥疃嘁淮沃荒馨l(fā)送16位數(shù)據(jù),因此產(chǎn)生的時(shí)鐘信號如圖。

由于ADS8688要求在每一個(gè)轉(zhuǎn)換周期內(nèi)幀同步信號至少應(yīng)保持32個(gè)系統(tǒng)時(shí)鐘周期

2025-01-13 06:52:38

影響HT25Q20D閃存芯片寫入速度和使用壽命的因素有哪些?

2025-01-08 16:05:03 1429

1429 電子發(fā)燒友網(wǎng)站提供《EE-197:ADSP-BF531/532/533 Blackfin處理器多周期指令和延遲.pdf》資料免費(fèi)下載

2025-01-08 14:39:05 0

0 、零售、金融、游戲等眾多領(lǐng)域的通用工作負(fù)載需求。本文旨在詳細(xì)闡述如何高效利用“云服務(wù)器 Flexus X 實(shí)例”,包括如何在其中從零開始,通過安裝相關(guān)依賴、安裝 Docker、安裝 Gitea 等步驟,實(shí)現(xiàn)自己的 Git 倉庫,管理本地代碼。精彩內(nèi)容,不容錯(cuò)過,快來一探究

2025-01-07 16:59:54 840

840

電子發(fā)燒友網(wǎng)站提供《EE-171:ADSP-BF535 Blackfin處理器多周期指令和延遲.pdf》資料免費(fèi)下載

2025-01-05 09:47:40 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論