9DBL02x2/9DBL04x2/9DBL06x1/9DBL08x1C:PCIe零延遲/扇出緩沖器的卓越之選

在PCIe設計領域,時鐘緩沖器的性能直接影響著整個系統的穩定性和數據傳輸效率。今天,我們就來深入探討Renesas推出的9DBL02x2/9DBL04x2/9DBL06x1/9DBL08x1C系列2至8輸出3.3V PCIe零延遲/扇出緩沖器,看看它究竟有哪些獨特之處。

文件下載:Renesas Electronics 9DBL0x扇出緩沖器.pdf

產品概述

9DBL02x2/9DBL04x2/9DBL06x1/9DBL08x1C是Renesas全功能PCIe系列中的低功耗、高性能成員。它支持PCIe Gen1至Gen5,適用于多種PCIe時鐘架構,包括常見的Common Clocked(CC)和Independent Reference(IR)(帶或不帶擴頻功能,即SRIS和SRNS)。

典型應用場景

- PCIe Riser Cards:為PCIe擴展卡提供穩定的時鐘信號,確保數據的高速、準確傳輸。

- nVME Storage:滿足高速存儲設備對時鐘信號的嚴格要求,提升存儲性能。

- Networking:在網絡設備中保證時鐘同步,減少數據傳輸延遲。

- Accelerators:為加速器提供精確的時鐘,提高計算效率。

- Industrial Control/Embedded:適應工業控制和嵌入式系統的復雜環境,確保系統的可靠性。

關鍵規格亮點

- 低抖動性能:在扇出模式下,PCIe Gen5 CC附加抖動小于60fs RMS;在高帶寬零延遲緩沖器(ZDB)模式下,PCIe Gen5 CC抖動小于150fs RMS。如此低的抖動,為高速數據傳輸提供了堅實的保障。

- 低功耗設計:2至8個低功耗HCSL(LP - HCSL)輸出,每個輸出對可省去4個電阻,有效降低功耗。

- 集成終端電阻:9DBLxx4x設備提供集成的100Ω終端電阻,9DBLxx5x設備提供集成的85Ω終端電阻,簡化了設計,減少了外部元件數量。

- 擴頻兼容性:支持擴頻功能,可有效降低電磁干擾(EMI)。

- 靈活的控制接口:每個輸出都有專用的OE#引腳,方便進行輸出控制;具備3個可選的SMBus地址,可通過SMBus接口進行廣泛的功能配置,以滿足不同客戶的需求。

- 寬工作溫度范圍:可在 - 40°C至 + 85°C的溫度范圍內正常工作,適應各種惡劣環境。

- 節省空間的封裝:提供多種不同尺寸的VFQFPN封裝,如4×4 mm 24 - VFQFPN(9DBL02x2C)、5×5 mm 32 - VFQFPN(9DBL04x2C)等,滿足不同設計的空間要求。

詳細技術分析

引腳信息

該系列產品的不同型號在引腳分配上有所差異,但都有明確的功能定義。例如,^CKPWRGD_PD#引腳用于通知設備采樣鎖存輸入并啟動,低電平進入掉電模式,后續高電平退出掉電模式;CLK_IN和CLK_IN#是差分輸入時鐘的正、負輸入引腳等。通過合理的引腳布局和功能設計,確保了信號的準確輸入和輸出。

規格參數

絕對最大額定值

在使用過程中,需要注意一些絕對最大額定值,如電源電壓VDDx范圍為 - 0.5V至3.9V,輸入電壓VIN范圍為 - 0.5V至VDD + 0.5V等。超出這些額定值可能會對設備造成損壞,影響其可靠性和使用壽命。

熱特性

不同型號的產品在熱特性上有所不同,例如9DBL08xxC的熱阻在不同條件下有相應的典型值。了解熱特性有助于在設計散熱方案時做出合理的決策,確保設備在正常溫度范圍內工作。

電氣規格

在電氣性能方面,該系列產品表現出色。例如,在不同的PCIe Gen標準下,其附加相位抖動都嚴格控制在一定范圍內。以PCIe Gen5為例,在CC架構下,典型的附加相位抖動僅為0.014ps RMS,遠低于行業限制。此外,輸入和輸出的各項參數也都滿足設計要求,如輸入的交叉電壓、擺幅、壓擺率等,輸出的占空比、偏斜和PLL特性等。

測試負載

為了準確測量產品的各項性能指標,需要使用特定的測試負載。文檔中給出了用于AC/DC測量和ZDB模式PCIe抖動測量的測試負載圖,以及相應的參數設置。通過這些測試負載和測量方法,可以確保產品的性能符合規格要求。

替代終端

LP - HCSL輸出可以輕松驅動其他邏輯家族。對于不同型號的設備,在替代HCSL終端方面有不同的配置,如9DBLxx4xC在不同差分阻抗下的終端電阻配置等。這些替代終端方案為設計提供了更多的靈活性。

通用SMBus串行接口信息

SMBus串行接口為設備的配置和控制提供了便利。通過該接口,可以進行數據的讀寫操作。在寫入操作時,控制器需要依次發送起始位、寫地址、起始字節位置、字節計數等信息,并等待設備的確認;在讀取操作時,過程類似,但需要額外發送讀取地址等信息。此外,文檔還給出了SMBus地址選擇、各字節的功能定義等詳細信息,方便工程師進行編程和配置。

應用建議

在實際應用中,為了充分發揮該系列產品的性能,需要注意以下幾點:

- 電源設計:確保電源的穩定性和濾波效果,特別是對于模擬電源和數字電源,要分別進行合理的濾波處理,以減少電源噪聲對設備性能的影響。

- 布局布線:合理的布局布線可以減少信號干擾和延遲。例如,輸入和輸出信號應盡量分開布線,避免相互干擾;差分信號對要保持等長布線,以確保信號的對稱性。

- 散熱設計:根據產品的熱特性,設計合適的散熱方案。可以采用散熱片、風扇等散熱措施,確保設備在工作過程中不會因為過熱而影響性能。

- SMBus配置:根據實際需求,合理配置SMBus接口的各項參數,如輸出使能、PLL模式、輸出幅度等,以滿足不同應用場景的要求。

總結

9DBL02x2/9DBL04x2/9DBL06x1/9DBL08x1C系列PCIe零延遲/扇出緩沖器以其低功耗、高性能、靈活的配置和豐富的功能,為PCIe設計提供了一個優秀的解決方案。無論是在高速數據傳輸、時鐘同步還是系統穩定性方面,都具有出色的表現。希望通過本文的介紹,能幫助各位工程師更好地了解和應用這款產品,在實際設計中取得更好的效果。大家在使用過程中遇到任何問題,歡迎在評論區交流討論。

-

低功耗

+關注

關注

12文章

3638瀏覽量

106801 -

高性能

+關注

關注

0文章

609瀏覽量

21464

發布評論請先 登錄

9DBV05x1/9DBV07x1/9DBV09x1:PCIe Gen1 - 5出色的低功耗緩沖器

深入剖析PI7C9X2G304EL:PCI Express Gen 2 Packet Switch的卓越之選

9DBV05x1/9DBV07x1/9DBV09x1:PCIe Gen1 - 5的低功耗扇出緩沖器解決方案

PI7C9X130:PCI Express與PCI - X的高效橋梁

PI7C9X2G系列PCIe Packet Switch:高性能低功耗解決方案

深入解析PI7C9X113SL:PCIe到PCI/PCI - X的橋梁專家

探索PI7C9X2G312GP:高性能PCIe 2 3 - 端口/12 - 通道數據包交換機

9DBL0255/9DBL0455:PCIe Gen1 - 7時鐘扇出緩沖器的設計與應用

深度解析 LMK1C110x 時鐘緩沖器:高性能與低抖動的完美融合

德州儀器LMK1C110x時鐘緩沖器的特性與設計應用

揭秘LMK1D210x:高性能LVDS時鐘緩沖器的卓越之選

探索THVD14x9(V):高性能RS - 485收發器的卓越之選

探索THVD24x9:小型封裝RS - 485收發器的卓越之選

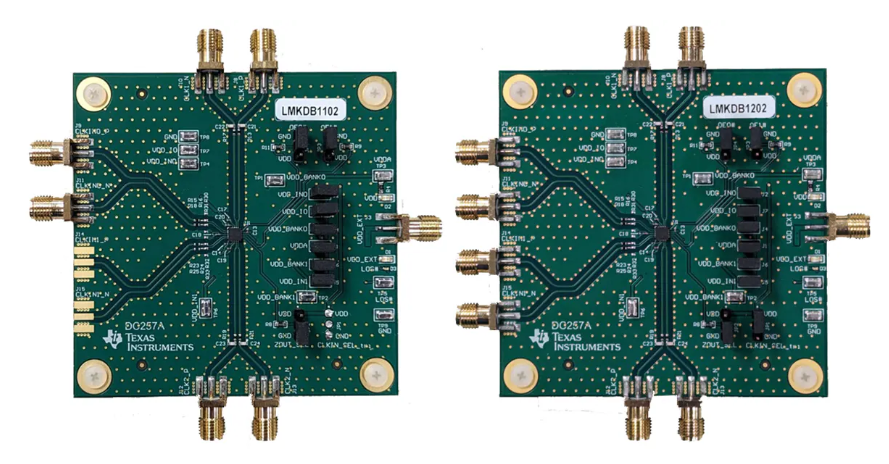

Texas Instruments LMKDB1x02EVM 評估模塊數據手冊

9DBL02x2/9DBL04x2/9DBL06x1/9DBL08x1C:PCIe零延遲/扇出緩沖器的卓越之選

9DBL02x2/9DBL04x2/9DBL06x1/9DBL08x1C:PCIe零延遲/扇出緩沖器的卓越之選

評論