1、時鐘設計,芯片性能的節拍器

在現代 IC 設計中,時鐘網絡的優化是實現高性能、高可靠性和低功耗的關鍵。本文聚焦四大核心技術:CTS 優化、DCD 最小化、時鐘門控和時鐘域交叉(CDC),帶你深入理解并掌握先進的時鐘設計策略。

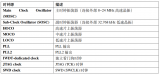

下圖展示了典型的時鐘樹結構(Clock Tree),用于平衡時鐘延遲與偏斜。

2、核心技術詳解

I. CTS 優化:消除時序違例的第一步

時鐘樹綜合(CTS) 是物理設計中構建平衡時鐘網絡的關鍵步驟,通過插入緩沖器和反相器,實現最小時鐘偏斜與延遲(skew + insertion delay)。例如,當啟用全局布線(global routing)而非虛擬路由預測時,可以顯著提升時序精度與一致性。

而“有用偏斜(useful skew)”技術則可通過人為調整時鐘到達路徑,緩解 setup/hold 違例。在實測中,通過 CTS 設置與命令(如 opt_useful_skew)的合理應用,有效優化了時序性能。

II. 降低 DCD:擁抱高密度設計的挑戰

占空比失真(DCD) 是高頻深布線設計中常見的問題,源于上升沿與下降沿的延遲差異,尤其在 7nm 節點后更加明顯。

解決之道之一是采用 Infinisim 的 ClockEdge 工具,其通過 SPICE 級別仿真,覆蓋百萬門電路網絡,實現高精度寄生分析和 DCD 檢測,挖掘傳統 STA 無法發現的潛在問題,提升簽核信心。

III. 時鐘門控:動態關斷,擁抱低功耗

時鐘門控(Clock Gating) 是數字設計中最廣泛采用的動態功耗優化技術之一,通過停止時鐘信號傳導至空閑模塊,顯著降低切換功耗。

其中 順序時鐘門控(Sequential Clock Gating) 在多個時鐘周期基礎上進行區域判斷,相較于組合門控更為精確,可節省高達 30% 時鐘功耗。但手工設計復雜,容易出錯—工具如 Calypto PowerPro 可自動推斷并驗證時序邏輯,保障設計高效可靠。

IV. CDC 驗證:多域交叉的安全機制

在多時鐘域 SoC 中,信號跨域需防止亞穩態、毛刺和數據一致性問題。分層時鐘域交叉(Hierarchical CDC) 驗證方法,如底向上與頂向下混合策略,可及早識別異步邊界問題。

Motellus 的 Maestro 技術進一步優化了多速率通信路徑,減少 CDC Fifo 使用與重定時 flops,提高 PPA 效率與設計健壯性。

3、為什么選擇 EDA Academy 深入學習?

?課程前沿全面:無論是 CTS 調優、DCD 分析、時鐘門控策略,還是 CDC 驗證流程,EDA Academy(www.eda-academy.com) 都提供最新、實戰驅動的系統課程,讓你完整掌握時鐘設計要點。

?靈活身份切換:你既可以作為學員深造,也可注冊導師,分享經驗提升自我。

?免費 Newsletter 訂閱:只需郵箱注冊,即可定期獲得時序設計新技術、工具評測和實戰案例。

?銷售聯盟回報機制:加入推廣課程的銷售聯盟,推薦即有 20%–50% 傭金,讓你學有所值還能收獲收益。

通過優化 CTS、消減 DCD、應用高效時鐘門控、以及強化 CDC 驗證,設計師能夠顯著提升 IC 時序性能、節省動態功耗、提升設計魯棒性。而 EDA Academy 則是你深化這一核心領域、擴展能力與職業價值的最佳平臺。歡迎訪問www.eda-academy.com,開啟你的時鐘設計實戰成長之旅!

審核編輯 黃宇

-

芯片

+關注

關注

463文章

54007瀏覽量

465911 -

eda

+關注

關注

72文章

3113瀏覽量

182863 -

CDC

+關注

關注

0文章

58瀏覽量

18569 -

時鐘設計

+關注

關注

0文章

29瀏覽量

11186

發布評論請先 登錄

Linux進程樹分析工具pstree詳解與實戰指南(另一視角優化Linux系統)

【深圳】嵌入式AI實戰:半天上手,人形檢測模型部署+優化全流程

MCU時鐘管理對功耗優化方向

淘寶拍立淘接口實戰:圖像優化、識別調優與避坑代碼示例

別踩分頁坑!京東商品詳情接口實戰指南:從并發優化到數據完整性閉環

淘寶商品詳情 API 實戰:5 大策略提升店鋪轉化率(附簽名優化代碼 + 避坑指南)

數據庫慢查詢分析與SQL優化實戰技巧

瑞薩RA系列FSP庫開發實戰指南(29)CGC(時鐘生成電路)時鐘控制

時鐘設計優化實戰

時鐘設計優化實戰

評論