集成電路工藝(integrated circuit technique )是把電路所需要的晶體管、二極管、電阻器和電容器等元件用一定工藝方式制作在一小塊硅片、玻璃或陶瓷襯底上,再用適當的工藝進行互連,然后封裝在一個管殼內,使整個電路的體積大大縮小,引出線和焊接點的數目也大為減少。集成的設想出現在50年代末和60年代初,是采用硅平面技術和薄膜與厚膜技術來實現的。電子集成技術按工藝方法分為以硅平面工藝為基礎的單片集成電路、以薄膜技術為基礎的薄膜集成電路和以絲網印刷技術為基礎的厚膜集成電路。

單片集成電路工藝

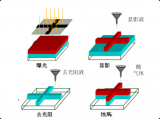

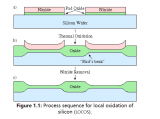

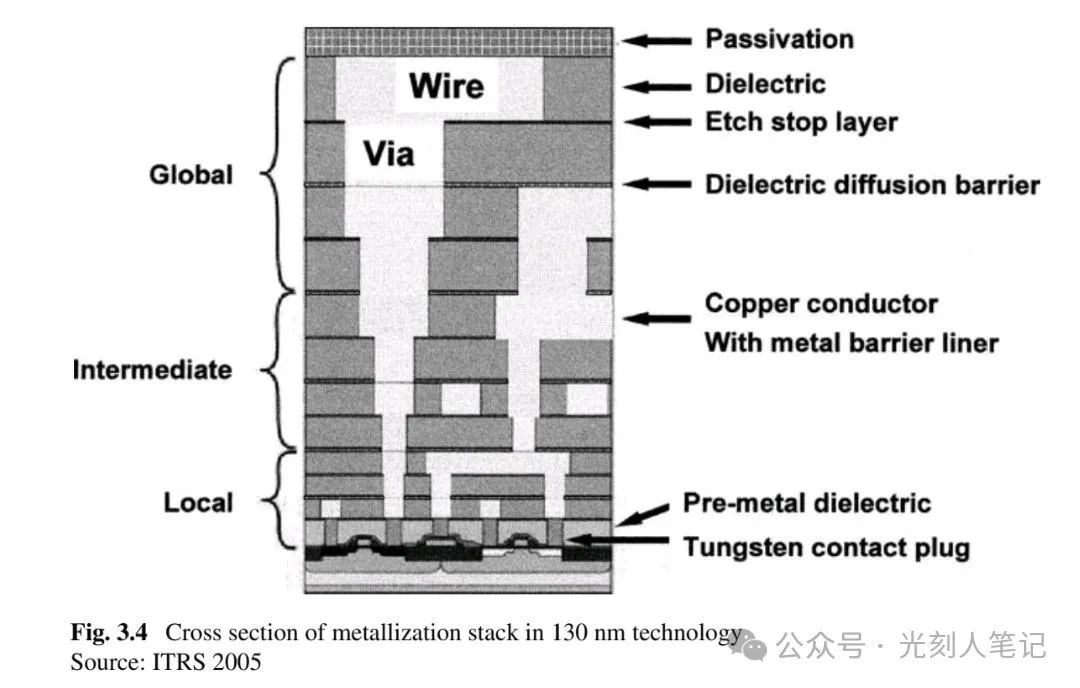

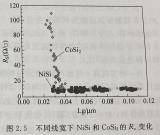

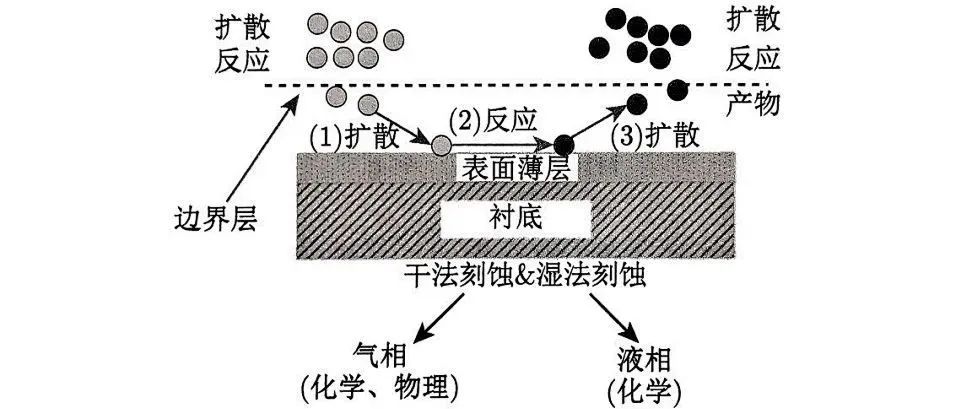

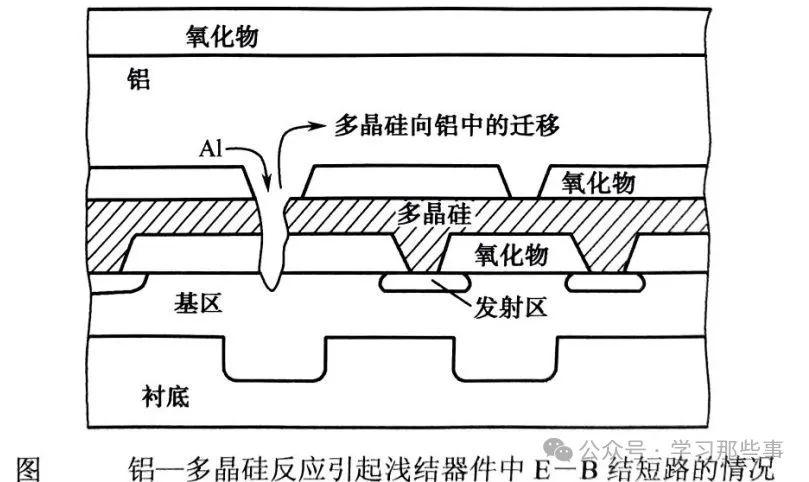

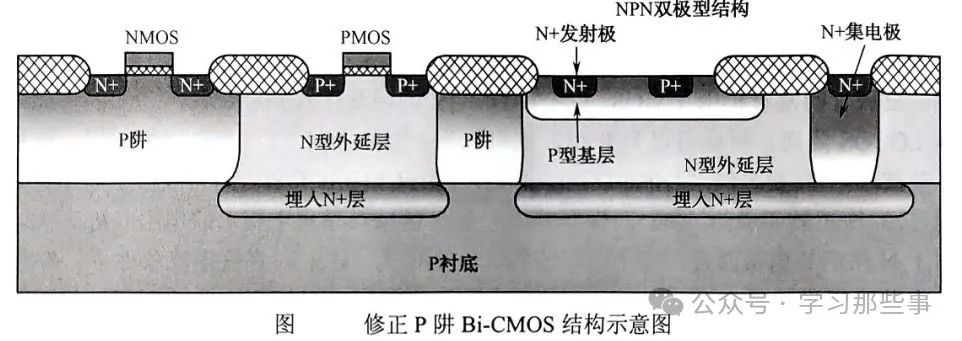

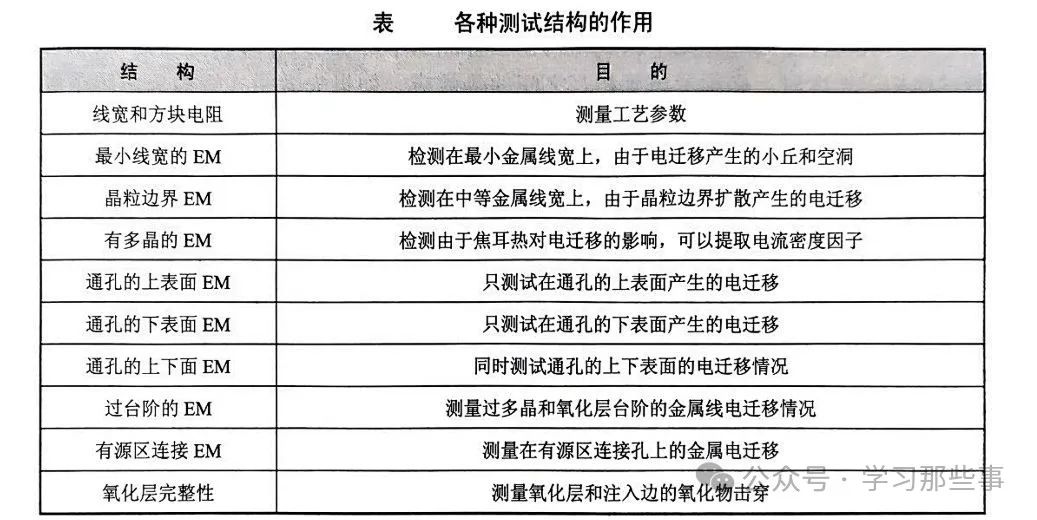

利用研磨、拋光、氧化、擴散、光刻、外延生長、蒸發等一整套平面工藝技術,在一小塊硅單晶片上同時制造晶體管、二極管、電阻和電容等元件,并且采用一定的隔離技術使各元件在電性能上互相隔離。然后在硅片表面蒸發鋁層并用光刻技術刻蝕成互連圖形,使元件按需要互連成完整電路,制成半導體單片集成電路。隨著單片集成電路從小、中規模發展到大規模、超大規模集成電路,平面工藝技術也隨之得到發展。例如,擴散摻雜改用離子注入摻雜工藝;紫外光常規光刻發展到一整套微細加工技術,如采用電子束曝光制版、等離子刻蝕、反應離子銑等;外延生長又采用超高真空分子束外延技術;采用化學汽相淀積工藝制造多晶硅、二氧化硅和表面鈍化薄膜;互連細線除采用鋁或金以外,還采用了化學汽相淀積重摻雜多晶硅薄膜和貴金屬硅化物薄膜,以及多層互連結構等工藝。

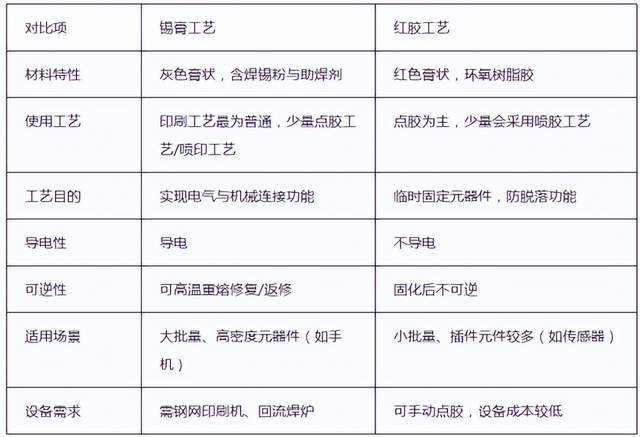

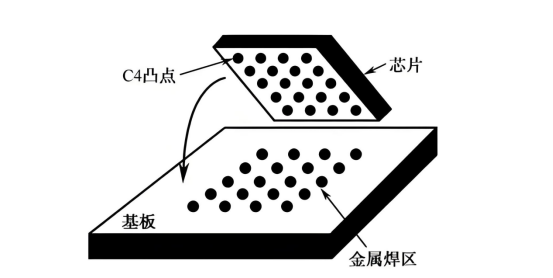

而厚膜混合集成電路工藝是用絲網印刷和燒結等厚膜工藝在同一基片上制作無源網絡,并在其上組裝分立的半導體器件芯片或單片集成電路或微型元件,再外加封裝而成的混合集成電路。厚膜混合集成電路是一種微型電子功能部件。青島智騰微電子生產的厚膜混合集成電路封裝具有六大優勢,基片選用陶瓷基板,散熱好,應用環境溫度可達:-55℃~250℃;模塊內部采用裸芯片貼裝,組裝密度高達10~100個/cm2,產品體積比傳統PCB電路縮小30%~70%;內部采用高純氮氣氣密性封裝,裸芯片的焊接使用邦定工藝,不易產生虛焊、脫焊,比PCB電路焊點減少70%~90%;內部元器件使用金絲連接,走線短,寄生效應小、噪聲小、功耗低、溫度漂移小;鍍金或陶瓷外殼封,裝模塊化設計、組裝,耐腐蝕,且便于儀器設備故障檢查和維修;多芯片裸芯封裝,形成功能完整的應用SOC模塊,仿制難度大,保密性好。

電子發燒友App

電子發燒友App

評論