文章來源:Jeff的芯片世界

原文作者:Jeff的芯片世界

Bosch工藝,又稱交替側壁鈍化深層硅蝕刻工藝,是一種在半導體制造中用于刻蝕硅片上特定材料層的先進技術,由Robert Bosch于1993年提出,屬于等離子體增強化學刻蝕(反應離子刻蝕)的一種。該工藝通過獨特的“刻蝕-鈍化”循環,實現了高深寬比、各向異性的微結構加工,廣泛應用于微機電系統(MEMS)、深硅刻蝕及硅通孔(TSV)制造等領域。

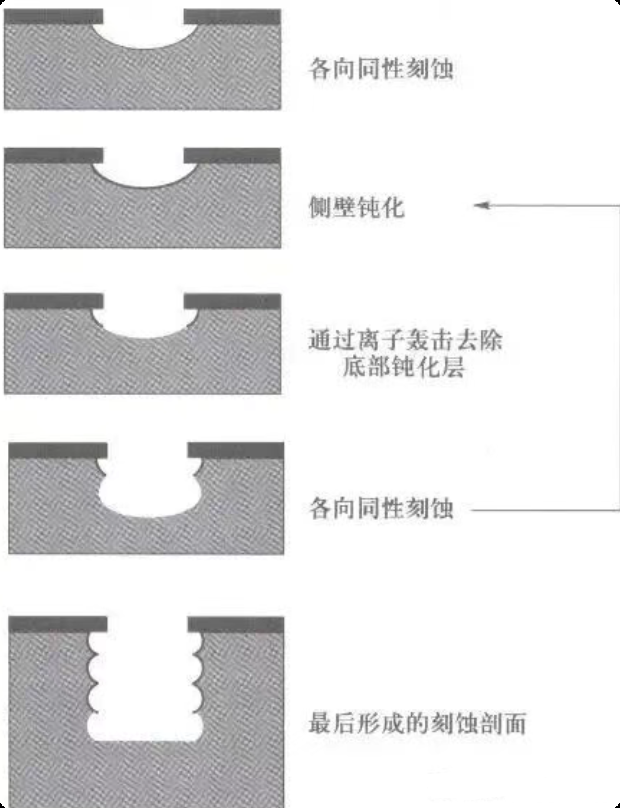

其核心原理基于周期性交替進行的三個子過程:首先進行基礎刻蝕,使用SF6氣體產生氟離子對硅進行各向異性刻蝕,形成初始溝槽或孔洞;隨后進入側壁保護階段,通入C4F8氣體,在等離子體作用下于側壁沉積一層聚合物保護膜;最后進行側壁刻蝕,再次切換回SF6刻蝕環境,去除溝槽底部的硅材料而保護側壁。這三個階段構成一個完整循環,通過多次重復,逐步加深結構直至達到所需深度。

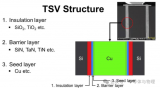

在TSV與先進封裝中的關鍵作用

在高性能計算、人工智能等領域廣泛應用的HBM(高帶寬內存)等3D堆疊技術中,硅通孔(TSV)是實現芯片垂直電氣連接的關鍵。TSV技術要求在硅基板上刻蝕出深且直的高深寬比孔洞。Bosch工藝憑借其高深寬比、高精度和各向異性刻蝕能力,成為制造TSV結構的理想選擇,對于HBM和TSV的制造起到了至關重要的作用。

具體而言,在TSV工藝流程的“孔形成”步驟中,普遍采用基于Bosch工藝的深反應離子刻蝕(DRIE)。該工藝能夠刻蝕出深度達幾十至幾百微米、尺寸為幾微米到幾十微米的高深寬比通孔,確保了垂直互連的可靠性和性能。TSV技術通過這種垂直連接,大幅縮短了互連長度,降低了信號延遲和功耗,提高了數據傳輸速率,是實現3D IC封裝和異構集成的核心技術。

工藝特點與優勢

Bosch工藝具備多項顯著特點與優勢。首先是高深寬比,能夠實現幾十至幾百微米的深寬比,滿足深槽、深孔結構的制造需求。其次是優異的各向異性,即垂直刻蝕能力,能有效抑制側向刻蝕,形成近乎垂直的刻蝕剖面,這對器件小型化和高密度集成至關重要。第三是高選擇性,通過調節工藝參數,可以實現對硅、二氧化硅、氮化硅等不同材料的選擇性刻蝕。最后是良好的工藝可控性,通過精確控制脈沖頻率、氣體流量、功率等參數,能夠精細調整刻蝕速率、剖面形貌和均勻性,適應復雜的制造要求。

具體工藝流程步驟

一次完整的Bosch工藝通常包含以下步驟:首先是預清洗和腔室準備,確保硅片表面清潔并設定好工藝氣體環境。接著進入等離子體生成與刻蝕階段,啟動射頻電源產生等離子體,活性粒子與硅反應進行刻蝕。然后切換至鈍化階段,通入鈍化氣體(如C4F8)在側壁形成保護膜。之后,重復進行“刻蝕-鈍化”循環,逐步加深結構。當達到預定刻蝕深度后,終止刻蝕并進行后處理清洗,去除殘留副產物。

該工藝的循環方式本質上是“刻蝕→形成側壁保護層→重復交替”,通過這種周期性操作實現深度方向的“階梯狀”深刻蝕,同時保護側壁形態。

應用領域與未來發展

Bosch工藝的應用已擴展到半導體制造的多個關鍵領域。在MEMS器件制造中,用于加工壓力傳感器、加速度計等所需的復雜三維微結構。在存儲器制造中,用于刻蝕DRAM電容器的深電極孔和3D NAND Flash的深溝槽通道。在功率半導體中,用于制造改善器件性能的深溝槽結構。此外,還應用于光電子器件的微光學結構加工以及深溝槽隔離等。

隨著技術發展,Bosch工藝也在不斷演進以應對新挑戰,如優化工藝參數以減少側壁“扇貝效應”(波紋),以及將工藝拓展至碳化硅(SiC)等更難刻蝕的寬禁帶半導體材料。未來,該工藝將繼續推動3D集成、先進封裝和異構集成技術的發展,滿足后摩爾時代對更高性能、更小尺寸和更優架構的追求。

Bosch工藝作為一種精密的深硅刻蝕技術,通過其創新的循環刻蝕與鈍化機制,為現代半導體產業,特別是3D集成與先進封裝,提供了制造高深寬比、高精度微結構的關鍵解決方案,其持續創新將對未來電子器件的發展產生深遠影響。

-

集成電路

+關注

關注

5455文章

12599瀏覽量

374919 -

半導體

+關注

關注

339文章

30870瀏覽量

265008 -

BOSCH

+關注

關注

14文章

65瀏覽量

55462

原文標題:Bosch工藝技術介紹

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

集成電路基本的工藝流程步驟

國產EDA“夾縫”生存 集成電路設計和制造流程

集成電路制造中Bosch工藝的關鍵作用和流程步驟

集成電路制造中Bosch工藝的關鍵作用和流程步驟

評論