硅與其他半導(dǎo)體材料在集成電路應(yīng)用中的比較可從以下維度展開(kāi)分析:

一、基礎(chǔ)特性對(duì)比

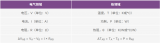

| 材料 | 帶隙(eV) | 電子遷移率(cm2/(V·s)) | 熱導(dǎo)率(W/(m·K)) | 擊穿電場(chǎng)(MV/cm) |

|---|---|---|---|---|

| ?硅(Si)? | 1.12 | 1500 | 150 | 0.3 |

| 鍺(Ge) | 0.67 | 3900 | 60 | 0.1 |

| 砷化鎵(GaAs) | 1.42 | 8500 | 55 | 0.4 |

| 碳化硅(SiC) | 3.26 | 900 | 490 | 3.0 |

| 氮化鎵(GaN) | 3.4 | 2000 | 130 | 3.3 |

二、核心優(yōu)勢(shì)領(lǐng)域

?硅材料?

?主流邏輯芯片?:全球95%的集成電路采用硅基制造,因其成本低(12英寸晶圓成本僅為砷化鎵的1/10)、工藝成熟(支持3nm制程)14

?集成度優(yōu)勢(shì)?:硅晶圓直徑可達(dá)300mm,單晶缺陷率低于0.1/cm2,適合超大規(guī)模集成814

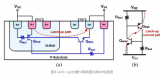

?氧化層特性?:自然生成的SiO?絕緣層(介電常數(shù)3.9)是MOSFET器件的理想介質(zhì)28

?化合物半導(dǎo)體?

?高頻應(yīng)用?:砷化鎵電子遷移率是硅的5.7倍,適用于5G毫米波(>30GHz)器件49

?功率器件?:碳化硅擊穿電場(chǎng)強(qiáng)度達(dá)硅的10倍,可使電動(dòng)汽車(chē)逆變器損耗降低70%112

?光電轉(zhuǎn)換?:磷化銦(InP)在光通信波段(1310/1550nm)量子效率超90%4

三、關(guān)鍵性能短板

?硅的局限性?

禁帶寬度窄導(dǎo)致高溫漏電流大(>150℃性能驟降)911

高頻特性差(截止頻率<100GHz),不適合太赫茲應(yīng)用411

?替代材料挑戰(zhàn)?

?成本問(wèn)題?:6英寸碳化硅晶圓價(jià)格是硅晶圓的20倍12

?晶圓尺寸?:氮化鎵量產(chǎn)晶圓最大直徑僅8英寸,限制產(chǎn)能提升12

?工藝兼容性?:砷化鎵器件需特殊生產(chǎn)線,與硅基產(chǎn)線不通用4

四、技術(shù)演進(jìn)趨勢(shì)

?混合集成?:硅基CMOS與氮化鎵射頻器件3D堆疊(如蘋(píng)果5G射頻模組)12

?異質(zhì)外延?:在硅襯底上生長(zhǎng)GaN薄膜以降低成本(已實(shí)現(xiàn)200mm工藝)12

?量子計(jì)算?:硅-28同位素自旋量子比特相干時(shí)間突破1秒11

當(dāng)前硅仍主導(dǎo)邏輯芯片市場(chǎng),而第三代半導(dǎo)體在功率/射頻領(lǐng)域加速滲透,形成互補(bǔ)共存格局48。

-

集成電路

+關(guān)注

關(guān)注

5459文章

12614瀏覽量

375178 -

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

30989瀏覽量

265451

發(fā)布評(píng)論請(qǐng)先 登錄

臺(tái)階儀在集成電路制造中的應(yīng)用:高端光刻膠材料純化研究進(jìn)展

集成電路制造中薄膜生長(zhǎng)設(shè)備的類型和作用

半導(dǎo)體中的合金制備技術(shù)詳解

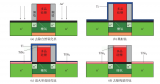

CMOS集成電路中閂鎖效應(yīng)的產(chǎn)生與防護(hù)

集成電路制造中薄膜刻蝕的概念和工藝流程

功率集成電路應(yīng)用中的通用熱學(xué)概念

PDK在集成電路領(lǐng)域的定義、組成和作用

恒坤新材IPO擬募資10.07億,錨定集成電路關(guān)鍵材料國(guó)產(chǎn)化突破

恒坤新材IPO成功過(guò)會(huì),劍指集成電路關(guān)鍵材料國(guó)產(chǎn)化

集成電路傳統(tǒng)封裝技術(shù)的材料與工藝

量水堰計(jì)如何與其他監(jiān)測(cè)系統(tǒng)集成?

硅與其他材料在集成電路中的比較

硅與其他材料在集成電路中的比較

評(píng)論