半導體外延工藝主要在集成電路制造的前端工藝(FEOL)階段進行。以下是具體說明:

所屬環節定位:作為核心步驟之一,外延屬于前端制造流程中的關鍵環節,其目的是在單晶襯底上有序沉積單晶材料以形成外延層。這一過程為后續晶體管、二極管等器件的構建提供基礎結構。

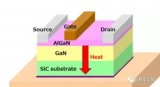

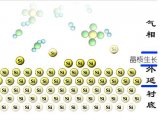

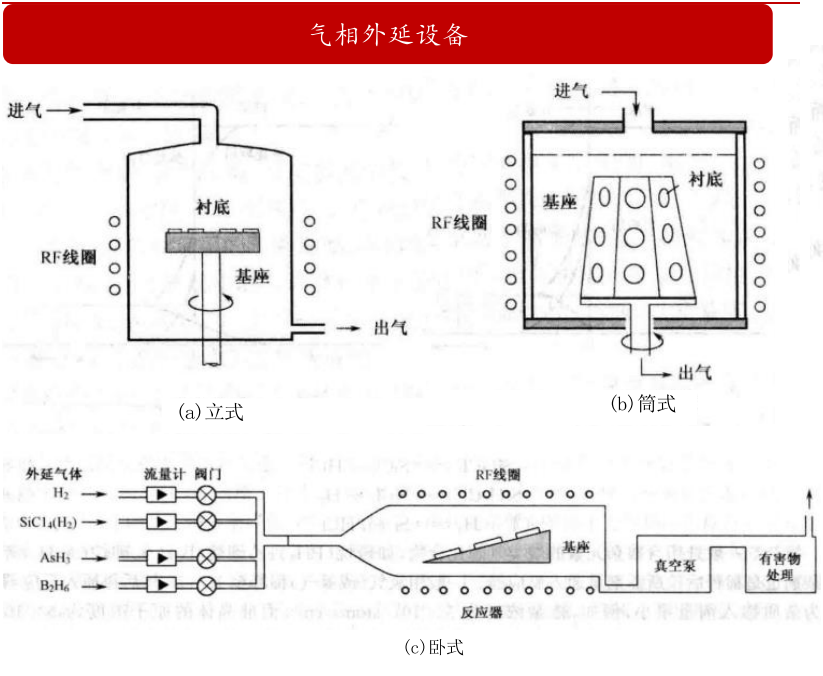

工藝目標與作用:通過同質外延(如Si/Si)或異質外延(如SiGe/Si),結合分子束外延(MBE)、氣相外延(VPE)和金屬有機化學氣相沉積(MOCVD)等技術,實現對材料厚度、電阻率及晶格匹配性的精確控制。例如,在CMOS源漏區的SiGe外延或HBT基區制備中,外延層直接影響器件性能。

與其他工序的關系:該工藝通常先于光刻、刻蝕等后端步驟完成,確保襯底表面的晶體質量和導電特性符合設計要求。外延層的晶體完整性、位錯密度等參數會顯著影響最終器件的可靠性和效率。

特殊應用場景擴展:除常規應用外,選擇性外延生長技術還可用于納米線制造、鰭式場效應晶體管(FinFET)優化等領域,通過掩模限定材料沉積區域,實現局部高精度生長。

半導體外延工藝是前端制造的核心基礎,通過精準的材料堆疊和晶體控制,為高性能器件提供關鍵的物理支撐結構。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

集成電路

+關注

關注

5461文章

12636瀏覽量

375378 -

半導體

+關注

關注

339文章

31077瀏覽量

265764 -

外延芯片

+關注

關注

0文章

4瀏覽量

6056

發布評論請先 登錄

相關推薦

熱點推薦

半導體制造之外延工藝詳解

外延工藝是指在襯底上生長完全排列有序的單晶體層的工藝。一般來講,外延工藝是在單晶襯底上生長一層與原襯底相同晶格取向的晶體層。

半導體工藝講座

半導體工藝講座ObjectiveAfter taking this course, you will able to? Use common semiconductor terminology

發表于 11-18 11:31

招聘半導體封裝工程師

能力強;善于與人進行溝通、交流。 5、有相關半導體封裝工作經驗的優先。海特光電有限責任公司專著于半導體激光器器件和應用產品研發、生產和銷售,作為國內半導體激光器市場最早的開拓者,擁有從

發表于 02-10 13:33

中電化合物榮獲“中國第三代半導體外延十強企業”

近日,華大半導體旗下中電化合物有限公司榮獲“中國第三代半導體外延十強企業”稱號,其生產的8英寸SiC外延片更是一舉斬獲“2023年度SiC襯底/外延最具影響力產品獎”。這一榮譽充分體現

半導體襯底和外延有什么區別?

襯底(substrate)是由半導體單晶材料制造而成的晶圓片,襯底可以直接進入晶圓制造環節生產半導體器件,也可以進行外延工藝加工生產

發表于 03-08 11:07

?3908次閱讀

用于半導體外延片生長的CVD石墨托盤結構

襯底的關鍵組件,其結構和性能對外延片的質量具有決定性影響。本文將詳細介紹一種用于半導體外延片生長的CVD石墨托盤結構,探討其設計特點、工作原理及在半導體制造中的應

半導體外延和薄膜沉積有什么不同

半導體外延和薄膜沉積是兩種密切相關但又有顯著區別的技術。以下是它們的主要差異:定義與目標半導體外延核心特征:在單晶襯底上生長一層具有相同或相似晶格結構的單晶薄膜(外延層),強調晶體結構的連續性和匹配

半導體外延工藝在哪個階段進行的

半導體外延工藝在哪個階段進行的

評論