此選項根據你所用的FPGA型號確定GT類型,我所用的是7k325t系列,故GT類型為GTX。

當使用不同版本的Vivado打開工程時,IP核被鎖定的情況較為常見。不同版本的Vivado對IP核的....

本章以太網通信實驗是基于ZYNQ-MZ702P開發板進行實現,在配置方面,需要讀者自主修改不同的地方....

在Vivado的時序約束中,-invert是用于控制信號極性的特殊參數,應用于時鐘約束(Clock ....

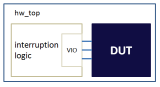

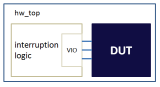

在 HDL 代碼中標記待觀測信號,添加 (* mark_debug = "true" *) 屬性(V....

高層次綜合(HLS)是一種將高級編程語言(如C、C++或SystemC)轉換為硬件描述語言(HDL)....

FFT 的輸出不是 “連續的頻率譜”,而是離散的、等寬的頻率區間,每個區間就稱為一個 “頻率倉”(簡....

Vivado HLS是一款強大的高層次綜合工具,可將C/C++代碼轉換為硬件描述語言(HDL),顯著....

ZYNQ 的程序固化是指將程序代碼永久存儲到非易失性存儲器中,使系統上電后能自動加載運行的過程。主要....

在vivado中,我們常用的時序約束指令主要包括如下幾個方面。

其中1是添加幾個觀察信號,2是采樣深度。1根據自己要觀察的信號進行選擇,2一般越大越好。

為滿足對 “納秒級實時響應” 與 “復雜數據深度運算” 的雙重需求,“FPGA+GPU”異構混合部署....

FPGA 芯片中DSP(數字信號處理)硬核是高性能計算的核心資源,但使用不當會引入隱蔽性極強的“坑”....

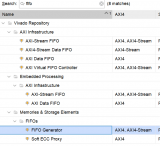

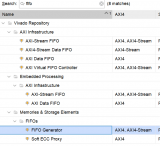

FIRST IN FIRST OUT (先入先出)。顧名思義,FIFO是一個數據具有先進先出的存儲器....

Serial RapidIO(SRIO) 特指 RapidIO 標準的串行物理層實現。

在數字IC/FPGA設計的過程中,對PPA的優化是無處不在的,也是芯片設計工程師的使命所在。此節主要....

FPGA定點數計算在高效資源利用、運算速度優勢、硬件可預測性和成本效益等方面發揮著重要作用。它能節省....

microblaze和jtag-to-axi(jtag2axi)雖然也提供了訪問axi總線的能力,但....

本篇博客具體包括SPI協議的基本原理、模式選擇以及時序邏輯要求,采用FPGA(EPCE4),通過SP....

添加Zynq Processing System IP核,配置DDR控制器和時鐘。7000系列的Zy....

本章的實驗任務是在 PL 端自定義一個 AXI4 接口的 IP 核,通過 AXI_HP 接口對 PS....

IBERT(Integrated Bit Error Ratio Tester),集成誤碼率測試儀。....

調頻連續波(frequency modulated continuous wave, FMCW),常....

Xilinx FPGA因其高性能和低延遲,常用于串行通信接口設計。本文深入分析了Aurora、PCI....

本例程詳細介紹了如何在FPGA上實現Serial RapidIO(SRIO)通信協議,并通過Veri....

本文介紹了一個基于FPGA的內存到串行數據傳輸模塊,該模塊設計用來高效地處理存儲器中的數據并傳輸至串....

如果對處于全速(at-speed)運行下的FPGA調試,工程師在現有通用“能力技術”基礎上,再增加“....

本篇將詳細介紹如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試。SRAM是一種非易失....

本質上就是對數據進行多級寄存器緩存,延遲時間以clk的一個周期為單位,消耗的就是寄存器。比較適合延遲....

這列出了定義板上可用的不同JTAG鏈。每個鏈都列在下面<jtag_chain>以及鏈的名稱,以及定義名稱和鏈中組件的位置。