一、前言

IBERT(Integrated Bit Error Ratio Tester),集成誤碼率測(cè)試儀。作為用戶來(lái)說(shuō)可以使用這個(gè)工具對(duì)自己設(shè)計(jì)的板子中的高速串行收發(fā)器進(jìn)行簡(jiǎn)單測(cè)試,從而判斷設(shè)計(jì)的接口是否有問(wèn)題。因?yàn)檫@個(gè)工具是直接集成到FPGA上,這樣一來(lái)直接使用這個(gè)工具來(lái)測(cè)試高速接口就方便很多了,它只需要JTAG和測(cè)試接口用的連接線就能完成對(duì)板子的測(cè)試。

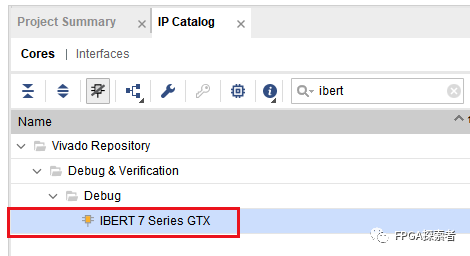

二、IBERT配置

使用ibrt時(shí)主要時(shí)例化時(shí)對(duì)各個(gè)參數(shù)進(jìn)行配置,本節(jié)將順應(yīng)IP的配置順序?qū)Ω鱾€(gè)配置參數(shù)進(jìn)行介紹。在對(duì)4個(gè)配置頁(yè)面進(jìn)行介紹之前,先對(duì)component name進(jìn)行說(shuō)明,這個(gè)就是ip的定義名字,可以有字母數(shù)字下劃線組合而成,下劃線不能再最前面。

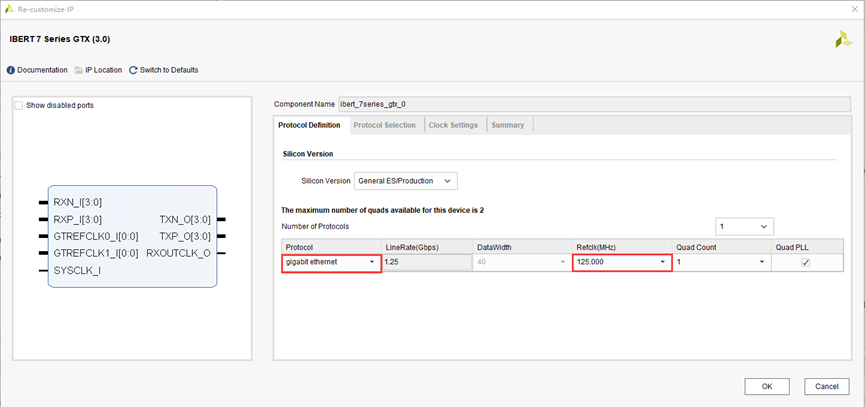

2.1 協(xié)議定義

協(xié)議是線速/數(shù)據(jù)寬度/參考時(shí)鐘速率的組合。一個(gè) IBERT 內(nèi)核最多可以定義三個(gè)協(xié)議,并且可以將任意數(shù)量的可用 Quad 指定為定義的任何協(xié)議。

Silicon Version:選擇“常規(guī) ES/產(chǎn)品”或“初始 ES”按鈕以匹配目標(biāo)芯片,這兩者的區(qū)別暫時(shí)還沒(méi)弄清楚,一般來(lái)說(shuō)使用過(guò)程中默認(rèn)選第一個(gè)。

Number of Protocols:選擇協(xié)議的數(shù)量, 一個(gè)IBERT 最多可定義三個(gè)協(xié)議。

Protocol:在Protocol框中,選擇自定義(custom)或其他預(yù)定義協(xié)議。如果為自定義,需要在linerate框中輸入線速率(如果超出允許的范圍,則線速率以紅色文本顯示)。

LianRate(Gbps):線速率,單位為吉比特每秒。可以根據(jù)要求選擇自定義值,也可以從預(yù)先提供的行業(yè)標(biāo)準(zhǔn)協(xié)議(例如,CPRI、千兆以太網(wǎng)或 XAUI)中進(jìn)行選擇。

DataWith:選擇數(shù)據(jù)的位寬。

refclk(Mhz):參考時(shí)鐘頻率,單位為兆赫茲。GT收發(fā)器的參考時(shí)鐘。

Quad Count:再參考時(shí)鐘頻率下運(yùn)行的Quad數(shù)量。一個(gè)Quad對(duì)應(yīng)四個(gè)channel。

Quad PLL:Quad的時(shí)鐘單元,默認(rèn)情況下,Quad PLL 處于選中狀態(tài)。要改為選擇 CPLL,可以取消選中 QPLL 復(fù)選框。Xilinx建議在高于 6.5 Gb/s 的線速率下使用 QPLL,可以為 0.6 Gb/s 至 6.5 Gb/s 范圍內(nèi)的每個(gè)線速選擇 QPLL或者CPLL。

2.2 協(xié)議選擇

GTH location:將顯示器件/封裝組合中可用的Quad。

Protocol Selected:將要測(cè)的Quad分配給特定協(xié)議。

Refclk Selection:參考時(shí)鐘輸入的合法選擇列在 REFCLK 選擇組合中,這里需要結(jié)合原理圖確定是選擇MGTREFCLK0還是MGTREFCLK1,以及是否選擇相鄰的南北兩個(gè)Quad的參考時(shí)鐘作為本Quad的參考時(shí)鐘。

TXUSRCLK Source:將 Quad 分配給協(xié)議后,將啟用 TXUSRCLK 驅(qū)動(dòng)源組合會(huì)被使能。TXUSRCLK 在 Quad 中的所有四個(gè)通道之間共享,因此需要確認(rèn)組合中 TXOUTCLK 中的哪一個(gè)通道應(yīng)用于用戶時(shí)鐘。

2.3 Clock Settings

Add RXOUTCLK Probes:如果需要,接收器時(shí)鐘探頭使能功能可從任何串行收發(fā)器中提取恢復(fù)的時(shí)鐘。啟用后,會(huì)出現(xiàn)一個(gè)新面板,可以在其中填寫串行收發(fā)器源和探針標(biāo)準(zhǔn)。在“時(shí)鐘設(shè)置”選項(xiàng)卡中,單擊“添加RXOUTCLK探頭”,Quad lane0 驅(qū)動(dòng)輸出引腳或引腳對(duì)。需要從列表中選擇 I/O 標(biāo)準(zhǔn)并分配有效的引腳位置。

Systom clock:IBERT內(nèi)核需要一個(gè)自由運(yùn)行的系統(tǒng)時(shí)鐘,用于通信和內(nèi)核中包含的其他邏輯。選擇 I/O 標(biāo)準(zhǔn)、有效引腳位置和頻率以完成系統(tǒng)時(shí)鐘設(shè)置。或者,也可以選擇任何啟用的Quad參考時(shí)鐘。為了使內(nèi)核正常工作,當(dāng)FPGA配置為IBERT內(nèi)核設(shè)計(jì)時(shí),該系統(tǒng)時(shí)鐘源必須保持工作和穩(wěn)定。如果系統(tǒng)時(shí)鐘的運(yùn)行速度超過(guò)150 MHz,則會(huì)使用混合模式時(shí)鐘管理器(MMCM)在內(nèi)部對(duì)其進(jìn)行分頻,以滿足時(shí)序限制。xilinx推薦選擇外部時(shí)鐘源來(lái)驅(qū)動(dòng)系統(tǒng)時(shí)鐘 。

注:在我自己的使用過(guò)程中選擇了一個(gè)Quad的參考時(shí)鐘作為系統(tǒng),結(jié)果在vivado hardware 下始終不會(huì)出現(xiàn)IBERT,導(dǎo)致無(wú)法觀測(cè)誤碼率,最終選擇板上晶振作為IBERT時(shí)鐘IBERT才被探測(cè)到,而后發(fā)現(xiàn)最初為其選擇參考時(shí)鐘為系統(tǒng)的哪個(gè)Quad則是無(wú)法link上。因此如Xilinx的推薦一樣,最好選擇外部時(shí)鐘源來(lái)驅(qū)動(dòng)IBERT的系統(tǒng)時(shí)鐘。

2.4 Summary

回顧總結(jié)之前配置的內(nèi)容。

三、IBRT使用

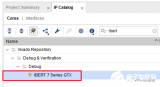

在完成好IP的設(shè)置之后,可以在工程下看到綜合好的IP模塊,單擊右鍵點(diǎn)擊open IP example design即可獲得基于該IP生成的示例工程。直接生成比特然后下載到板子上即可。

工程下載完成后,在vivado hardware manager中便會(huì)顯示IBRT的內(nèi)容,下下方也會(huì)出現(xiàn)serial I/O Links以及serial I/O Scans頁(yè)面,在IBERT上右鍵創(chuàng)建Links或者直接在serial I/O Links點(diǎn)擊+號(hào)添加links。

3.1 serial I/O Links

在serial I/O Links頁(yè)面中可以看見(jiàn)詳細(xì)的鏈路信息。

Status:鏈路傳輸速率,如果為建鏈成功會(huì)顯示No Link,建鏈不成功多半時(shí)時(shí)鐘不對(duì),以及PCB的問(wèn)題。.當(dāng)檢查器連續(xù)五個(gè)周期接收到?jīng)]有錯(cuò)誤的數(shù)據(jù)時(shí),就會(huì)斷言LINK信號(hào)(顯示線速率)。如果 LINK 信號(hào)被置位,并且檢查器連續(xù)收到五個(gè)帶有數(shù)據(jù)錯(cuò)誤的周期,則 LINK 信號(hào)將被取消置位(顯示No Link)。

Bits:探測(cè)到的比特?cái)?shù)量。

Error:錯(cuò)誤的比特?cái)?shù)量。

BER:誤碼率,bit error ratio。

Reset:如果更改了serial I/O Links中的某些配置,需要reset下一重新進(jìn)行檢測(cè)。

TX/RX Pattern:測(cè)試時(shí)的偽隨機(jī)碼(PRBS),接收端需要校驗(yàn)發(fā)送端發(fā)送的數(shù)據(jù)是否正確的來(lái)計(jì)算誤碼率,故需要Tx和Rx的偽隨機(jī)碼一致。

TX Pre-Cursor:TX 預(yù)加重,用于改善信號(hào)傳輸質(zhì)量的參數(shù),可以修改參數(shù)獲取最優(yōu)質(zhì)量鏈路。

TX Post-Cursor:TX后加重,用于改善信號(hào)傳輸質(zhì)量的參數(shù),可以修改參數(shù)獲取最優(yōu)質(zhì)量鏈路。

TX Diff Swing:用于改善信號(hào)傳輸質(zhì)量的參數(shù),可以修改參數(shù)獲取最優(yōu)質(zhì)量鏈路。

DFE Enabled:收發(fā)器的Rx接收端的均衡器的使能信號(hào),勾選有利補(bǔ)償信號(hào)在信道傳輸中的損失。

Inject Error:可以在測(cè)試過(guò)程中注入錯(cuò)誤,可以模擬真實(shí)情況下有可能遇到的各種影響。

TX/RX Reset:發(fā)送端和接收端各自單獨(dú)的復(fù)位。

RX/TX PLL Status:顯示locked即表示可以進(jìn)行測(cè)試,如果顯示其他則說(shuō)明對(duì)應(yīng)的參考時(shí)鐘設(shè)置或參考時(shí)鐘的管腳約束有問(wèn)題,需要重新設(shè)置。

Loopback Mode:主要五個(gè)選項(xiàng),分為近端、遠(yuǎn)端的PCS和近端、遠(yuǎn)端PMA回環(huán),以及none。如果選擇none,則Tx端的碼流將會(huì)輸出,根據(jù)自行外部連接線再輸入到Rx端去,選擇外部連接一定要注意連接情況。

3.2 serial I/O Scans

serial I/O Scans用來(lái)生成GT鏈路的眼圖,可以在serial I/O Links頁(yè)面中右鍵添加scan以產(chǎn)生眼圖,也可以在serial I/O Scans頁(yè)面添加。

眼圖的橫坐標(biāo)為-0.5到0.5,表示一個(gè)數(shù)據(jù)的數(shù)字周期。

除了單次查看眼圖判斷信道質(zhì)量,還可以選擇sweep的方式來(lái)設(shè)置多組不同的參數(shù)生成眼圖的方式,這樣就可以獲取最佳預(yù)加重參數(shù),這樣一來(lái)在此后的接口設(shè)計(jì)當(dāng)中就可以使用到這樣的一組參數(shù),以此提供信號(hào)傳輸?shù)馁|(zhì)量。

-

收發(fā)器

+關(guān)注

關(guān)注

10文章

3834瀏覽量

111343 -

眼圖

+關(guān)注

關(guān)注

1文章

76瀏覽量

21792 -

誤碼率

+關(guān)注

關(guān)注

1文章

26瀏覽量

14475 -

Vivado

+關(guān)注

關(guān)注

19文章

859瀏覽量

71275

原文標(biāo)題:【vivado】 IBERT GT收發(fā)器誤碼率測(cè)試

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

是德科技全新多通道比特誤碼率測(cè)試儀

誤碼率測(cè)試儀的技術(shù)原理和應(yīng)用場(chǎng)景

#fpga 利用IBERT IP核實(shí)現(xiàn)GTX收發(fā)器硬件誤碼率測(cè)試實(shí)例

利用IBERT核對(duì)GTX收發(fā)器板級(jí)測(cè)試

基于FPGA的誤碼率測(cè)試儀的設(shè)計(jì)與實(shí)現(xiàn)

IP集成式誤碼率測(cè)試器(IBERT)的主要性能和優(yōu)勢(shì)介紹

BER誤碼率 影響誤碼率的因素

誤碼率是指什么_誤碼率是怎么表示_怎么計(jì)算

信道編碼中的誤碼率曲線與編碼增益及編碼設(shè)計(jì)的誤碼率分析

關(guān)于利用IBERT核對(duì)GTX收發(fā)器板級(jí)測(cè)試的原理與過(guò)程詳解

關(guān)于ZC706評(píng)估板的IBERT誤碼率測(cè)試和眼圖掃描詳細(xì)分析

利用IBERT IP核實(shí)現(xiàn)GTX收發(fā)器硬件誤碼率測(cè)試實(shí)例

如何在DS2652x STC上使用誤碼率測(cè)試儀

ZC706評(píng)估板IBERT誤碼率測(cè)試和眼圖掃描

基于IBERT的GTX數(shù)據(jù)傳輸測(cè)試

IBERT GT收發(fā)器誤碼率測(cè)試實(shí)例

IBERT GT收發(fā)器誤碼率測(cè)試實(shí)例

評(píng)論