如何使用FPGA驅(qū)動(dòng)并行ADC和DAC芯片,使用不同編碼方式的ADC與DAC時(shí)的注意事項(xiàng)

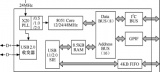

ADC和DAC是FPGA與外部信號(hào)的接口,從數(shù)據(jù)接口類型的角度劃分,有低速的串行接口和高速的并行接口....

復(fù)位電路的作用、控制方式和類型

復(fù)位電路也是數(shù)字邏輯設(shè)計(jì)中常用的電路,不管是 FPGA 還是 ASIC 設(shè)計(jì),都會(huì)涉及到復(fù)位,一般 ....

FPGA設(shè)計(jì)調(diào)試流程

調(diào)試,即Debug,有一定開發(fā)經(jīng)驗(yàn)的人一定會(huì)明確這是設(shè)計(jì)中最復(fù)雜最磨人的部分。對(duì)于一個(gè)龐大復(fù)雜的FP....

Verilog中signed和$signed()的用法

1、在verilog中有時(shí)會(huì)用signed修飾符來(lái)修飾定義的數(shù)據(jù),運(yùn)算的時(shí)候也會(huì)用$signed()....

FPGA上的圖像處理算法集成與優(yōu)化

本文詳細(xì)介紹了多種圖像處理技術(shù),包括RG/GB單通道提取、亮度和對(duì)比度調(diào)整、圖像反轉(zhuǎn)、均值濾波、高斯....

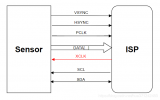

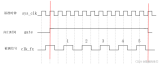

基于FPGA的DVP協(xié)議實(shí)現(xiàn)標(biāo)準(zhǔn)圖像數(shù)據(jù)流轉(zhuǎn)換

DVP(Digital Video Port) 是傳統(tǒng)的sensor輸出接口,采用并行輸出方式,d數(shù)....

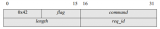

一文詳解JESD204B協(xié)議

其實(shí)使用到ADI的東西,基本也就沒有太去關(guān)注協(xié)議這些東西,只是簡(jiǎn)簡(jiǎn)單單的有個(gè)了解就行,在實(shí)際調(diào)試的時(shí)....

FPGA圖像處理基礎(chǔ)----實(shí)現(xiàn)緩存卷積窗口

像素行與像素窗口 一幅圖像是由一個(gè)個(gè)像素點(diǎn)構(gòu)成的,對(duì)于一幅480*272大小的圖片來(lái)說,其寬度是48....

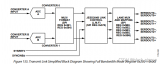

高速接口7系列收發(fā)器GTP介紹

1. 前言 最近在做以太網(wǎng)相關(guān)的東西,其中一個(gè)其中想要使用MAC通過光電轉(zhuǎn)換模塊來(lái)完成數(shù)據(jù)的收發(fā)。在....

RAM-Based Shift Register Xilinx IP核的使用

一般來(lái)講,如果要實(shí)現(xiàn)移位寄存器的話,通常都是寫RTL用reg來(lái)構(gòu)造,比如1bit變量移位一個(gè)時(shí)鐘周期....

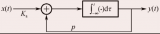

數(shù)字鎖相環(huán):二階環(huán)的FPGA實(shí)現(xiàn)

一.依據(jù)模擬環(huán)設(shè)計(jì)數(shù)字環(huán) 根據(jù)信號(hào)與系統(tǒng)的分析理論,一個(gè)系統(tǒng)完全由系統(tǒng)函數(shù)來(lái)確定,因此我們可從系統(tǒng)函....

FPGA頻率測(cè)量的三種方法

1、FPGA頻率測(cè)量? 頻率測(cè)量在電子設(shè)計(jì)和測(cè)量領(lǐng)域中經(jīng)常用到,因此對(duì)頻率測(cè)量方法的研究在實(shí)際工程應(yīng)....

Vivado Xilinx FFT IP核v9.0使用說明

一 傅里葉變換FFT 想必大家對(duì)傅里葉老人家都不陌生了,網(wǎng)上也有這方面的很多資料。通過FFT將時(shí)域信....

基于FPGA的GigE Vision相機(jī)圖像采集方案設(shè)計(jì)

1 概述 GigE Vision是一個(gè)比較復(fù)雜的協(xié)議,要在FPGA中完全實(shí)現(xiàn)具有較大的難度。如果FP....

FPGA在AI方面有哪些應(yīng)用

隨著人工智能技術(shù)的飛速發(fā)展,對(duì)計(jì)算性能的需求也日益增長(zhǎng)。FPGA(現(xiàn)場(chǎng)可編程門陣列)作為一種高性能、....

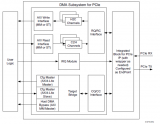

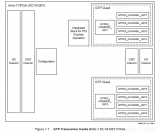

ZYNQ基礎(chǔ)---AXI DMA使用

前言 在ZYNQ中進(jìn)行PL-PS數(shù)據(jù)交互的時(shí)候,經(jīng)常會(huì)使用到DMA,其實(shí)在前面的ZYNQ學(xué)習(xí)當(dāng)中,也....

FIFO IP核的使用教程

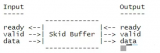

在數(shù)字設(shè)計(jì)中,利用FIFO進(jìn)行數(shù)據(jù)處理是非常普遍的應(yīng)用,例如,實(shí)現(xiàn)時(shí)鐘域交叉、低延時(shí)存儲(chǔ)器緩存、總線....

基于FPGA的CIC濾波器設(shè)計(jì)

這個(gè)概念是相對(duì)于單速率(Single Rate)信號(hào)處理而言的。單速率 是指整個(gè)信號(hào)處理流程中只有一....

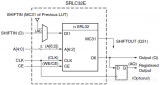

利用FPGA實(shí)現(xiàn)USB 2.0通信接口

USB?2.0接口的實(shí)現(xiàn)方式 利用FPGA來(lái)實(shí)現(xiàn)USB 2.0接口的方式一般有兩種,一是借助外圍的U....