為滿足對(duì) “納秒級(jí)實(shí)時(shí)響應(yīng)” 與 “復(fù)雜數(shù)據(jù)深度運(yùn)算” 的雙重需求,“FPGA+GPU”異構(gòu)混合部署方案通過(guò)硬件功能精準(zhǔn)拆分與高速協(xié)同,突破單一硬件的性能瓶頸 ——FPGA聚焦低延遲實(shí)時(shí)交易鏈路,GPU承接高復(fù)雜度數(shù)據(jù)處理任務(wù),形成 “實(shí)時(shí)執(zhí)行+智能分析” 的閉環(huán)架構(gòu)。

1.FPGA+GPU異構(gòu)架構(gòu)的優(yōu)勢(shì)

高頻量化交易的核心矛盾在于 “實(shí)時(shí)性” 與 “復(fù)雜性” 的平衡:

單一FPGA雖能實(shí)現(xiàn)納秒級(jí)延遲(端到端≤200ns),但硬件邏輯資源有限(如 Xilinx Alveo U250的LUT資源約35萬(wàn)),難以承載多維度訂單流分析、機(jī)器學(xué)習(xí)模型推理等復(fù)雜計(jì)算(如100個(gè)品種的協(xié)整檢驗(yàn)、LSTM價(jià)格預(yù)測(cè));

單一GPU雖具備每秒千萬(wàn)級(jí)并行運(yùn)算能力(如NVIDIA A100的FP32算力達(dá)19.5TFLOPS),但存在顯存通信延遲(約0.5-2μs)與指令調(diào)度開(kāi)銷(xiāo),無(wú)法滿足做市商、閃電套利等策略對(duì) “微秒必爭(zhēng)” 的響應(yīng)要求;

因此,F(xiàn)PGA+GPU異構(gòu)架構(gòu)通過(guò)功能互補(bǔ)解決上述矛盾:FPGA承接 “行情→指令→報(bào)單” 的低延遲鏈路,GPU負(fù)責(zé)“數(shù)據(jù)→分析→預(yù)測(cè)”的復(fù)雜運(yùn)算,兩者通過(guò)高速接口協(xié)同,兼顧快與準(zhǔn)。

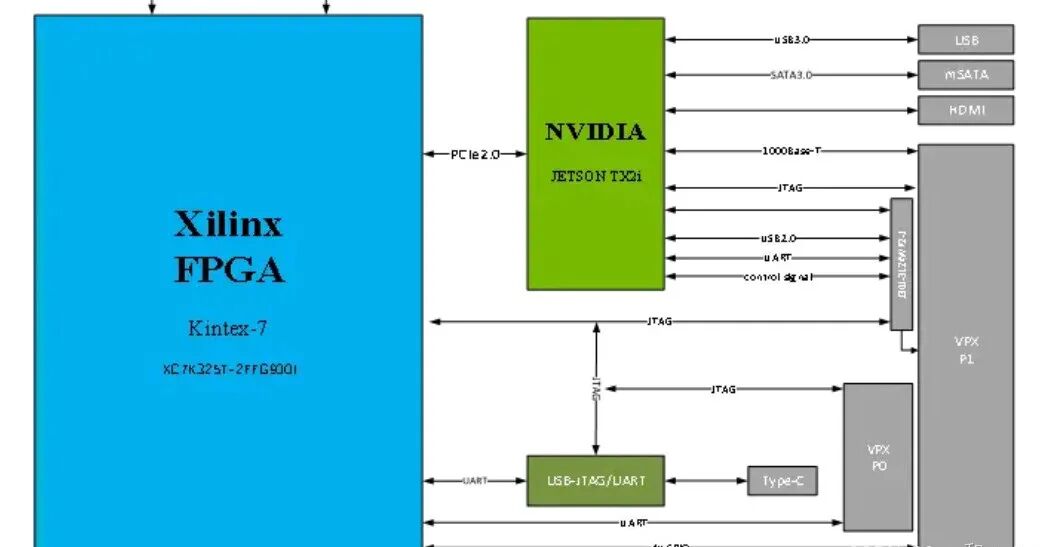

2.FPGA+GPU多層協(xié)同核心架構(gòu)

FPGA+GPU異構(gòu)方案以功能分層、數(shù)據(jù)高速流轉(zhuǎn)為核心,整體架構(gòu)分為三層,各層通過(guò)標(biāo)準(zhǔn)化接口銜接,形成無(wú)瓶頸的交易閉環(huán):

| 架構(gòu)層級(jí) | 核心硬件 | 核心功能 | 延遲目標(biāo) | 數(shù)據(jù)流向 |

|---|---|---|---|---|

| 實(shí)時(shí)執(zhí)行層 | FPGA(如Xilinx Alveo U250、Intel Stratix 10) | 行情接收解析、交易指令生成、報(bào)單發(fā)送、風(fēng)險(xiǎn)實(shí)時(shí)校驗(yàn) | 端到端≤200ns | 交易所行情→FPGA→GPU(預(yù)處理后數(shù)據(jù));GPU預(yù)測(cè)結(jié)果→FPGA→交易所報(bào)單 |

| 智能分析層 | GPU(如NVIDIA A100、RTX4090) | 訂單流深度分析、機(jī)器學(xué)習(xí)模型推理(價(jià)格預(yù)測(cè)、套利機(jī)會(huì)識(shí)別)、多品種風(fēng)險(xiǎn)測(cè)算 | 復(fù)雜任務(wù)≤1ms | FPGA預(yù)處理數(shù)據(jù)→GPU;GPU 分析 / 預(yù)測(cè)結(jié)果→FPGA |

| 數(shù)據(jù)支撐層 | 高速存儲(chǔ)(如NVMe SSD、DDR5)+ 主機(jī)CPU | 歷史數(shù)據(jù)緩存、策略參數(shù)配置、交易日志存儲(chǔ) | 數(shù)據(jù)讀寫(xiě)≤100ns | 主機(jī)→GPU(歷史數(shù)據(jù));FPGA/GPU→主機(jī)(日志 / 結(jié)果) |

其中:

1.FPGA與GPU:采用PCIe 4.0/5.0接口(帶寬分別達(dá)8GB/s、16GB/s,延遲≤10ns),實(shí)現(xiàn)納秒級(jí)數(shù)據(jù)交互;

2.FPGA與交易所:通過(guò)100Gbps低延遲光模塊(如 Arista 7050X3+DPDK(數(shù)據(jù)平面開(kāi)發(fā)套件),規(guī)避操作系統(tǒng)內(nèi)核延遲,網(wǎng)絡(luò)延遲≤1μs;

3.GPU與存儲(chǔ):通過(guò)NVMe-oF(NVMe over Fabrics)協(xié)議,直接訪問(wèn)遠(yuǎn)端高速存儲(chǔ),避免CPU中轉(zhuǎn)開(kāi)銷(xiāo)。

3.FPGA與GPU協(xié)同

3.1 高速數(shù)據(jù)交互:PCIe 4.0/5.0的納秒級(jí)傳輸

硬件接口:采用 PCIe 4.0(帶寬8GB/s)或PCIe 5.0(帶寬 16GB/s),F(xiàn)PGA 作為PCIe從設(shè)備,GPU作為主設(shè)備,數(shù)據(jù)傳輸延遲≤10ns(遠(yuǎn)低于高頻交易的微秒級(jí)需求);

數(shù)據(jù)格式:統(tǒng)一采用“AXI-Stream流數(shù)據(jù)格式”(FPGA 側(cè))與 “CUDA Array格式”(GPU 側(cè)),避免數(shù)據(jù)格式轉(zhuǎn)換開(kāi)銷(xiāo);例如,F(xiàn)PGA 將預(yù)處理后的訂單流數(shù)據(jù)按 “時(shí)間戳+品種ID+價(jià)格+成交量” 的固定結(jié)構(gòu)封裝,GPU直接按該結(jié)構(gòu)讀取,無(wú)需解析。

3.2 時(shí)間戳同步:PTP協(xié)議確保數(shù)據(jù)一致性

為避免FPGA與GPU的時(shí)間戳偏差導(dǎo)致策略誤判(如GPU用t=100ns的預(yù)測(cè)結(jié)果,F(xiàn)PGA用 t=200ns的行情執(zhí)行),通過(guò)PTPv2(精確時(shí)間協(xié)議) 實(shí)現(xiàn)時(shí)鐘同步:

部署PTP主時(shí)鐘(精度≤1ns),F(xiàn)PGA與GPU均作為從設(shè)備,每1ms校準(zhǔn)一次時(shí)鐘,同步誤差≤5ns;

所有數(shù)據(jù)(行情、預(yù)測(cè)結(jié)果、報(bào)單)均攜帶PTP時(shí)間戳,F(xiàn)PGA僅執(zhí)行 “時(shí)間戳匹配” 的預(yù)測(cè)結(jié)果(如GPU的t=100ns預(yù)測(cè),僅用于FPGAt=100-150ns的行情決策)。

3.3 任務(wù)調(diào)度:動(dòng)態(tài)優(yōu)先級(jí)分配策略

基于“實(shí)時(shí)性優(yōu)先級(jí)”動(dòng)態(tài)分配任務(wù):

高優(yōu)先級(jí)任務(wù)(如行情解析、報(bào)單發(fā)送):固定分配給FPGA,獨(dú)占硬件邏輯資源,確保無(wú)延遲波動(dòng);

中優(yōu)先級(jí)任務(wù)(如訂單流特征提取、實(shí)時(shí)風(fēng)險(xiǎn)測(cè)算):FPGA預(yù)處理后,GPU并行計(jì)算,結(jié)果1ms 內(nèi)反饋;

低優(yōu)先級(jí)任務(wù)(如歷史回測(cè)、參數(shù)優(yōu)化):非交易時(shí)段(如盤(pán)后)由GPU獨(dú)占處理,避免占用交易時(shí)段資源;

調(diào)度實(shí)現(xiàn):通過(guò)主機(jī)CPU的 “任務(wù)調(diào)度器”(如基于Linux的RT_PREEMPT實(shí)時(shí)內(nèi)核),實(shí)時(shí)監(jiān)控 FPGA與GPU的資源利用率,動(dòng)態(tài)調(diào)整任務(wù)分配(如交易高峰時(shí),暫停GPU的回測(cè)任務(wù),優(yōu)先保障實(shí)時(shí)分析)。

-

FPGA

+關(guān)注

關(guān)注

1662文章

22450瀏覽量

637739 -

接口

+關(guān)注

關(guān)注

33文章

9554瀏覽量

157340 -

gpu

+關(guān)注

關(guān)注

28文章

5227瀏覽量

135825

原文標(biāo)題:FPGA+GPU異構(gòu)混合部署方案設(shè)計(jì)

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

什么是異構(gòu)并行計(jì)算

異構(gòu)計(jì)算的前世今生

Embedded SIG | 多 OS 混合部署框架

基于FPGA的異構(gòu)計(jì)算是趨勢(shì)

異構(gòu)計(jì)算的兩大派別 為什么需要異構(gòu)計(jì)算?

異構(gòu)混合并行編程模型及其研究綜述

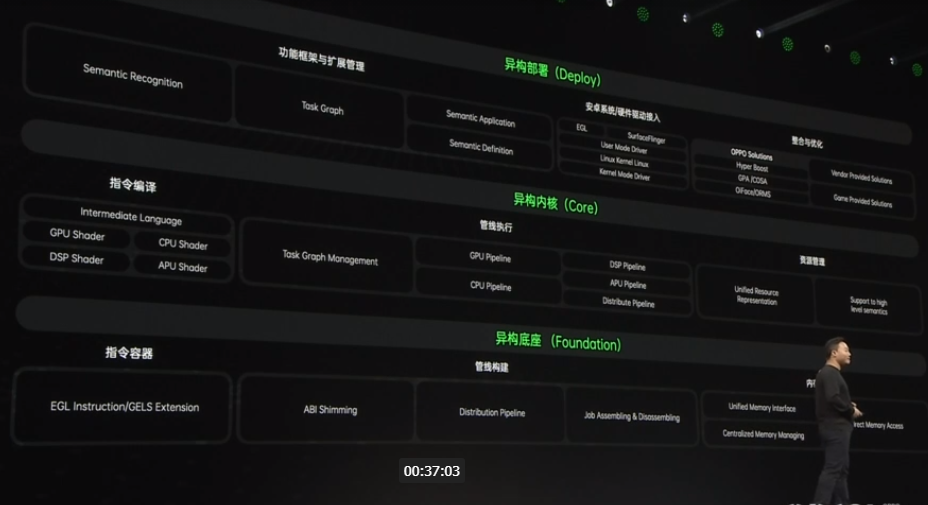

2021 OPPO開(kāi)發(fā)者大會(huì):異構(gòu)部署、異構(gòu)內(nèi)核、異構(gòu)底座

CPU+xPU的異構(gòu)方案解析 cpu和gpu有啥區(qū)別

【精彩回顧】ALINX亮相第七屆內(nèi)鏡大會(huì),發(fā)布FPGA+GPU異架構(gòu)高端醫(yī)療影像解決方案

打造異構(gòu)計(jì)算新標(biāo)桿!國(guó)數(shù)集聯(lián)發(fā)布首款CXL混合資源池參考設(shè)計(jì)

ALINX FPGA+GPU異架構(gòu)視頻圖像處理開(kāi)發(fā)平臺(tái)介紹

基于FPGA+GPU異構(gòu)平臺(tái)的遙感圖像切片解決方案

FPGA+GPU+CPU國(guó)產(chǎn)化人工智能平臺(tái)

FPGA+GPU異構(gòu)混合部署方案設(shè)計(jì)

FPGA+GPU異構(gòu)混合部署方案設(shè)計(jì)

評(píng)論