Vivado HLS是一款強大的高層次綜合工具,可將C/C++代碼轉換為硬件描述語言(HDL),顯著提升FPGA開發效率。

1. FIR參數確定

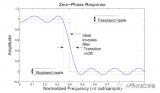

FIR濾波器的設計,首先要明確其技術指標,這些指標對濾波器的性能和資源占用起著關鍵作用。以一個低通濾波器為例,其具體參數如下:

濾波器階數設定為15。

采樣頻率是100MHz。

通帶截止頻率為20MHz。

阻帶起始頻率為30MHz。

通帶波紋要求在0.1dB以內。

阻帶衰減需達到60dB。

2. FIR系數計算

可以借助Python等工具來計算濾波器系數。下面是用Python計算系數的代碼:

importnumpyasnpfromscipyimportsignalimportmatplotlib.pyplotasplt# 濾波器參數order =15# 濾波器階數fs =100e6# 采樣頻率 (Hz)f_pass =20e6# 通帶截止頻率 (Hz)f_stop =30e6# 阻帶起始頻率 (Hz)A_pass =0.1# 通帶波紋 (dB)A_stop =60# 阻帶衰減 (dB)# 歸一化頻率nyquist =0.5* fs wp = f_pass / nyquist ws = f_stop / nyquist# 計算FIR濾波器系數(使用 Parks-McClellan 算法)h = signal.remez(order +1, [0, wp, ws,1.0], [1,0], Hz=1.0)# 打印系數(量化為16位定點數)coeffs_q15 = [int(round(c *32767))forcinh]print("FIR系數 (Q15格式):")fori, cinenumerate(coeffs_q15): print(f"h[{i}] ={c}, 即{c/32768:.10f}")# 繪制頻率響應w, h_freq = signal.freqz(h) plt.figure() plt.plot(0.5*fs*w/np.pi,20*np.log10(np.abs(h_freq))) plt.title('FIR濾波器頻率響應') plt.xlabel('頻率 (Hz)') plt.ylabel('幅度 (dB)') plt.grid(True) plt.axvline(f_pass, color='green') # 通帶截止頻率plt.axvline(f_stop, color='red') # 阻帶起始頻率plt.show()

3. C/C++代碼實現

使用Vivado HLS特定的數據類型和指令:

#include"fir.h"voidfir(data_t*output,data_tinput){ // 定義FIR系數(Q15格式)constcoeff_th[NUM_TAPS] = { -10,-22,-32,-37,-26,10,72,133, 171,171,133,72,10,-26,-37,-32,-22,-10 }; // 聲明移位寄存器數組staticdata_tshift_reg[NUM_TAPS]; // pragma指令,優化循環展開#pragmaHLS ARRAY_PARTITION variable=shift_reg complete dim=1// 數據移位操作for(inti = NUM_TAPS -1; i >0; i--) { #pragmaHLS UNROLL shift_reg[i] = shift_reg[i-1]; } shift_reg[0] = input; // 執行乘法累加操作acc_tacc =0; for(inti =0; i < NUM_TAPS; i++) { ? ? ? ?#pragma?HLS UNROLL? ? ? ? ?acc += shift_reg[i] * h[i]; ? ? } ? ? ? ??// 輸出結果? ? ?*output = acc >>15;// Q15格式轉換}

定義頭文件:

#ifndef_FIR_H_#define_FIR_H_#include"ap_fixed.h"http:// 定義數據類型typedefap_fixed<16,?1>data_t; // 16位定點數,1位整數,15位小數typedefap_fixed<16,?1>coeff_t; // 系數類型typedefap_fixed<32,?17>acc_t; // 累加器類型,防止溢出// 定義濾波器抽頭數#defineNUM_TAPS 19// 函數原型voidfir(data_t*output,data_tinput);#endif

定義測試程序:

#include"fir.h"#include#include #include #definePI 3.14159265358979323846intmain(){ // 測試數據data_tinput[100]; data_toutput[100]; // 生成測試信號(混合了5MHz和40MHz的正弦波)for(inti =0; i

4. Vivado HLS項目創建與配置

4.1 在Vivado HLS中創建新項目并配置

1.打開Vivado HLS工具。

2.執行 "File > New Project" 命令來創建一個新的項目。

3.為項目命名,例如 "FIR_Filter",并選擇合適的存儲位置。

4.添加源文件,即前面編寫的fir.c和fir.h。

5.添加測試平臺文件tb_fir.c。

6.指定目標設備,比如xc7z020clg400-1。

7.配置解決方案,設置時鐘周期(例如 10ns)和復位類型。

4.2在Vivado HLS中執行C仿真

1.點擊 "Project > Run C Simulation"。

2.確保仿真順利完成,并且控制臺顯示 "Verification successful"。

3.可以使用 gnuplot 或 MATLAB 對輸出文件進行分析。

4.3執行C綜合以將C代碼轉換為RTL

1.選擇 "Solution > Run C Synthesis > Active Solution"。

2.綜合完成后,查看報告,重點關注:

資源利用率(DSP、LUT、FF 等)。

延遲(Latency)和吞吐量(Interval)。

關鍵路徑分析。

4.4進行RTL級仿真驗證

1.選擇 "Solution > Run C/RTL Co-simulation"。

2.選擇仿真工具(如VCS、ModelSim等)。

3.等待仿真完成,檢查結果是否與C仿真一致。

4.5導出IP

將設計導出為IP核供Vivado使用:

1.選擇 "Solution > Export RTL"。

2.保持默認設置,點擊 "OK"。

3.導出完成后,IP 核會出現在項目目錄的exported_ip文件夾中。

4.6在Vivado中集成IP

1.打開 Vivado,創建新工程或打開已有工程。

2.點擊 "Settings > IP > Repository",添加HLS導出的IP路徑。

3.在Block Design中添加FIR濾波器IP核。

4.完成系統集成(添加時鐘、復位等)。

5.生成比特流并下載到FPGA進行硬件驗證。

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636217 -

濾波器

+關注

關注

162文章

8411瀏覽量

185679 -

低通濾波器

+關注

關注

15文章

554瀏覽量

49005 -

Vivado

+關注

關注

19文章

857瀏覽量

71100

原文標題:通過vivado HLS設計一個FIR低通濾波器

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Vivado 使用Simulink設計FIR濾波器

并行FIR濾波器Verilog設計

基于MATLAB及FPGA的FIR低通濾波器的設計

HLS系列 – High Level Synthesis(HLS) 從一個最簡單的fir濾波器開始2

HLS系列 – High Level Synthesis(HLS) 從一個最簡單的fir濾波器開始3

HLS系列 – High Level Synthesis(HLS) 從一個最簡單的fir濾波器開始4

HLS系列 – High LevelSynthesis(HLS) 從一個最簡單的fir濾波器開始5

數字低通濾波器的設計

Matlab低通濾波器設定與實踐

通過vivado HLS設計一個FIR低通濾波器

通過vivado HLS設計一個FIR低通濾波器

評論