FFT 的輸出不是 “連續的頻率譜”,而是離散的、等寬的頻率區間,每個區間就稱為一個 “頻率倉”(簡稱 “倉”)。可以類比為:把 “0Hz 到最高可測頻率” 的范圍分成了 N 個并排的 “箱子”,每個箱子就是一個頻率倉,每個倉對應一個特定的頻率范圍,最終 FFT 會計算出 “每個箱子里的信號能量有多少”。

頻率倉有三個核心參數:

1.數量(N):一般是FFT的點數,例如1024點FFT 對應 1024 個倉。(只取前一半,后一半是冗余數據)

2. 中心頻率:每個倉的代表頻率,即表示該倉的頻率中點

例:44.1kHz 采樣率、1024 點 FFT,第 50 倉的中心頻率為:(50 * 44100)/1024 ≈ 2158Hz。

3. 分辨率(Δf):每個倉的 “寬度”(即頻率范圍),等于中心頻率的間隔

例:44.1kHz 采樣率、1024 點 FFT,分辨率≈43Hz—— 意味著每個倉覆蓋 43Hz 的頻率范圍

FFT 輸出的每個頻率倉對應一個復數,這個復數的 “模”(或模的平方)就代表了該倉內所有頻率成分的總能量(或功率)。

直觀理解:倉的能量越高,說明原始信號中 “屬于這個頻率范圍的成分越強”。

單位:能量通常與 “振幅平方” 成正比,實際應用中常以 “分貝(dB)” 或 “功率譜密度(PSD)” 表示。

在 FFT 輸出的所有頻率倉中,能量值最大的那個倉,就是 “能量最高的頻率倉”。

它的物理意義是:原始信號中 “強度最強” 的頻率成分,主要集中在這個倉對應的頻率范圍內。

簡單說,它代表了信號的 “主導頻率”—— 即信號中最 “突出” 的頻率成分。

注意

不是 “單個頻率”:能量最高的頻率倉代表的是一個 “頻率范圍”,而非精確的單個頻率(除非信號是純正弦波且正好落在倉的中心頻率上)。

分辨率的影響:FFT 點數越多(分辨率越高),頻率倉越窄,對 “主導頻率” 的定位越精確。例如,1024 點 FFT 的分辨率是 43Hz,而 8192 點 FFT 的分辨率可降至 5.4Hz,能更精準地找到能量最高的頻率范圍。

頻譜泄露:如果信號的頻率不正好落在倉的中心頻率上,能量會 “泄露” 到相鄰的倉中,可能導致誤以為相鄰倉的能量更高。實際應用中通常會用 “窗函數”(如漢寧窗)來減少頻譜泄露。

“能量最高的頻率倉代表基波頻率”,這并非絕對真理,而是針對周期信號(如正弦波、方波、三角波,或人聲、機械振動等具有周期性的信號)的一種普遍規律。其核心原因在于周期信號的諧波構成特性—— 基波是信號的 “根本頻率”,且通常擁有最高的能量。諧波的作用是 “修飾” 信號的細節(比如方波的陡峭邊緣由高次諧波構成),但信號的整體周期性、“基調”(如聲音的音調、振動的主頻率)完全由基波決定。因此,信號的大部分能量會分配給基波,以支撐其基本形態。

非周期信號(如脈沖信號)沒有 “基波” 概念,其頻譜是連續的,能量最高的倉僅代表信號中能量最強的頻率成分,而非基波;

某些非線性系統產生的信號(如混沌振動),其諧波能量可能不隨頻率遞減,甚至出現高次諧波能量高于基波的情況。

FFT 的輸出是復數,每個頻率倉的復數都同時包含了該頻率分量的 “幅度信息” 和 “相位信息”,而功率則是幅度的衍生指標。

相位對應:FFT 的復數輸出天然包含頻率分量的相位信息,峰值倉位(最強分量)的復數輻角就是該分量的相位;

SINAD 計算:FFT 將有用信號(基波)、失真(諧波)、噪聲(非諧波隨機分量)分解到不同頻率倉,通過功率累加即可滿足 SINAD 的 “有用信號 / 干擾” 比值計算需求。

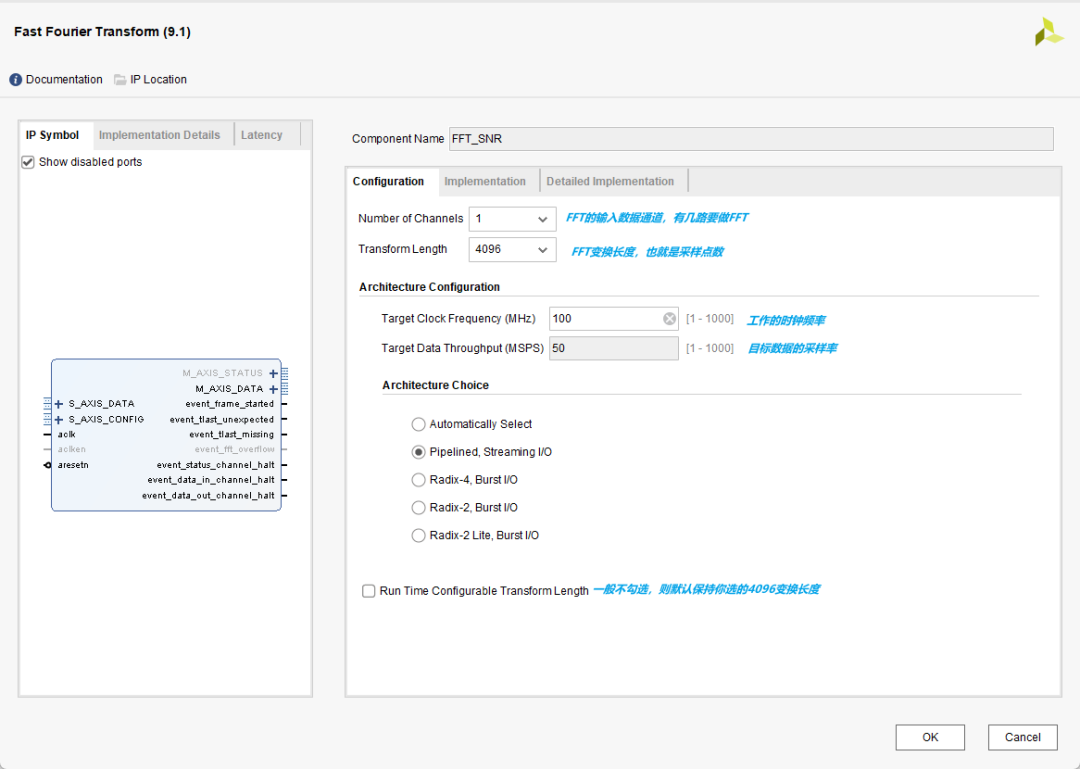

FFT IP核的配置

FFT的低位為實部,高位為虛部;

流水線I/O: 允許連續數據處理;

Radix-4突發I/O: 使用迭代方法分別加載和處理數據。使用資源大小比流水線解決方案小,但是轉換時間較長;

Radix-2突發I/O: 使用與基-4相同的迭代方法,但蝶形較小。使用資源比基-4更少,但是轉換時間更長;

Radix-2 Lite突發I/O: 基于基2體系結構,該變體使用時間復用方法使用更小的內核執行蝶形運算,代價是轉換時間更長

在上述的相位因子寬度(Phase Factor Width)直接影響 FFT 運算的精度、資源消耗和頻率響應特性。相位因子(即 FFT 蝶形運算中的旋轉因子)是 FFT 算法的核心系數,其位寬決定了旋轉因子的量化精度

1. 計算精度與誤差

舍入誤差:相位因子位寬越大,旋轉因子的量化精度越高,蝶形運算中的舍入誤差越小,最終 FFT 輸出的幅度和相位誤差越低。

低位寬(如 8 位)會導致旋轉因子近似度過低,高頻分量出現幅度衰減和相位偏移,甚至產生雜散。

高位寬(如 24 位)可將舍入誤差控制在極低水平,適合對精度要求高的場景(如通信、雷達信號處理)。

雜散與信噪比(SNR):相位因子精度不足會引入周期性量化誤差,表現為 FFT 頻譜中的雜散分量。根據 Xilinx 文檔,24 位或 25 位相位因子在浮點模式下可實現接近理想的噪聲性能,而低位寬(如 12 位)可能導致雜散電平上升 3~6 dB。

2. 資源消耗

相位因子寬度直接影響 IP 核的硬件資源占用:

存儲資源:旋轉因子需存儲在 BRAM 或分布式 RAM 中,位寬越大,所需 ROM 容量越大(例如,16 位相位因子的 ROM 容量是 8 位的 2 倍)。

計算資源:復數乘法(蝶形運算的核心)需 DSP 單元支持,高位寬會增加 DSP 的使用數量(如 24 位相位因子比 16 位多消耗約 30% 的 DSP)。

資源敏感場景(如小型 FPGA 或多 IP 核集成)需平衡精度與資源,避免過度占用。

3. 頻率響應一致性

相位因子的精度會影響 FFT 對不同頻率分量的響應一致性:

高位寬可保證各頻率點的幅度 / 相位響應更接近理想 FFT;

低位寬可能導致特定頻率(如高頻)的響應偏差,影響頻譜分析的準確性。

二、配置策略與最佳實踐

根據應用場景選擇相位因子寬度,參考以下建議:

1. 按數據格式選擇

定點模式(Fixed Point):相位因子寬度可在 8~34 位范圍內靈活配置:

低精度場景(如簡單頻譜監測、控制類應用):選擇 8~12 位,以最小化資源消耗。

中等精度場景(如工業傳感、一般通信):選擇 16~20 位,平衡精度與資源。

高精度場景(如雷達、寬帶通信、科學計算):選擇 24~34 位,確保低誤差和高信噪比。

浮點模式(Floating Point):相位因子寬度固定為 24 或 25 位(Xilinx 優化后的默認值),以在噪聲性能和資源消耗間取得平衡。

2. 按 FFT 結構選擇

FFT IP 核支持多種結構(如流水線 streaming、基 4 burst、基 2 burst),不同結構對相位因子寬度的敏感度不同:

流水線結構(高吞吐量,資源消耗大):可選擇較高位寬(如 16~24 位),利用其充裕的資源提升精度。

突發結構(低資源,中等吞吐量):建議選擇 12~16 位,避免資源過載。

3. 按系統需求驗證

若需嚴格保證精度,可通過仿真對比不同相位因子寬度的輸出:

用 MATLAB 生成理想 FFT 結果;

在 Vivado 中分別配置 8 位、16 位、24 位相位因子,對比輸出與理想結果的誤差;

選擇滿足精度要求且資源消耗合理的位寬。

在 FFT IP 核中,“Scaling Options”(縮放選項)用于控制 FFT 蝶形運算過程中數據的動態范圍,避免運算溢出的同時平衡精度,不同選項的核心區別的是 “如何處理數據位寬增長與溢出風險

1. Unscaled(無縮放)

行為:不對 FFT 蝶形運算的中間結果或最終結果進行任何縮放(即數據位寬完全 “自然增長”)。

適用場景:

FFT 點數極少(如 64 點),或輸入數據動態范圍嚴格受控,能確保所有蝶形運算都不會溢出;

對精度要求極高,且能接受 “溢出導致結果錯誤” 的風險(如實驗室低動態范圍的測試場景)。

缺點:長點數 FFT(如 4096 點)時,蝶形運算的多次復數乘法 / 加法會導致數據位寬急劇增長,幾乎必然溢出,最終結果會因 “數值回繞” 出現錯誤。

2. Scaled(固定比例縮放)

行為:對每一級蝶形運算的結果進行固定比例的縮放(如每級右移 1 位,相當于除以 2)。用戶可手動配置每一級的縮放因子。

適用場景:

FFT 點數較長(如 1024、4096 點),需要主動控制溢出風險;

對精度損失有 “確定性預期”(因為縮放比例固定,精度損失可預先計算)。

優點:能穩定避免溢出,且縮放規則簡單可控;

缺點:若縮放比例過大,會不必要地損失精度;若比例過小,仍可能溢出。

3. Block Floating Point(塊浮點)

行為:對整個數據塊(或 FFT 結果整體)進行自適應縮放—— 根據數據的實際動態范圍,自動調整每一級(或整體)的縮放因子(類似 “浮點運算”,但基于 “塊” 的定點縮放,無浮點的指數存儲開銷)。

適用場景:

對精度和動態范圍都有較高要求的場景(如寬帶通信信號處理、高精度頻譜分析);

輸入數據動態范圍不確定,需要 “智能適配” 的場景。

優點:既能最大程度避免溢出,又能在保證動態范圍的前提下盡可能保留精度(因為縮放因子是 “自適應” 的,不會過度損失低位);

缺點:實現邏輯比 “固定縮放” 更復雜,且縮放因子的自適應過程可能引入微小的額外延遲。

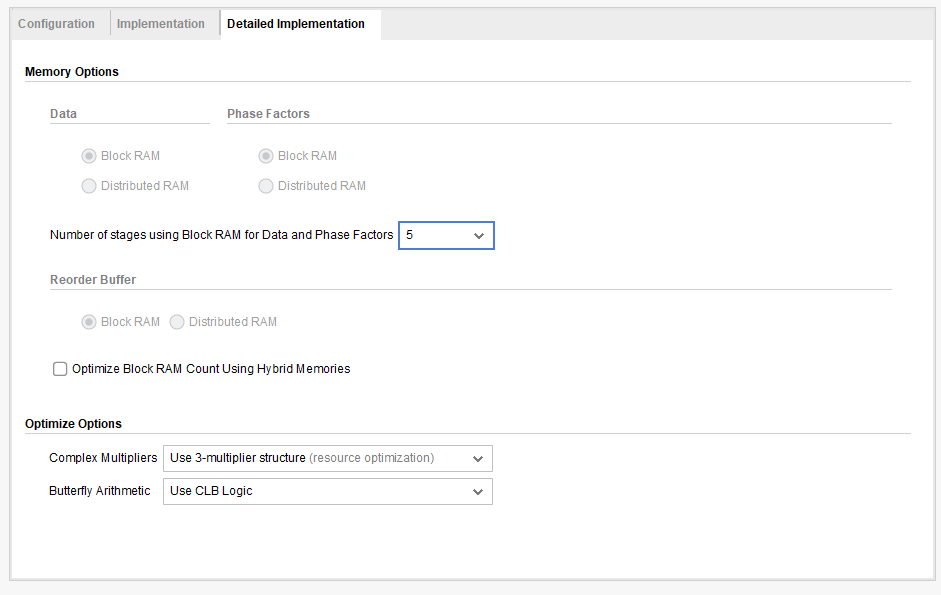

可以不進行配置這個界面保持默認

側邊欄顯示所需的時間,根據自己的實際項目來評估是否滿足實時性要求。

FFT中的握手機制

1.tvalid與tready的職責

s_axis_data_tvalid :由 TB(數據發送方,“主設備”)驅動,表示 “當前tdata上的數據有效,請求被接收”。

s_axis_data_tready :由 FFT IP 核(數據接收方,“從設備”)驅動,表示 “FFT 已準備好接收數據,允許傳輸”。

2. 數據傳輸的條件

只有當tvalid==1且tready==1時,當前時鐘上升沿才會完成 “數據從 TB 到 FFT” 的傳輸。

3. 傳輸過程的直觀理解

情況 1:FFT 一直準備好(tready==1):TB 每拍都能成功發送數據,data_idx每拍 +1,直到發完所有數據。

情況 2:FFT 暫時沒準備好(tready==0):TB 會 “重復發送當前數據”(tdata保持不變,tvalid保持 1),直到 FFT 準備好(tready==1),此時數據被接收,data_idx+1,開始發下一個數據。

這種機制是 AXI4-Stream 協議的核心設計,目的是讓 “數據發送方” 和 “數據接收方” 異步協調,避免數據丟失(發送方不盲目發,只在接收方準備好時發)。

補充:代碼中無需 “主動驅動tready”

因為tready是FFT IP 核的輸出信號(由 FFT 內部邏輯決定何時準備好),TB 作為 “發送方”,只需要讀取tready的狀態,來判斷 “當前數據是否能被接收”,不需要(也不能)主動修改tready。

-

FFT

+關注

關注

15文章

458瀏覽量

63180 -

頻率

+關注

關注

4文章

1588瀏覽量

62236 -

IP核

+關注

關注

4文章

344瀏覽量

52054

原文標題:FFT的頻率倉與IP核配置

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

xilinx DDR sdram IP核配置文檔

IP 核配置——DDR2 控制器 求助

IP核配置DDR2控制器出現黑屏

基于FPGA的FFT和IFFT IP核應用實例

【原創】Altera:A10 DDR3 IP核配置教程

Xilinx:K7 DDR3 IP核配置教程

利用面向對象技術進行可配置的FFT IP設計與實現

Linux內核配置系統詳解

可配置FFT IP核的實現及基礎教程

Gowin FFT IP用戶指南

詳解FFT的頻率倉與IP核配置

詳解FFT的頻率倉與IP核配置

評論