Xilinx Shift RAM IP概述和主要功能

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一個(gè) LogiCORE IP....

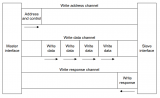

AXI協(xié)議規(guī)范總結(jié)

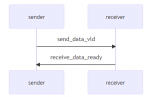

寫數(shù)據(jù)通道從主設(shè)備傳輸數(shù)據(jù)到從設(shè)備,在寫傳輸時(shí),從設(shè)備使用寫響應(yīng)通道通知主設(shè)備傳輸完成。

verilog模塊的調(diào)用、任務(wù)和函數(shù)

在做模塊劃分時(shí),通常會(huì)出現(xiàn)這種情形,某個(gè)大的模塊中包含了一個(gè)或多個(gè)功能子模塊,verilog是通過模....

在Vivado調(diào)用MIG產(chǎn)生DDR3的問題解析

下面是調(diào)用的DDR3模塊的,模塊的倒數(shù)第二行是,模塊的時(shí)鐘輸入,時(shí)鐘源來自PLL產(chǎn)生的系統(tǒng)時(shí)鐘的倍頻....

FPGA EDA軟件的位流驗(yàn)證

位流驗(yàn)證,對(duì)于芯片研發(fā)是一個(gè)非常重要的測(cè)試手段,對(duì)于純軟件開發(fā)人員,最難理解的就是位流驗(yàn)證。在FPG....

Xilinx Ultrascale系列FPGA的時(shí)鐘資源與架構(gòu)解析

Ultrascale是賽靈思開發(fā)的支持包含步進(jìn)功能的增強(qiáng)型FPGA架構(gòu),相比7系列的28nm工藝,U....

FPGA時(shí)序約束之設(shè)置時(shí)鐘組

Vivado中時(shí)序分析工具默認(rèn)會(huì)分析設(shè)計(jì)中所有時(shí)鐘相關(guān)的時(shí)序路徑,除非時(shí)序約束中設(shè)置了時(shí)鐘組或fal....

ZYNQ FPGA的PS端IIC設(shè)備接口使用

zynq系列中的FPGA,都會(huì)自帶兩個(gè)iic設(shè)備,我們直接調(diào)用其接口函數(shù)即可運(yùn)用。使用xilinx官....

Vivado HLS設(shè)計(jì)流程

為了盡快把新產(chǎn)品推向市場(chǎng),數(shù)字系統(tǒng)的設(shè)計(jì)者需要考慮如何加速設(shè)計(jì)開發(fā)的周期。設(shè)計(jì)加速主要可以從“設(shè)計(jì)的....

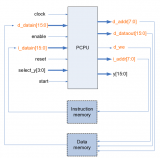

RISC-V五級(jí)流水線CPU設(shè)計(jì)

本文實(shí)現(xiàn)的CPU是一個(gè)五級(jí)流水線的精簡版CPU(也叫PCPU,即pipeline),包括IF(取指令....

Verilog編寫規(guī)范

用最右邊的字符下劃線代表低電平有效,高電平有效的信號(hào)不得以下劃線表示,短暫的有效信號(hào)建議采用高電平有....

一文詳解Video In to AXI4-Stream IP核

Video In to AXI4-Stream IP核用于將視頻源(帶有同步信號(hào)的時(shí)鐘并行視頻數(shù)據(jù),....

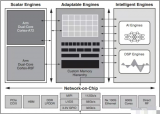

FPGA在數(shù)字化時(shí)代的主要發(fā)展趨勢(shì)

隨著數(shù)字化時(shí)代的飛速發(fā)展,人工智能(AI)、大數(shù)據(jù)分析、自動(dòng)駕駛等新興領(lǐng)域的需求不斷攀升。FPGA作....

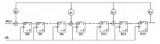

基于Verilog語言實(shí)現(xiàn)CRC校驗(yàn)

CRC即循環(huán)冗余校驗(yàn)碼:是數(shù)據(jù)通信領(lǐng)域中最常用的一種查錯(cuò)校驗(yàn)碼,其特征是信息字段和校驗(yàn)字段的長度可以....

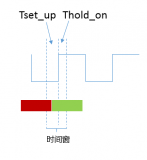

一文詳解Vivado時(shí)序約束

Vivado的時(shí)序約束是保存在xdc文件中,添加或創(chuàng)建設(shè)計(jì)的工程源文件后,需要?jiǎng)?chuàng)建xdc文件設(shè)置時(shí)序....

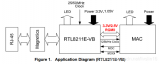

千兆網(wǎng)絡(luò)PHY芯片RTL8211E的實(shí)踐應(yīng)用

以太網(wǎng)MAC模塊負(fù)責(zé)實(shí)現(xiàn)以太網(wǎng)MAC子層的功能,完成802.3ab的數(shù)據(jù)封裝與解封。其同時(shí)負(fù)責(zé)適配硬....

基于FPGA的DS18B20數(shù)字溫度傳感器測(cè)溫實(shí)例

本文將使用三段式狀態(tài)機(jī)(Moore型)的寫法來對(duì)DS18B20進(jìn)行測(cè)溫操作,以便了解DS18B20和....