FPGA測試DDR帶寬跑不滿的常見原因及分析方法

在 FPGA 中測試 DDR 帶寬時(shí),帶寬無法跑滿是常見問題。下面我將從架構(gòu)、時(shí)序、訪問模式、工具限....

基于FPGA的CLAHE圖像增強(qiáng)算法設(shè)計(jì)

CLAHE圖像增強(qiáng)算法又稱為對(duì)比度有限的自適應(yīng)直方圖均衡算法,其算法原理是通過有限的調(diào)整圖像局部對(duì)比....

Aurora接口的核心特點(diǎn)和應(yīng)用場景

Aurora 是 Xilinx(賽靈思)推出的一種高速串行接口協(xié)議,主要用于 FPGA 之間或 FP....

JTAG標(biāo)準(zhǔn)的狀態(tài)機(jī)實(shí)現(xiàn)

JTAG作為一項(xiàng)國際標(biāo)準(zhǔn)測試協(xié)議(IEEE1149.1兼容),主要用于芯片內(nèi)部測試和調(diào)試。目前的主流....

高速總線接口的類型介紹

串行RapidIO,高速串行通信協(xié)議,旨在鏈接DSP、FPGA、網(wǎng)絡(luò)處理器等芯片,具有低延遲、高帶寬....

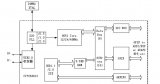

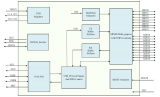

FPGA利用DMA IP核實(shí)現(xiàn)ADC數(shù)據(jù)采集

本文介紹如何利用FPGA和DMA技術(shù)處理來自AD9280和AD9708 ADC的數(shù)據(jù)。首先,探討了這....

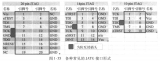

存儲(chǔ)技術(shù)全解析

在計(jì)算機(jī)和嵌入式系統(tǒng)中,各種存儲(chǔ)技術(shù)扮演著不同的角色,它們的性能特點(diǎn)和應(yīng)用場景各不相同。很多人對(duì)DR....

FPGA通信設(shè)計(jì)常見問答

FFT(快速傅里葉變換)是離散傅里葉變換(DFT)的高效實(shí)現(xiàn)算法,它的核心作用是快速將信號(hào)從時(shí)域轉(zhuǎn)換....

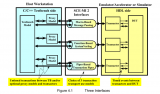

FPGA外接FT232H配置FIFO實(shí)現(xiàn)USB通信回環(huán)測試

USB英文全稱 Universal Serial Bus,即通用串行總線,是一個(gè)外部總線標(biāo)準(zhǔn),用于規(guī)....

FPGA在機(jī)器學(xué)習(xí)中的具體應(yīng)用

隨著機(jī)器學(xué)習(xí)和人工智能技術(shù)的迅猛發(fā)展,傳統(tǒng)的中央處理單元(CPU)和圖形處理單元(GPU)已經(jīng)無法滿....

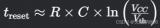

復(fù)位電路的核心功能和主要類型

復(fù)位電路(Reset Circuit) 是數(shù)字系統(tǒng)中的關(guān)鍵功能模塊,用于確保設(shè)備在上電、電壓波動(dòng)或異....

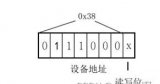

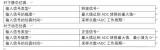

基于FPGA的AHT10溫濕度傳感器驅(qū)動(dòng)設(shè)計(jì)

傳感器輸出經(jīng)過標(biāo)定的數(shù)字信號(hào)輸出,通過標(biāo)準(zhǔn)的I2C接口傳輸數(shù)據(jù)。

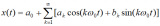

基于MATLAB實(shí)現(xiàn)FM調(diào)制解調(diào)

首先FM調(diào)制時(shí)屬于非線性調(diào)制中的一種,常見的非線性調(diào)制時(shí)FM(頻率調(diào)制),PM(相位)調(diào)制。

詳解ADC電路的靜態(tài)仿真和動(dòng)態(tài)仿真

ADC電路主要存在靜態(tài)仿真和動(dòng)態(tài)仿真兩類仿真,針對(duì)兩種不同的仿真,我們存在不同的輸入信號(hào)和不同的數(shù)據(jù)....

基于FPGA搭建神經(jīng)網(wǎng)絡(luò)的步驟解析

本文的目的是在一個(gè)神經(jīng)網(wǎng)絡(luò)已經(jīng)通過python或者M(jìn)ATLAB訓(xùn)練好的神經(jīng)網(wǎng)絡(luò)模型,將訓(xùn)練好的模型的....

基于FPGA的AM調(diào)制系統(tǒng)設(shè)計(jì)方案

本系統(tǒng)由FPGA、串口屏、DAC模塊和AD831組成。FPGA通過調(diào)用宏功能模塊NCO,按照輸入時(shí)鐘....

一文詳解頻率合成技術(shù)

一般是以高穩(wěn)定度參考源比如晶振所產(chǎn)生的頻率信號(hào)作為基準(zhǔn),經(jīng)過必要的的加減乘除運(yùn)算(對(duì)不同信號(hào)混頻可以....