在Vivado的時序約束中,-invert是用于控制信號極性的特殊參數,應用于時鐘約束(Clock Constraints)和延遲約束(Delay Constraints)中,用于指定信號的有效邊沿或邏輯極性。

1.-invert參數的作用

-invert參數的字面含義是 "反轉",其核心功能是告訴時序分析工具:信號的有效邊沿或邏輯電平與默認狀態相反。在數字電路中,信號通常有默認的有效狀態(如時鐘的上升沿有效、復位信號的低電平有效),而-invert參數允許設計者明確指定信號的實際有效狀態,確保時序分析結果與電路實際行為一致。

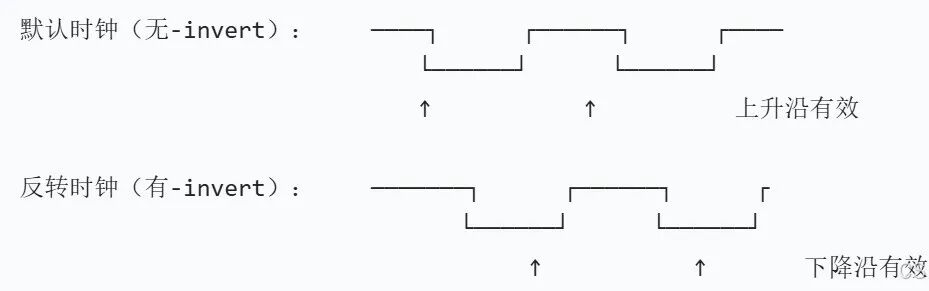

對于時鐘信號,Vivado默認假設上升沿為有效邊沿(即信號在上升沿觸發寄存器采樣)。當使用-invert參數時,表示該時鐘信號的下降沿為有效邊沿,時序分析工具會基于下降沿計算建立時間(Setup Time)和保持時間(Hold Time)。

對于復位信號或控制信號(如使能信號),-invert參數用于指定信號的有效電平與默認邏輯相反。例如,默認情況下工具可能認為高電平為有效狀態,使用-invert后則表示低電平為有效狀態。

2.-invert參數的應用場景

-invert參數主要用于以下兩類約束命令中,其語法格式和應用場景各有側重。

1.時鐘約束中-invert的典型應用是定義下降沿觸發的時鐘,語法格式如下:

# 基本語法:創建下降沿有效的時鐘create_clock -name-period -waveform { } -invert -ports # 示例:創建一個100MHz(周期10ns)的下降沿有效時鐘create_clock -name clk_100mhz -period 10 -waveform {5 10} -invert -ports [get_ports clk_in]

參數說明:

-name:指定時鐘名稱;

-period:時鐘周期(單位:ns);

-waveform:定義時鐘波形的上升沿和下降沿時間點(默認 {0 period/2},反轉時鐘通常設置為 {period/2 period});

-invert:指定時鐘下降沿有效;

-ports:指定時鐘輸入端口。

應用場景:

當電路中存在下降沿觸發的寄存器時(如always@(negedgeclk)描述的時序邏輯);

跨時鐘域交互中,需要明確區分上升沿和下降沿時鐘以避免時序沖突;

雙邊沿采樣電路(如 DDR 存儲器接口),需分別約束上升沿和下降沿時鐘。

2.延遲約束(如set_max_delay、set_min_delay)中-invert是反轉信號的邏輯極性。

# 基本語法:約束反轉極性信號的最大延遲 set_max_delay -invert-from -to # 示例:約束低電平有效的復位信號的最大延遲 set_max_delay -invert5-from [get_ports rst_n] -to[get_pins *reg/R]

參數說明:

-invert:指定信號為低電平有效(默認高電平有效);

-from/-to:指定延遲路徑的起點和終點。

應用場景:

低電平有效的復位信號(如rst_n),確保復位信號在低電平時的路徑延遲滿足要求;

低電平有效的使能信號(如enable_n),約束其有效狀態下的路徑延遲;

差分信號對中的負向信號(如clk_p和clk_n),明確信號極性以保證時序分析準確性。

3.-invert參數的工程實踐

波形設置與-invert的配合:

當使用-invert定義下降沿時鐘時,建議將-waveform設置為{period/2 period},使波形描述與實際有效邊沿一致:

# 正確:10ns周期的下降沿時鐘,波形從5ns開始下降create_clock-name clk_neg -period10-waveform {510} -invert -ports[get_ports clk_in]# 不推薦:波形與-invert含義沖突(仍以0ns為上升沿)create_clock-name clk_neg -period10-waveform {05} -invert -ports[get_ports clk_in]

與時鐘分組的協同:

下降沿時鐘應單獨分組或明確標記,避免與上升沿時鐘混淆:

# 將下降沿時鐘加入獨立時鐘組create_clock-name clk_neg -period10-invert -ports[get_ports clk_in]set_clock_groups-name neg_edge_clocks -group[get_clocks clk_neg]

跨時鐘域的時序處理:

當下降沿時鐘與上升沿時鐘交互時,需使用set_clock_uncertainty等約束明確時序關系:

# 為下降沿時鐘與上升沿時鐘之間的路徑設置額外不確定性set_clock_uncertainty0.5-from[get_clocks clk_neg] -to [get_clocks clk_pos]

復位信號的延遲約束:

對于低電平有效的復位信號(rst_n),使用-invert確保工具分析復位有效(低電平)時的路徑延遲:

# 約束rst_n(低有效)從輸入端口到寄存器復位端的最大延遲 set_max_delay -invert3-from[get_ports rst_n]-to[get_pins *reg/R]# 同時約束最小延遲,避免復位釋放時的競爭冒險 set_min_delay -invert0.5-from[get_ports rst_n]-to[get_pins *reg/R]

避免過度約束:

-invert僅需用于實際極性與默認相反的信號,對于高電平有效的信號無需添加,否則會導致時序分析錯誤:

# 錯誤:高電平有效信號不應使用-invert set_max_delay -invert2-from[get_ports enable]-to[get_pins *reg/CE]

與多周期路徑的配合:

當反轉極性的信號涉及多周期路徑時,需確保-invert參數與多周期約束協同工作:

# 為低電平有效的控制信號設置2周期路徑 set_multicycle_path2-setup -invert -from[get_ports ctrl_n]-to[get_pins data_reg/D]

-

FPGA

+關注

關注

1662文章

22455瀏覽量

637899 -

時序約束

+關注

關注

1文章

120瀏覽量

13982 -

Vivado

+關注

關注

19文章

859瀏覽量

71275

原文標題:FPGA時序約束分析——‘-invert’約束分析

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

VIVADO時序約束及STA基礎

FPGA主時鐘約束詳解 Vivado添加時序約束方法

FPGA中的時序約束設計

Vivado中的靜態時序分析工具Timing Report的使用與規范

Vivado時序約束中invert參數的作用和應用場景

Vivado時序約束中invert參數的作用和應用場景

評論