本章以太網通信實驗是基于ZYNQ-MZ702P開發板進行實現,在配置方面,需要讀者自主修改不同的地方。文章末尾有本項目原工程壓縮包,提供參考。

下面直接進行操作。

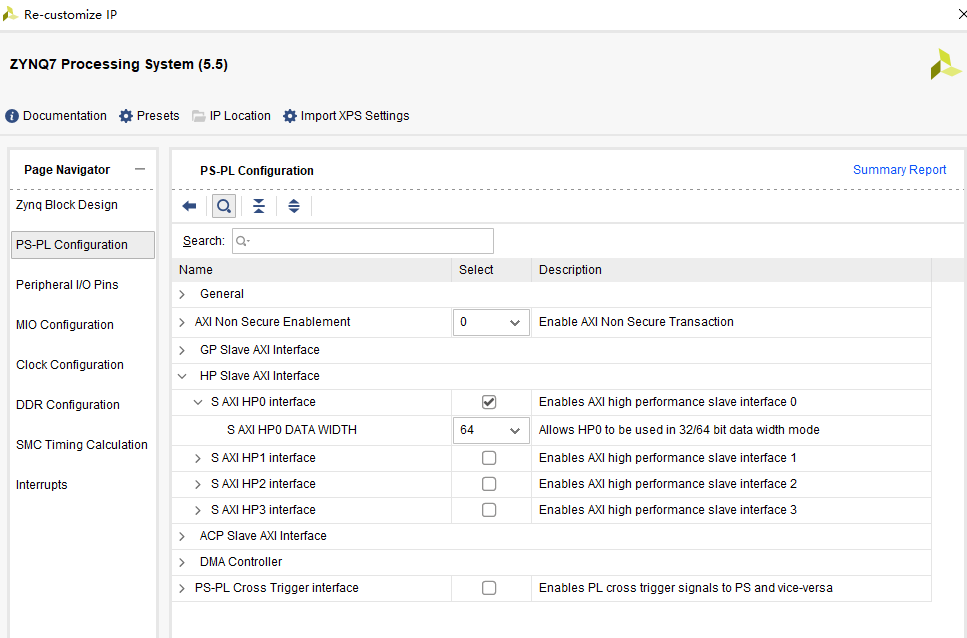

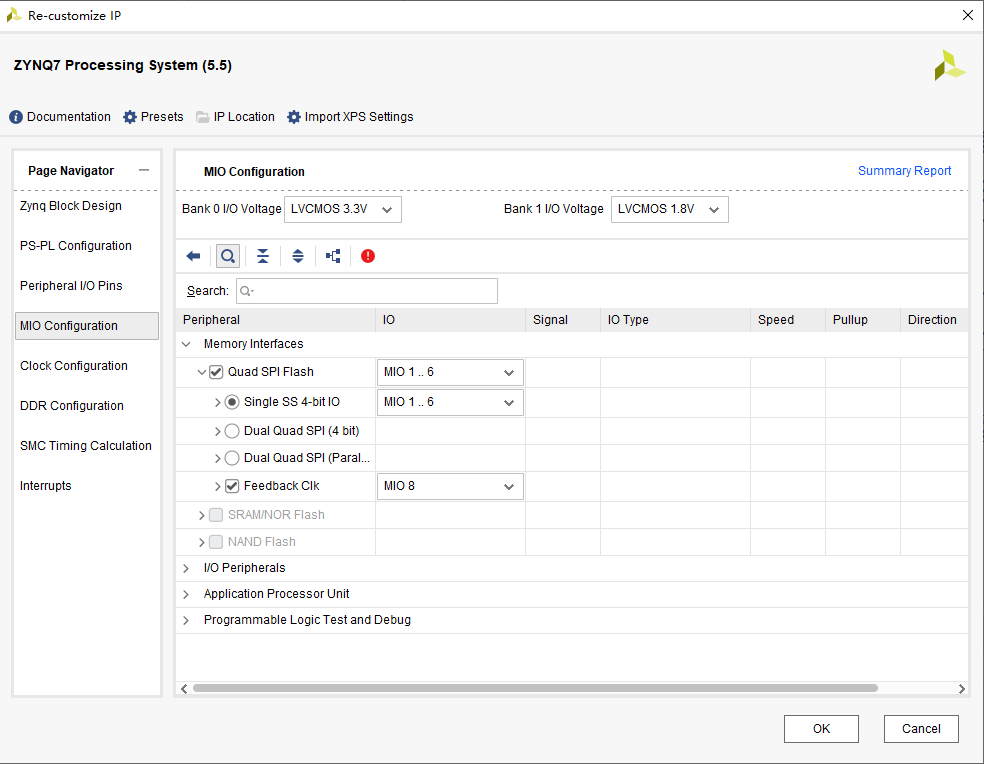

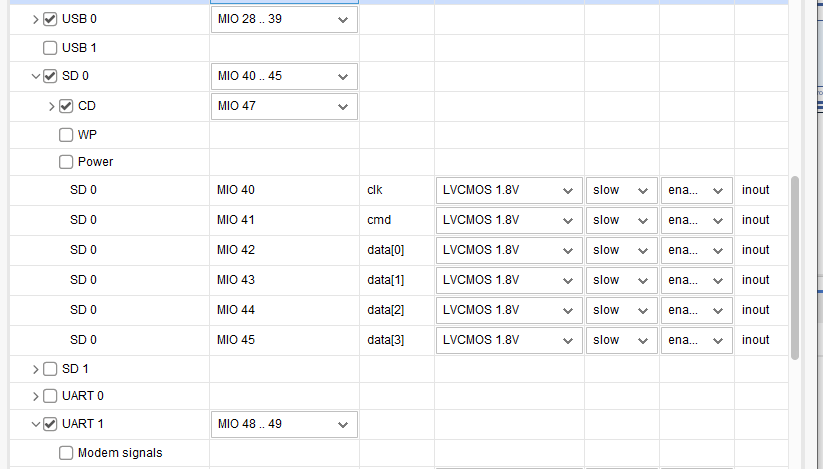

1.打開vivado,選擇好開發板芯片后,新建完成工程,點擊open block design,再點擊右邊Diagram框圖中的加號添加zynq再進行相關配置。

配置輸出時鐘。

下面根據個人使用的開發板進行配置。

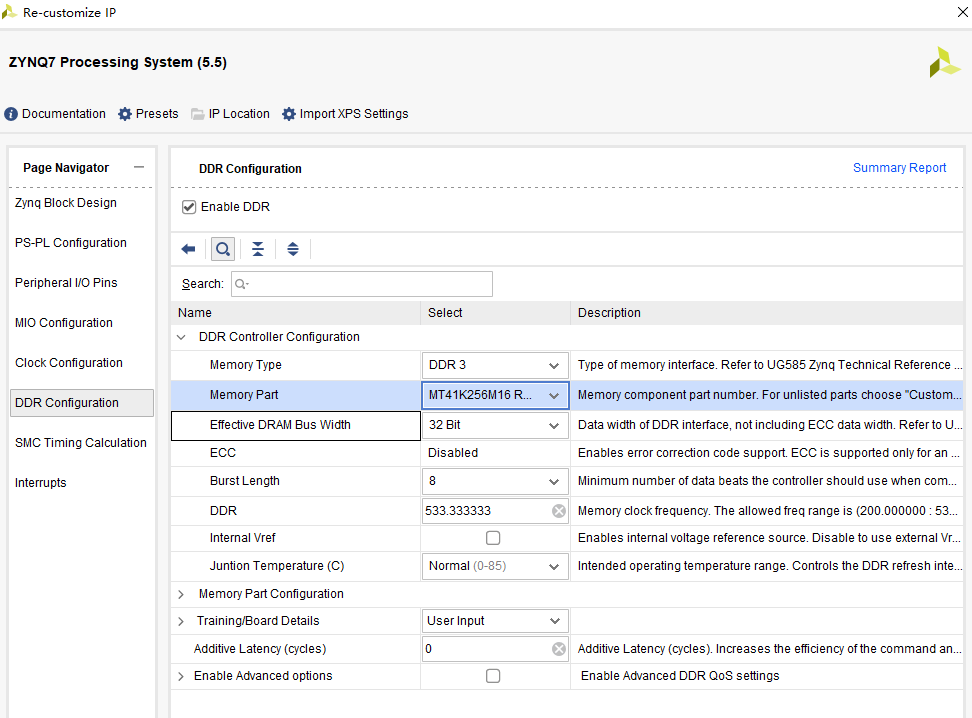

選擇DDR型號。

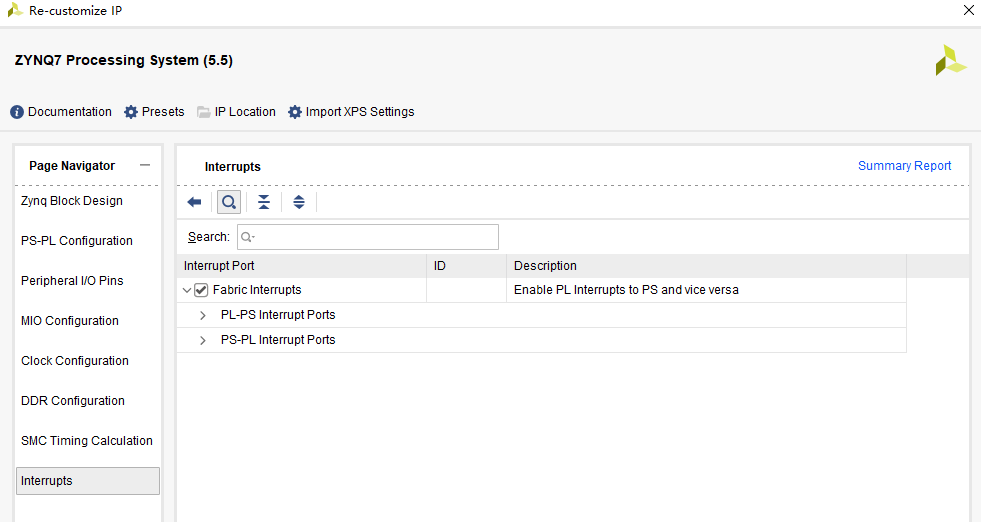

開啟中斷。

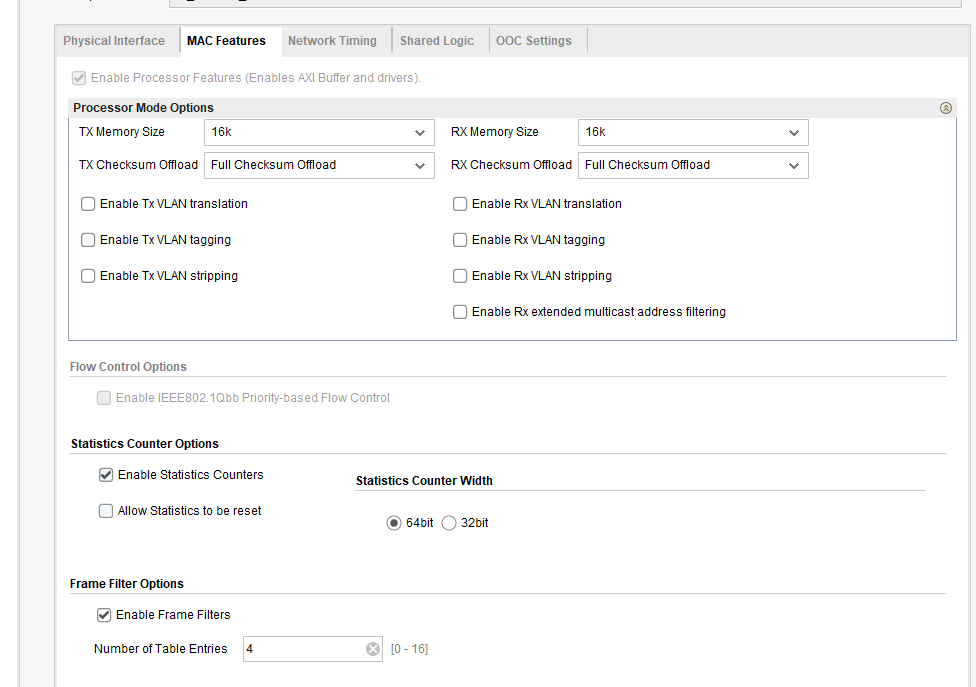

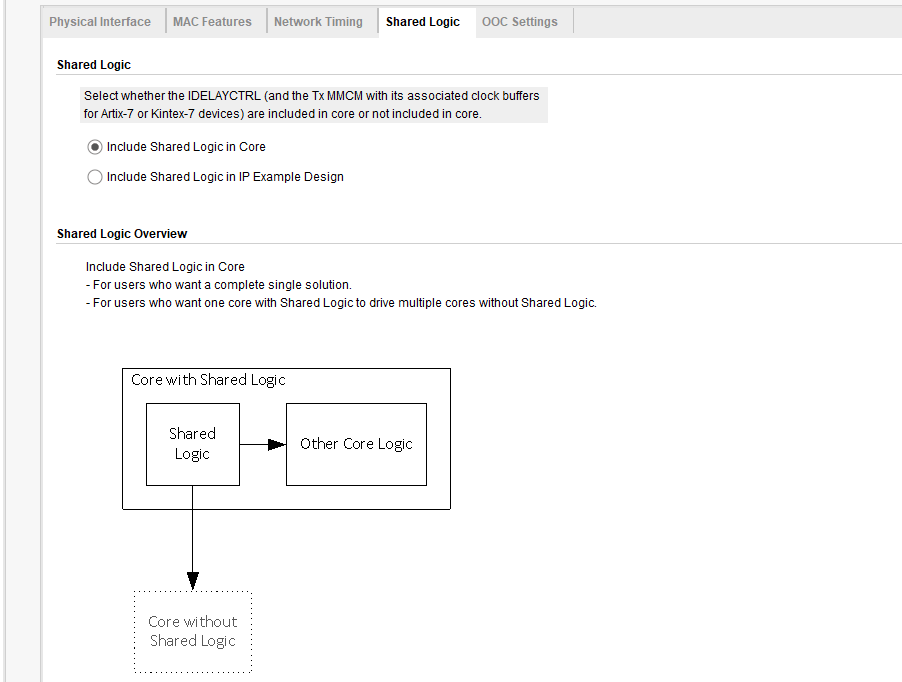

2.添加AXI 1G/2.5G Ethernet Subsystem模塊并進行配置。

其他保持默認即可,點擊OK。

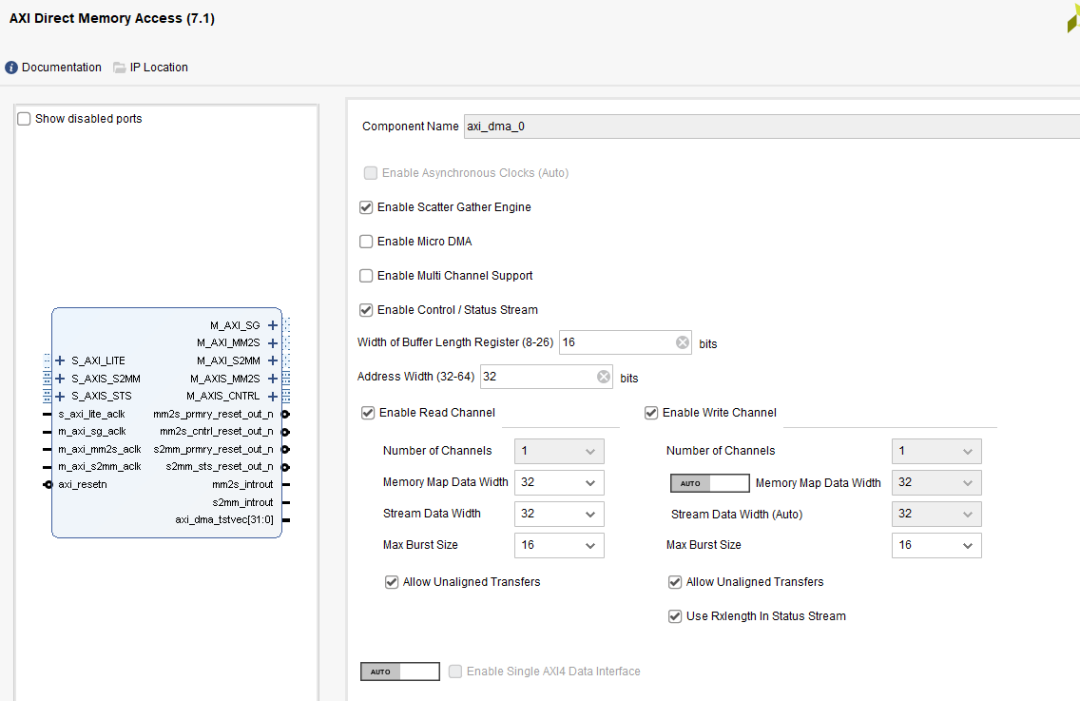

3.添加AXI Direct Memory Access模塊。

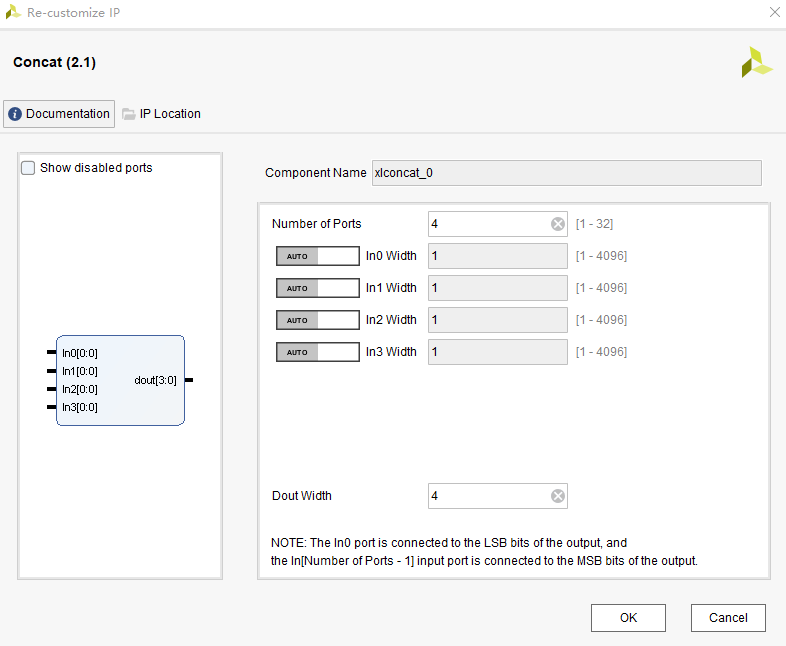

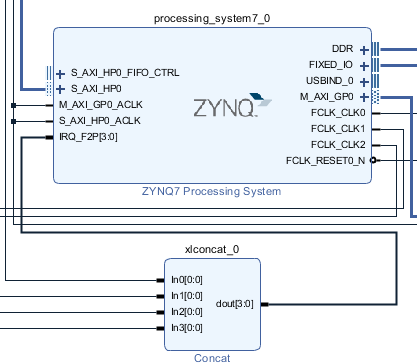

4.添加concat模塊,并修改為4個端口。連接PL至PS的中斷。

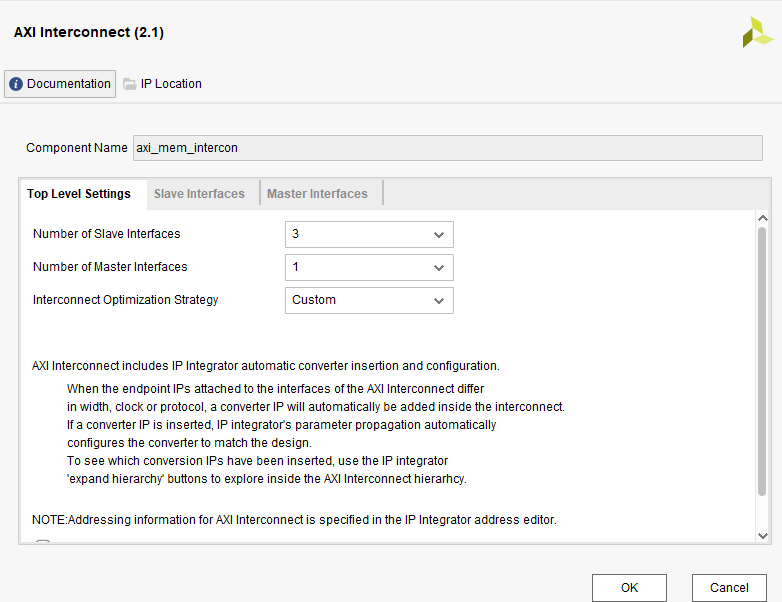

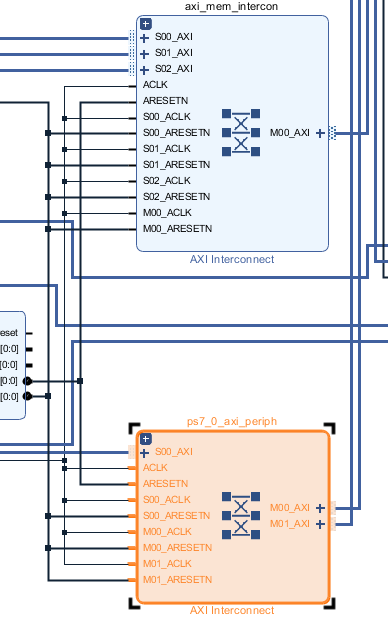

5.添加兩個AXI Interconnect模塊,其中一個默認,另一個進行修改。

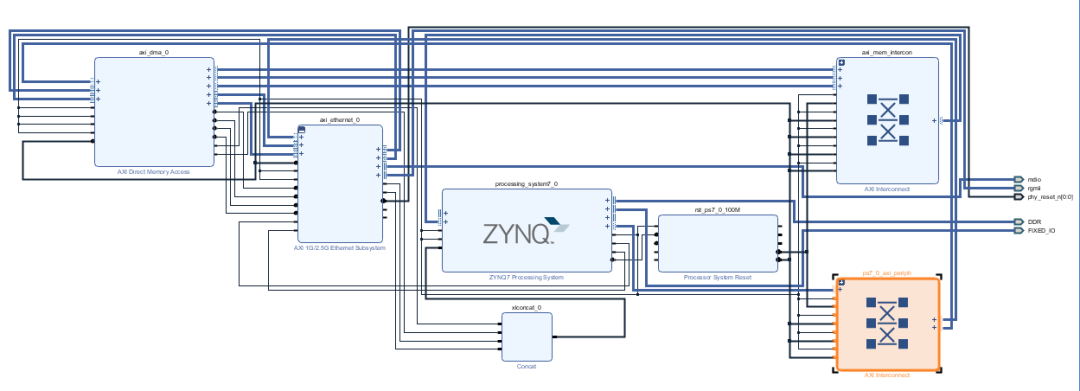

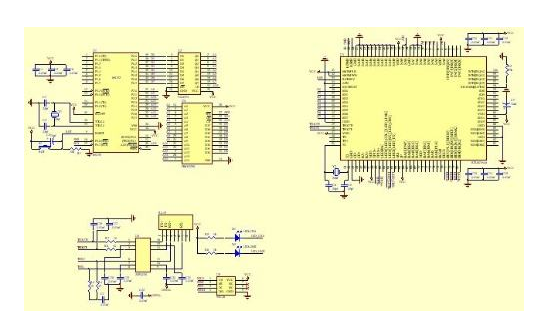

6.進行連線,先進行自動連線,不對的地方需要自己手動修改,最終連線效果如下圖。

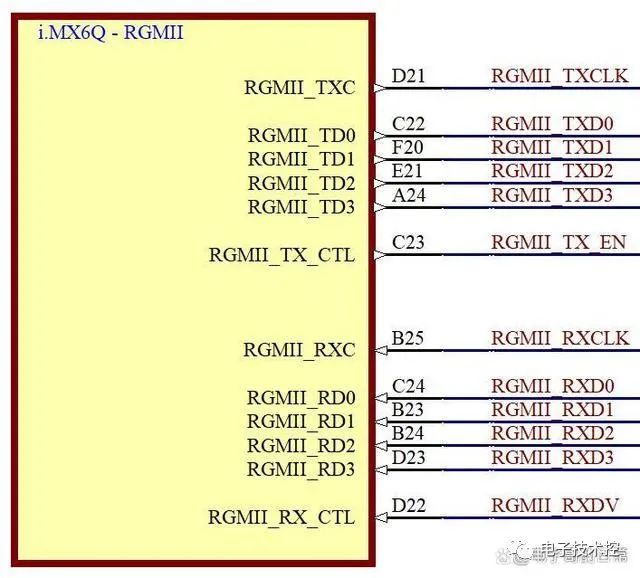

7.對引腳進行改名。

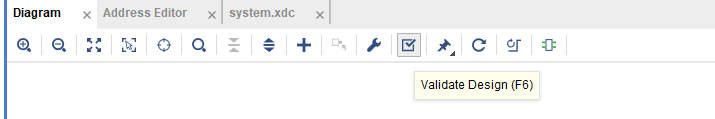

8.點擊Validate Design驗證block是否存在問題。

9.添加約束文件。

### -----------------RX------------------### set_property PACKAGE_PIN B19[get_ports rgmii_rxc]set_property PACKAGE_PIN A21[get_ports rgmii_rx_ctl]set_property PACKAGE_PIN B20[get_ports {rgmii_rd[0]}]set_property PACKAGE_PIN C18[get_ports {rgmii_rd[1]}]set_property PACKAGE_PIN A19[get_ports {rgmii_rd[2]}]set_property PACKAGE_PIN A18[get_ports {rgmii_rd[3]}]### -----------------TX------------------### set_property PACKAGE_PIN B15[get_ports rgmii_txc]set_property PACKAGE_PIN C15[get_ports rgmii_tx_ctl]set_property PACKAGE_PIN A17[get_ports {rgmii_td[0]}]set_property PACKAGE_PIN A16[get_ports {rgmii_td[1]}]set_property PACKAGE_PIN B17[get_ports {rgmii_td[2]}]set_property PACKAGE_PIN B16[get_ports {rgmii_td[3]}]set_property IOSTANDARD LVCMOS18[get_ports rgmii_rxc]set_property IOSTANDARD LVCMOS18[get_ports rgmii_rx_ctl]set_property IOSTANDARD LVCMOS18[get_ports {rgmii_rd[*]}]set_property IOSTANDARD LVCMOS18[get_ports rgmii_txc]set_property IOSTANDARD LVCMOS18[get_ports rgmii_tx_ctl]set_property IOSTANDARD LVCMOS18[get_ports {rgmii_td[*]}]set_property PACKAGE_PIN R18[get_ports mdio_mdc]set_property PACKAGE_PIN T17[get_ports mdio_mdio_io]set_property IOSTANDARD LVCMOS18[get_ports mdio_mdc]set_property IOSTANDARD LVCMOS18[get_ports mdio_mdio_io]set_property IOSTANDARD LVCMOS18[get_ports phy_reset_n_0[0]]set_property PACKAGE_PIN T19[get_ports phy_reset_n_0[0]]

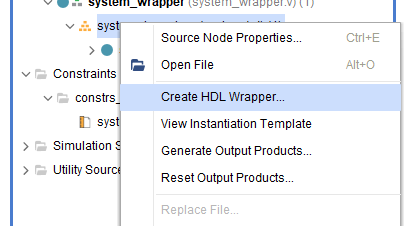

10.先生成頂層文件,再點擊下方的Generate Output...。

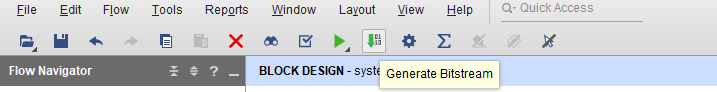

11.生成bit流文件。

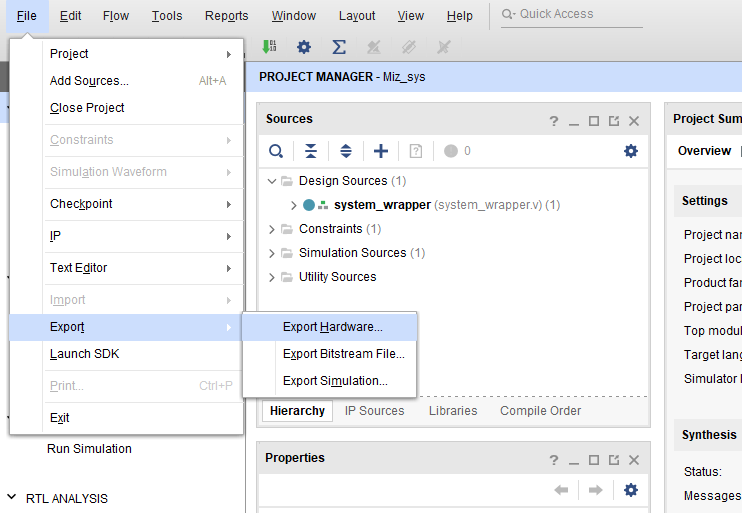

12.若生成比特流成功,則導出比特流,打開vitis軟件進行工程創建。若顯示失敗,參考本人另一帖子。https://blog.csdn.net/c_lllll_ll/article/details/154642857?spm=1001.2014.3001.5501

13.導出bit流文件。

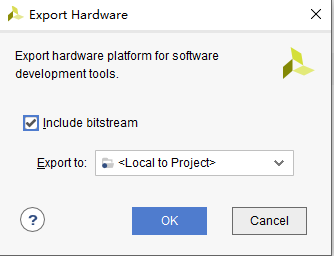

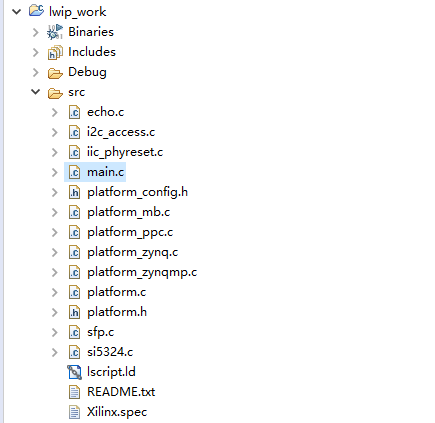

14.打開SDK。若讀者使用vitis,則需要自主創建工程。

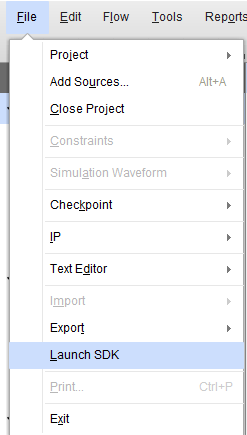

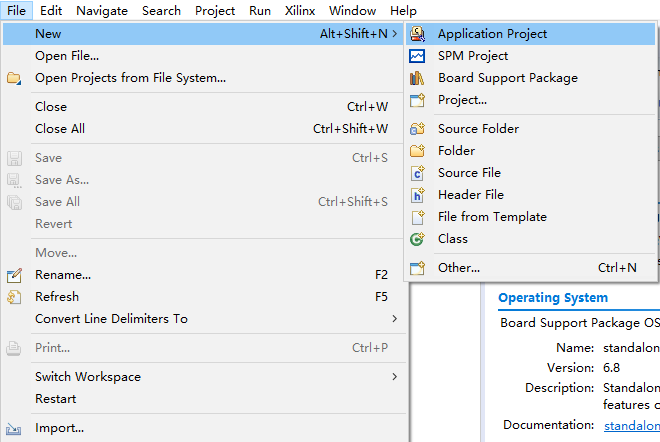

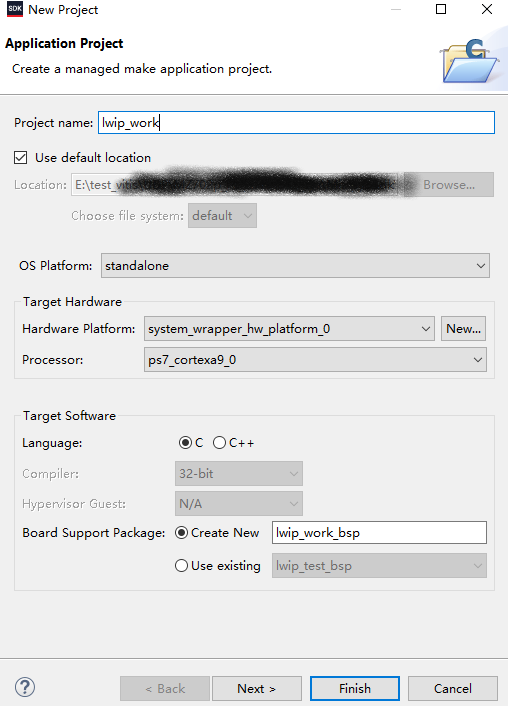

15.新建工程。

16.選擇lwIP Echo Server,點擊finish

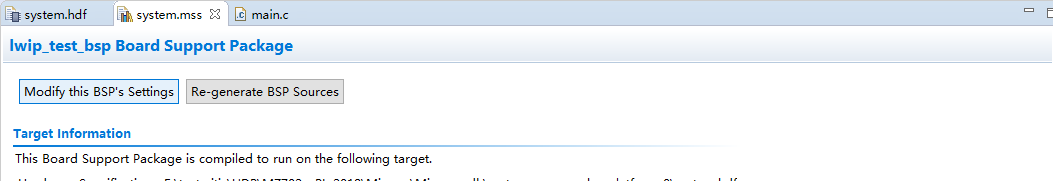

17.此時需要打開bsp setting查看配置。

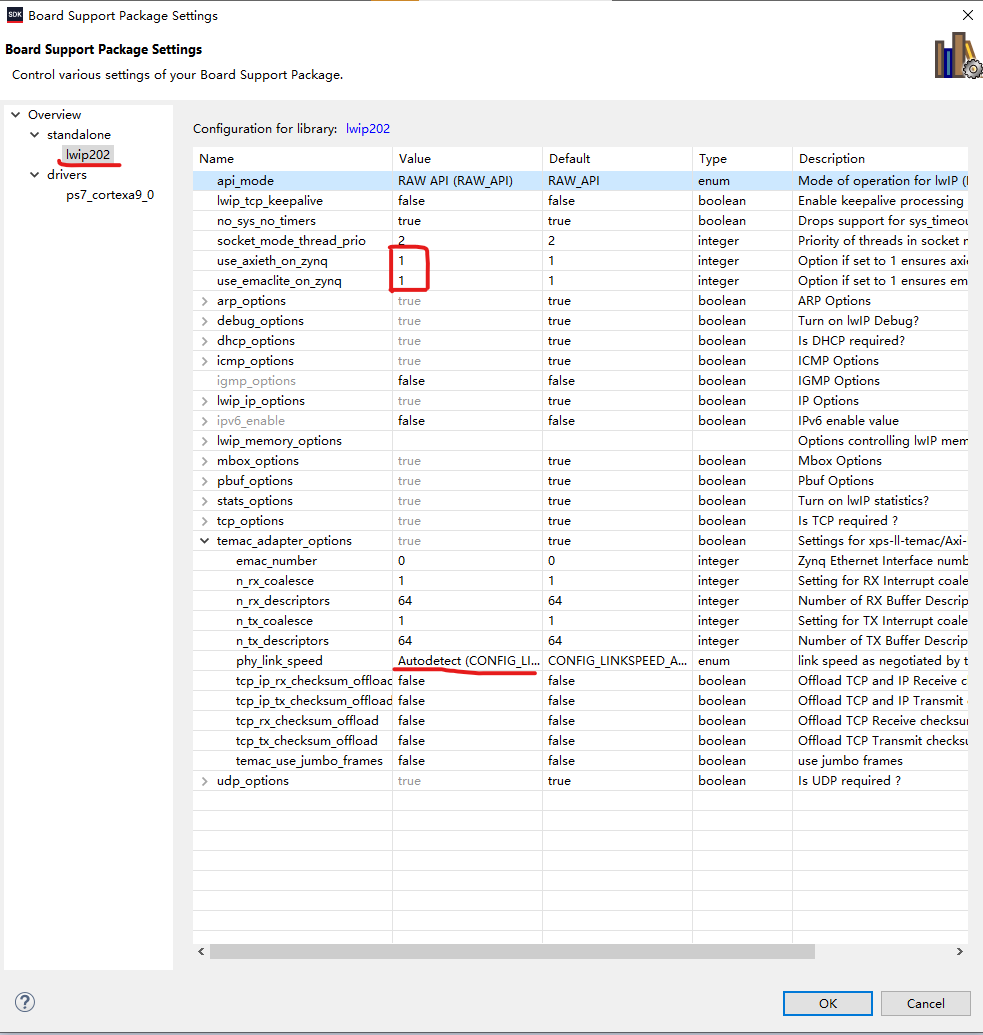

18.上面兩個value需要配置為1,因為是進行pl端擴展的以太網通信實驗。ps端以太網測試則修改為0即可,下方的phy_link_speed需要設置為自動檢測。

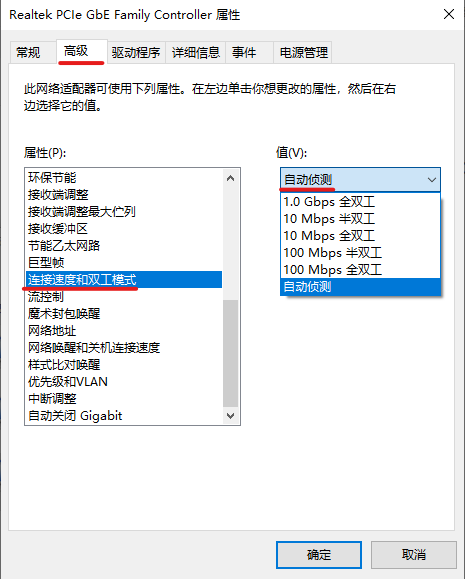

19.phy_link_speed的設置需要與電腦網口配置相同,由于電腦網口配置一般都為自動檢測,讀者也可以自行檢查。

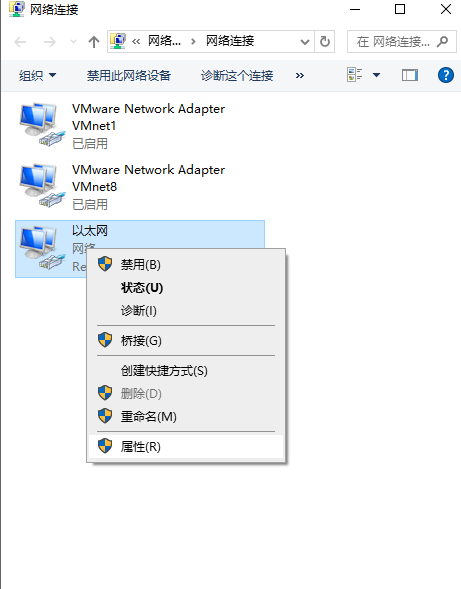

(1)終端搜索 查看網絡連接

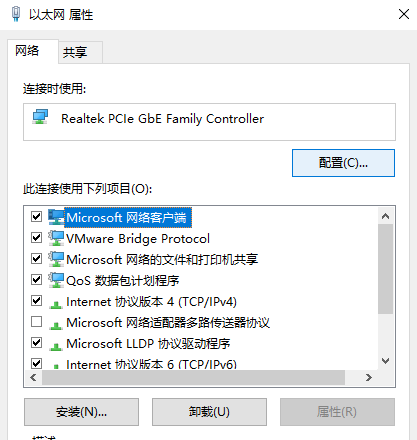

(2)點擊屬性

(3)點擊上方的 配置。

(4)點擊 高級,在下面的屬性中找到 連接速度和雙工模式,右邊查看電腦網口配置。

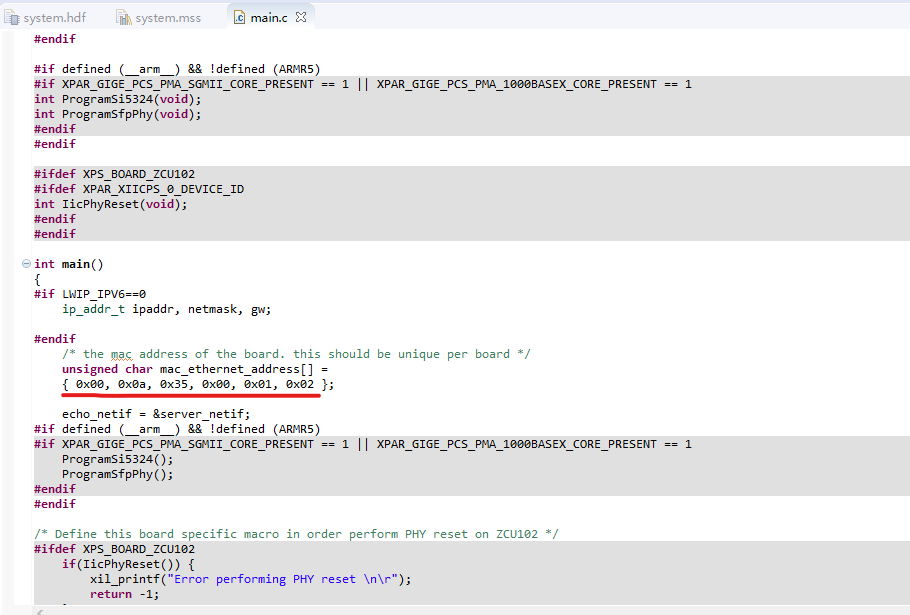

20.在左側文件欄中打開main.c函數,

21.查看sdk自動生成的測試代碼中的mac地址

21.打開cmd,輸入ipconfig,查看局域網內是否有相同的mac地址的設備,若有則需要修改代碼,修改為不同的即可。

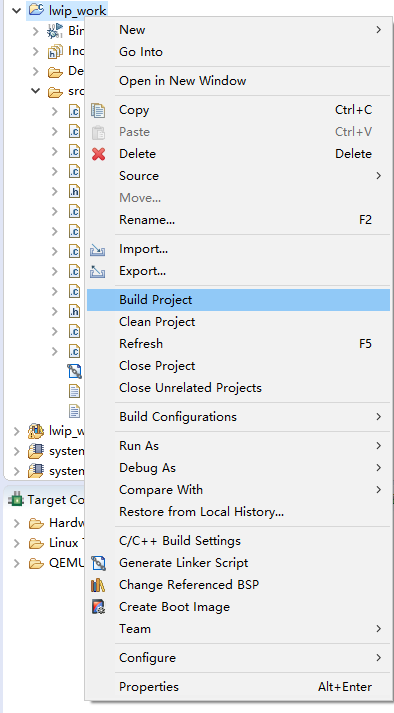

22.進行編譯。

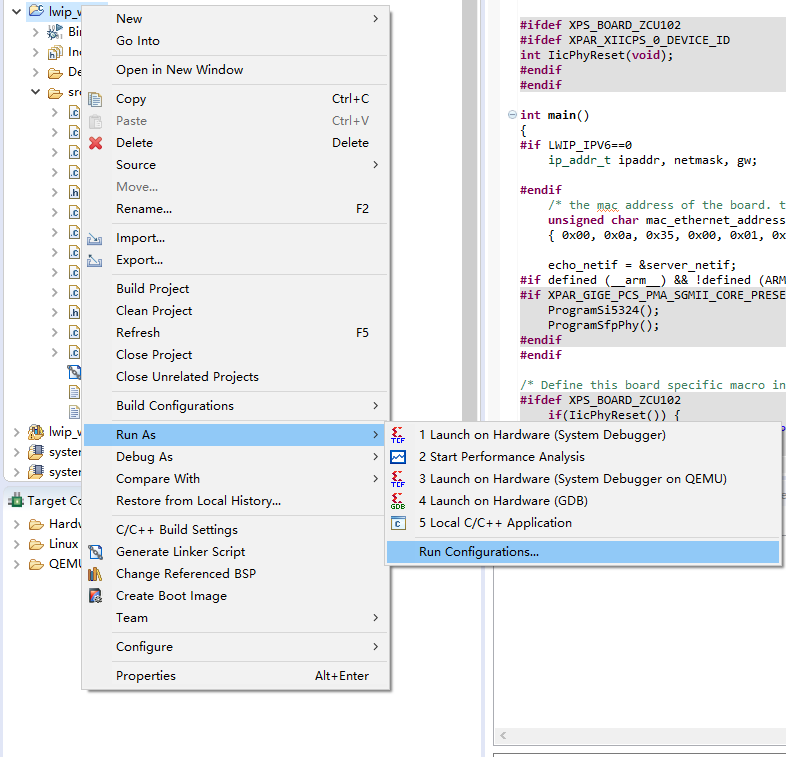

23.sdk需要點擊run configuration進行配置。

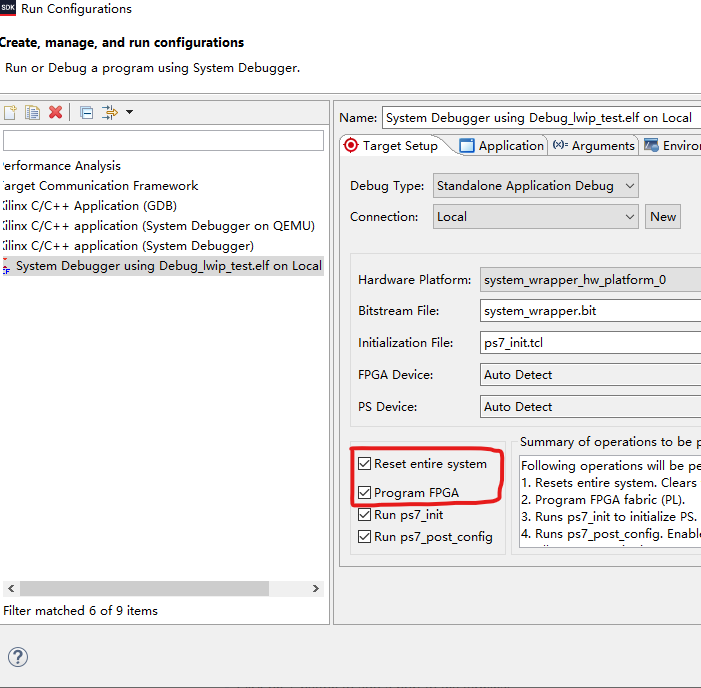

24.進行勾選,勾選后,連接好開發板的電源線,串口線,下載線,以太網的網線。

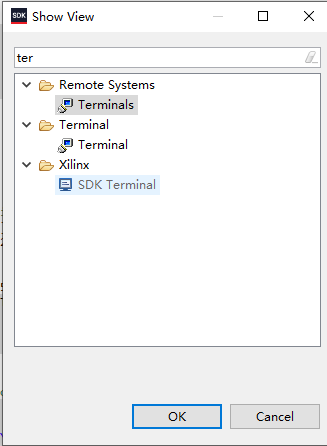

25.打開串口。

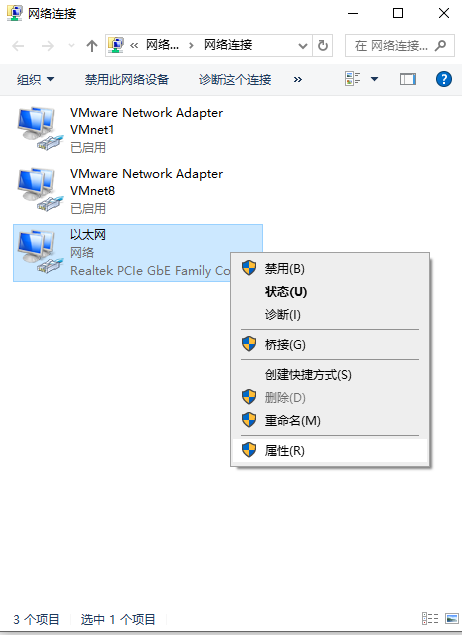

26.配置電腦網址。

點擊屬性。

點擊協議版本4。

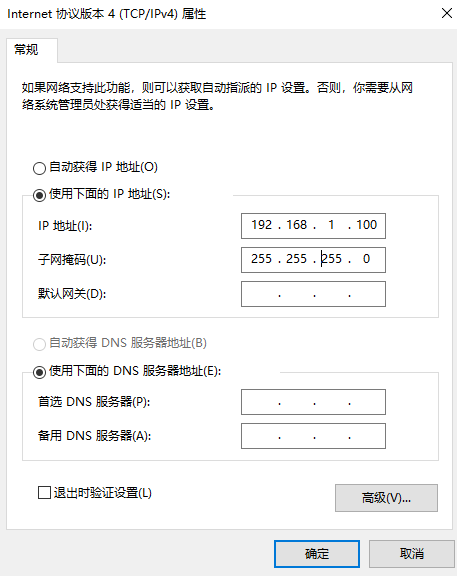

需要配置網址,與開發板網址處于同一ip。

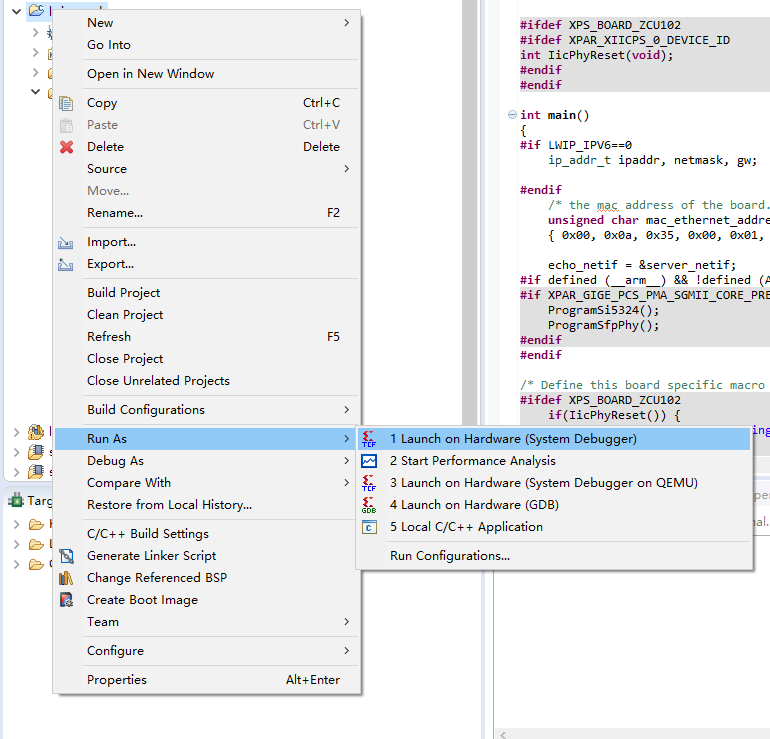

27.燒錄程序。

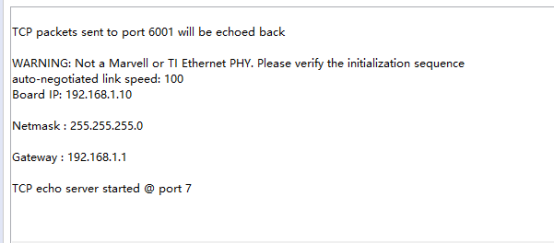

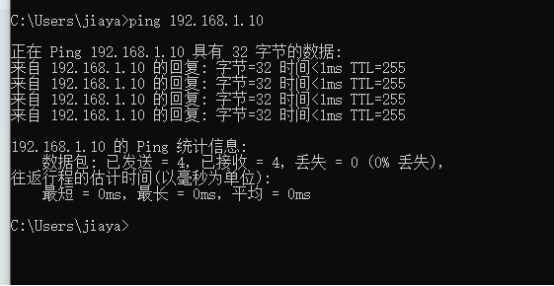

27.此時可以看到串口正常打印出開發板的ip地址,子網掩碼,端口號。然后在終端進行ping連接。

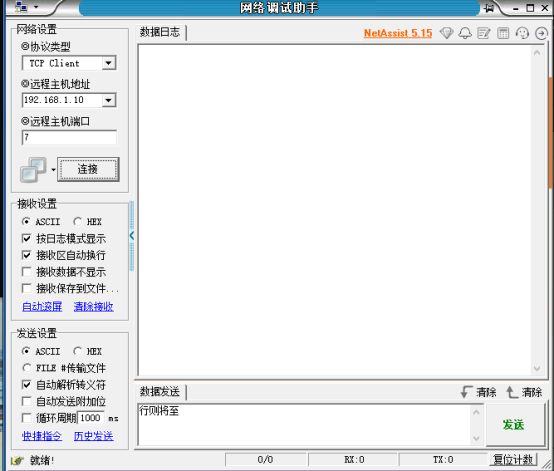

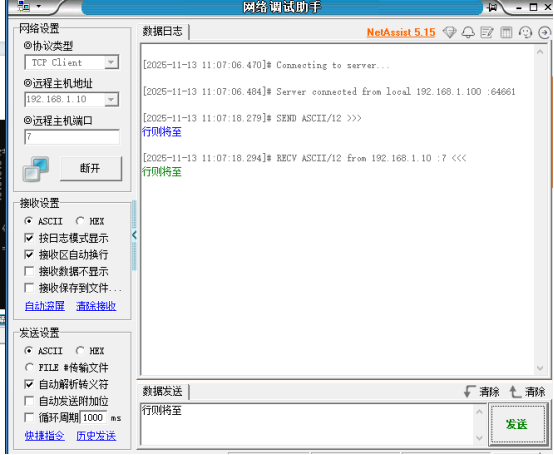

28.打開網絡調試助手,選擇TCP Client,點擊連接。

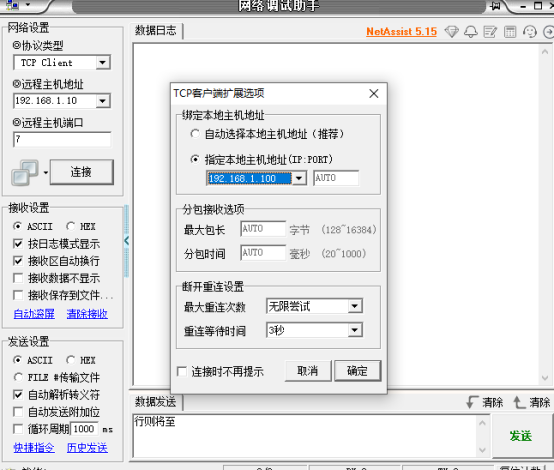

選擇指定本地主機地址,并選擇配置的ip地址,點擊確定。

29.連接成功后,輸入數據,回傳成功,實驗結束。

-

以太網

+關注

關注

41文章

6058瀏覽量

181142 -

通信

+關注

關注

18文章

6409瀏覽量

140115 -

開發板

+關注

關注

26文章

6320瀏覽量

118930 -

Zynq

+關注

關注

10文章

630瀏覽量

49492

原文標題:基于ZYNQ開發板實現以太網通信

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

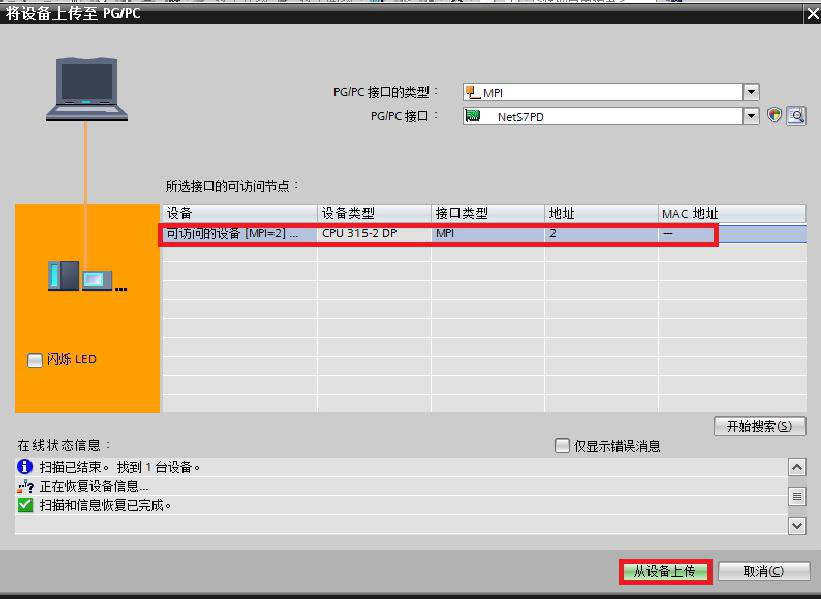

西門子200ppi轉以太網通過CHNet-S7200PD實現以太網通信及ModbusTCP配置方法

西門子300mpi/dp轉以太網通過CHNet-S7300MD實現以太網通信及ModbusTCP配置方法

實現以太網通信硬件電路方法

DE2-115開發板以太網通信問題

請問UDP SOCKET要用操作系統才可以實現以太網通信嗎?

用51單片機控制RTL8029實現以太網通信

單片機實現以太網通訊硬件設計

W5100在單片機實現以太網通信中的應用

S7-200SMART開放以太網通信

如何使用51單片機控制RTL8019AS實現以太網通訊

基于ZYNQ-MZ702P開發板實現以太網通信

基于ZYNQ-MZ702P開發板實現以太網通信

評論