如果對處于全速(at-speed)運行下的FPGA調試,工程師在現有通用“能力技術”基礎上,再增加“硬件斷點”功能,那么對高速運行FPGA,也就擁有像調試軟件程序類似的完整可觀測能力(Full Visibility)和可控制能力(Controllability)。

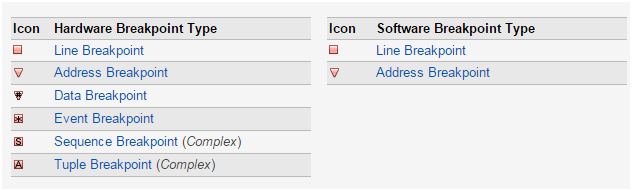

以賽靈思FPGA的應用開發為例,用戶已經能從硬件的運行特征出發,為設計增加兩類硬件斷點。除了前文所介紹的時鐘斷點功能,本文將詳細介紹事件斷點(Event-based Breakpoint)的集成和使用。

與適用于算法設計、接口控制等全同步設計的時鐘斷點相比,事件斷點是由用戶自定義的事件觸發信號來凍結時鐘,即以“事件發生的次數”為中斷地址。適用于對包含UART、以太網等通信接口在內,較復雜的FPGA應用開發設計。

例如,在網絡處理系統中,可將“數據包接收/發送”作為事件斷點;在數據加密處理應用中,將“一個數據塊處理結束”作為事件觸發信號。

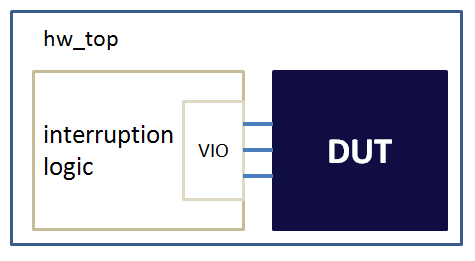

用戶在設計階段,與前文介紹的時鐘斷點類似,事先將硬件斷點控制模塊(interruption logic)集成到待測DUT的頂層(hw_top),就可獲得這樣的在線調試能力。

本文將以按圖索驥的方式,詳細介紹在設計中集成事件斷點的實現過程,對原有設計的改動非常小,仍然保持優異的時序性能。

以下為正文

1. 樣例簡要介紹

uart-demo作為串口數據傳輸樣例,用于控制uart串口數據的發送,以及led輸出。

通信協議設置為“9600 bps,8位數據位,沒有校驗位、1位停止位”。

源碼獲取地址:https://gitee.com/forgeda/forgedaX-35T/tree/master/demo/vivado-uart/Source

2. 事件斷點控制模塊

模塊定義如下:

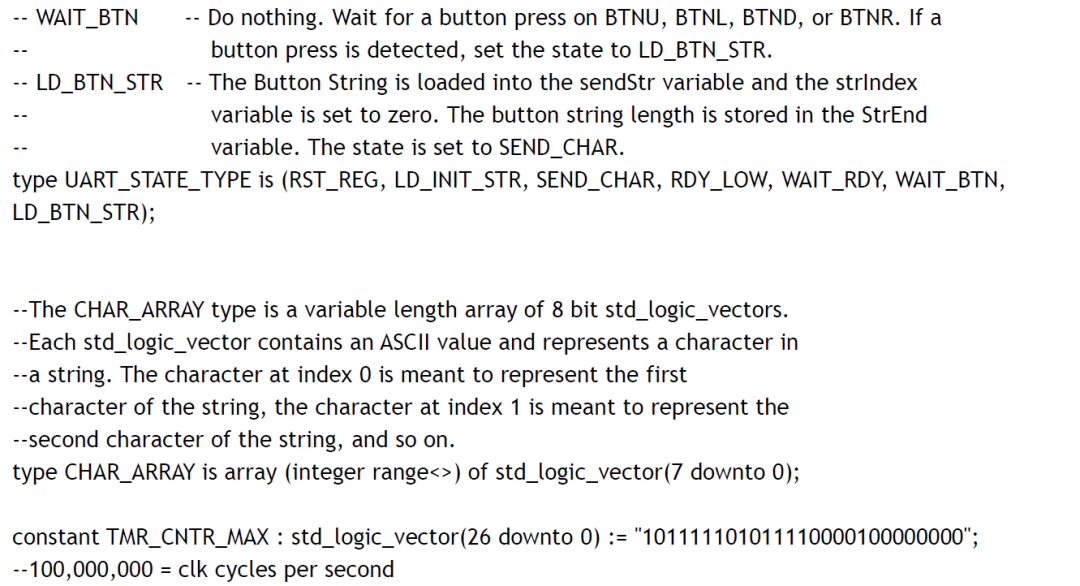

moduleinterruption_logic( (* dont_touch ="true"*)outputreg[63:0] cycles, inputsig_in, inputsys_clk,inputsys_reset,outputtask_clk );wireclk_en;wire[63:0] breakpoint; reg[63:0] counter; regbreak; il_vio_0 il_vio ( .clk(sys_clk), .probe_in0(counter), .probe_in1(cycles), .probe_out0(breakpoint), .probe_out1(clk_en) );always@(posedgesys_clk)beginif(!sys_reset)begincounter <=?0;break?<=?0;endelseif?(clk_en)beginif?(counter == breakpoint)beginbreak?<=?1'b1;endelsebeginif?(sig_in) counter <= counter +?1;break?<=?1'b0;endendend? BUFGCE inst_bufgce (.O(task_clk),.I(sys_clk),.CE(clk_en & ~break) ); always?@(posedge?task_clk) ? ?beginif?(!sys_reset) ? ? ? ? ?begin? ? ? ? ? ? ?cycles <=?0; ? ? ? ?endelsebegin? ? ? ? ? ? ?cycles <= cycles +?1; ? ? ? ?endendendmodule

該模塊非常精簡,對您的原生設計的改動很小,所占用的硬件資源也很少。

3. 將事件斷點模塊集成到設計中

在原有設計中集成事件斷點控制模塊,全程在Xilinx Vivado環境下完成,共有以下四個步驟。

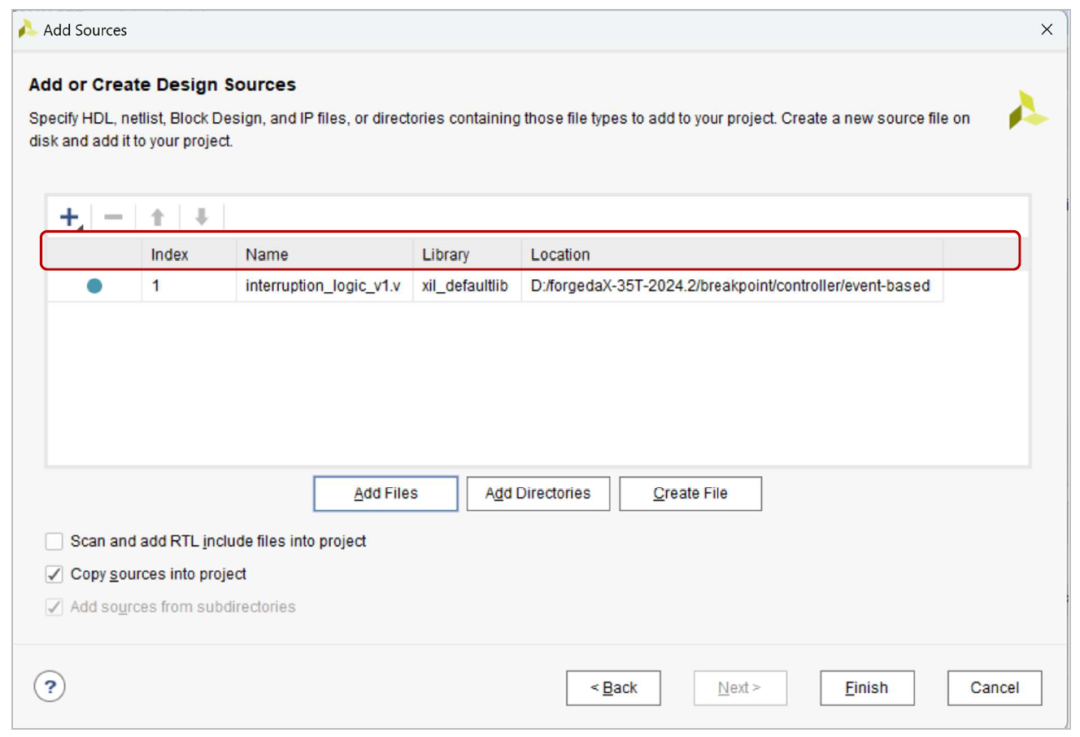

Step 1.導入控制模塊interruption logic,并對VIO進行參數設置

單擊“Finish”,確認導入該模塊文件。

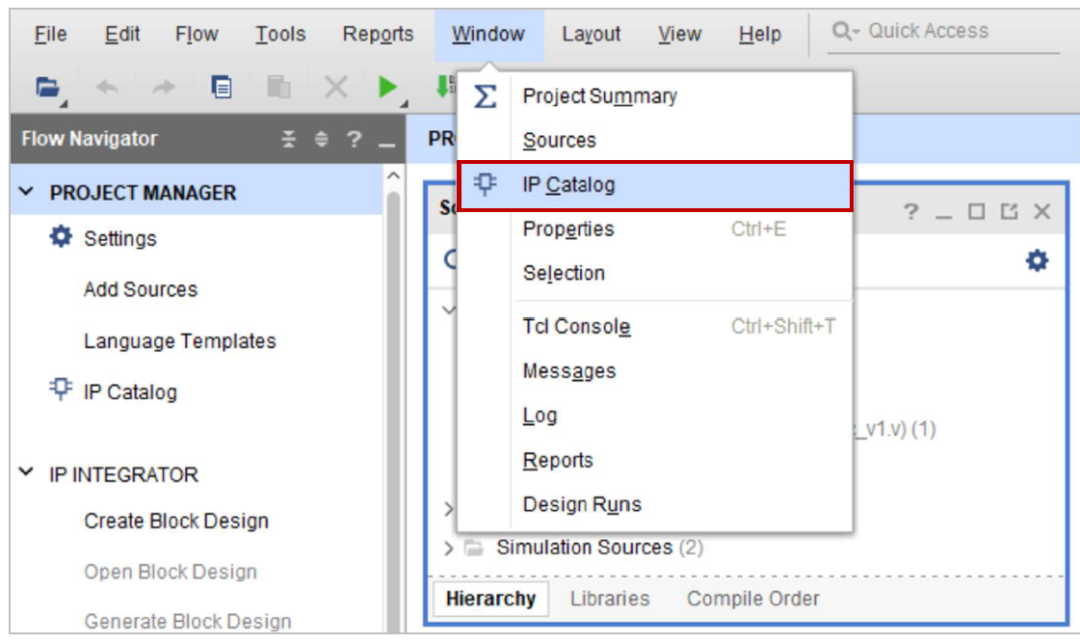

導入斷點控制模塊所使用的VIO IP核

在Vivado中,選擇“IP Catalog”,導入VIO IP核。

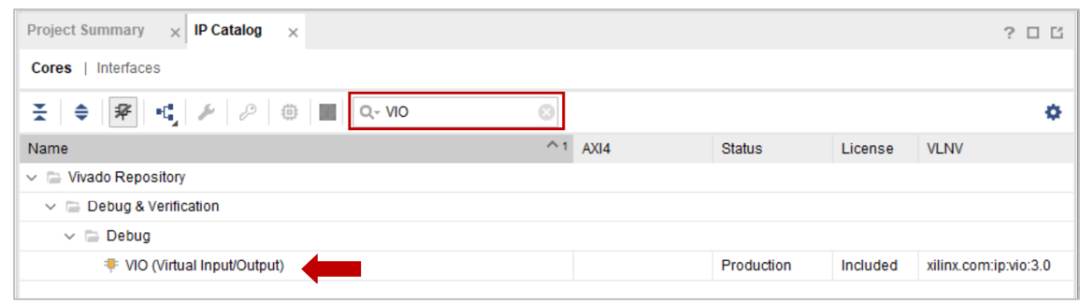

在IP Catalog搜索框中,直接輸入VIO,顯示如下:

設置VIO IP核的輸出端口(PROBE_OUT0),設置事件斷點的初始地址。

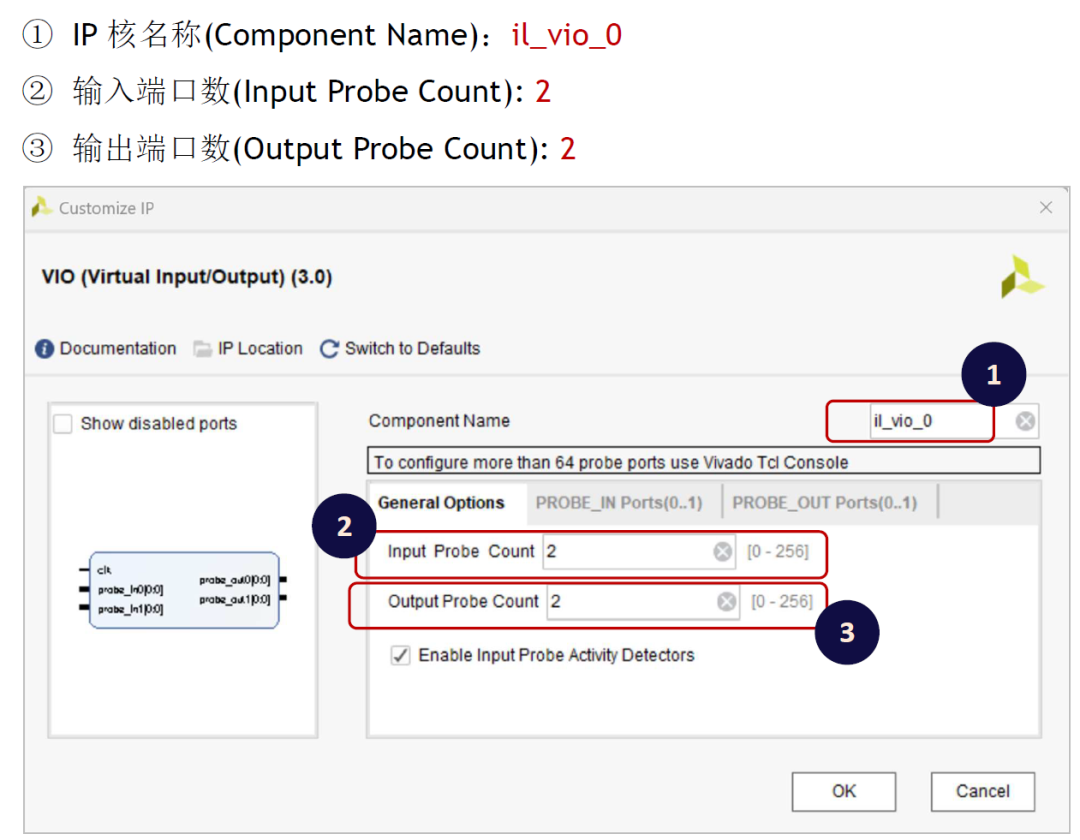

在Customize IP核界面,對VIO IP進行參數設置:

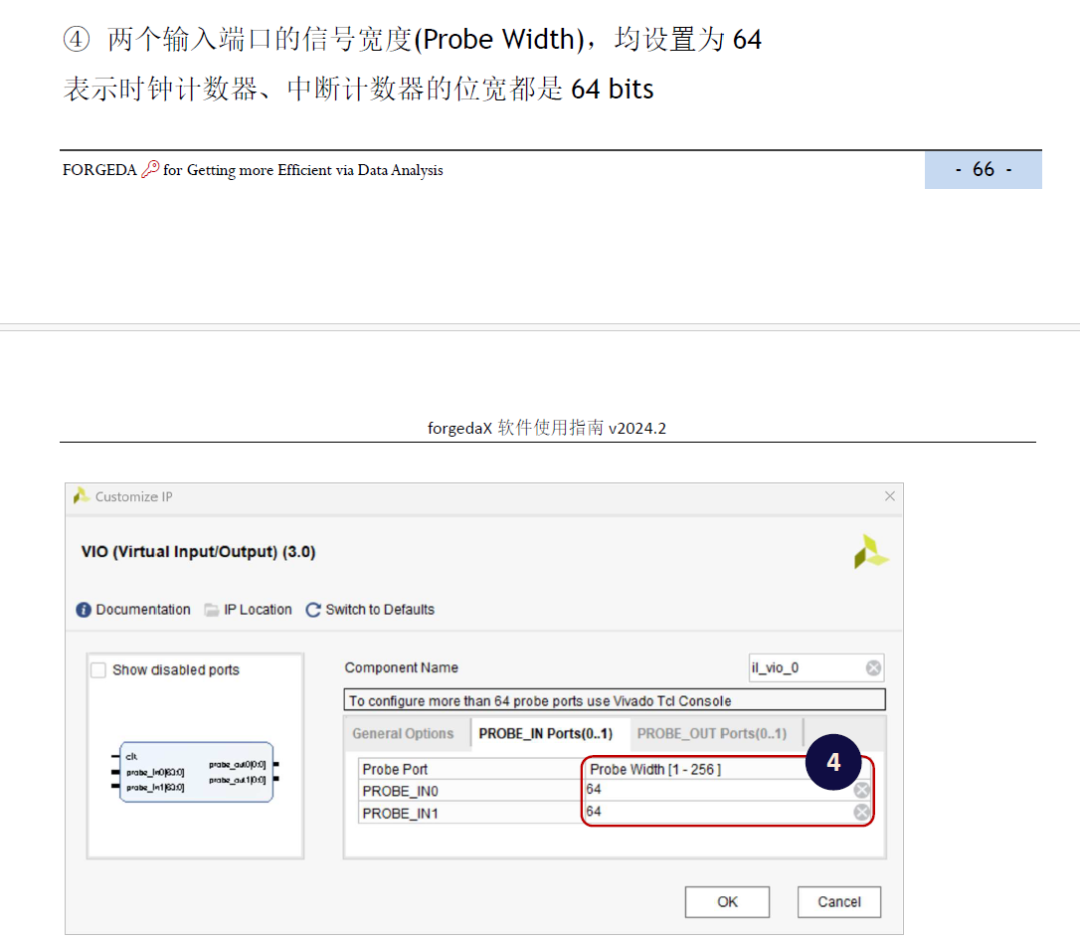

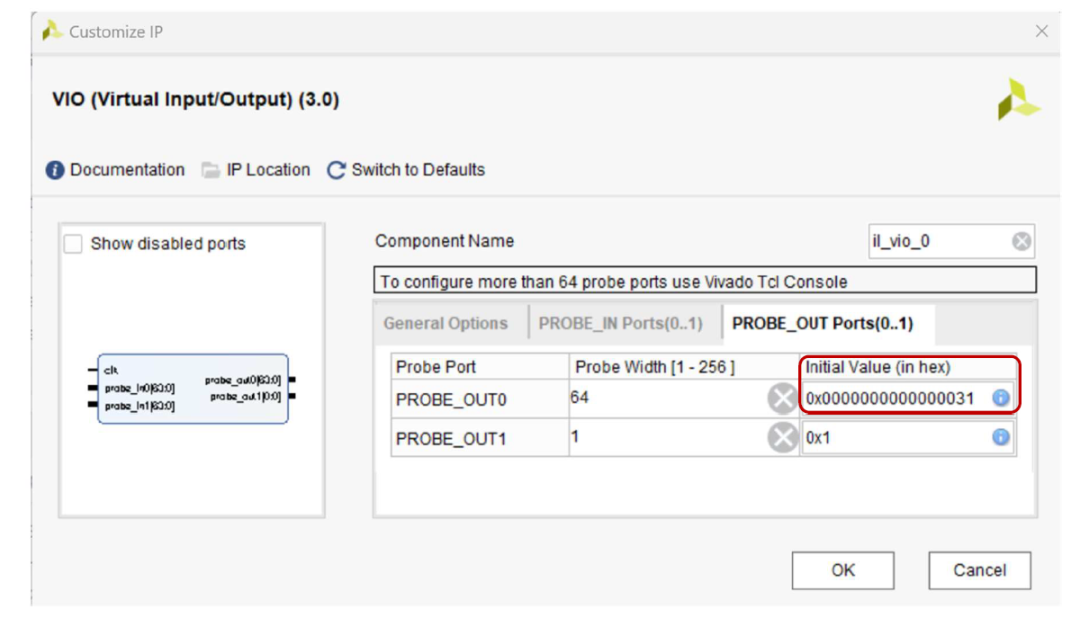

接下來,設置兩個關鍵輸出端口的參數:

事件斷點的初始地址(PROBE_OUT0)

信號位寬Probe Width [1-256]:64;

初始值Initial Value (in hex):0x31

即該樣例在位流載入完成之后,在運行階段遇到的首個斷點地址。

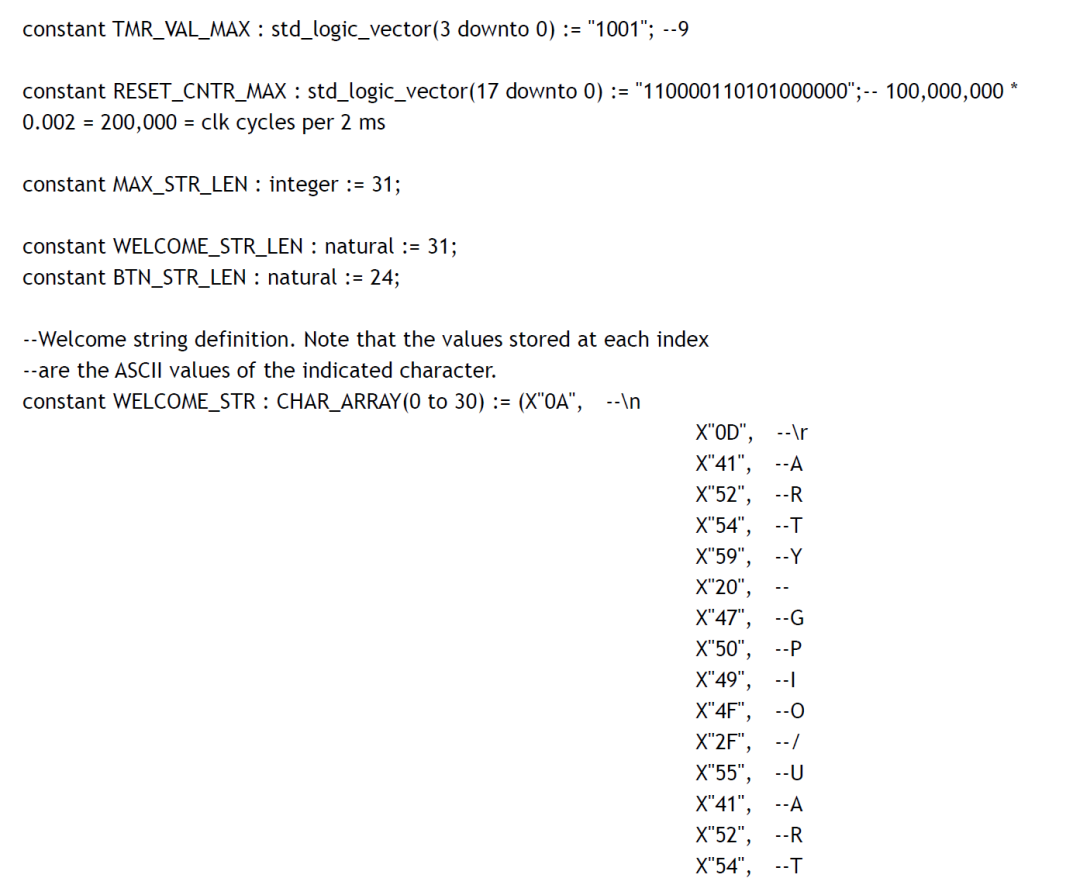

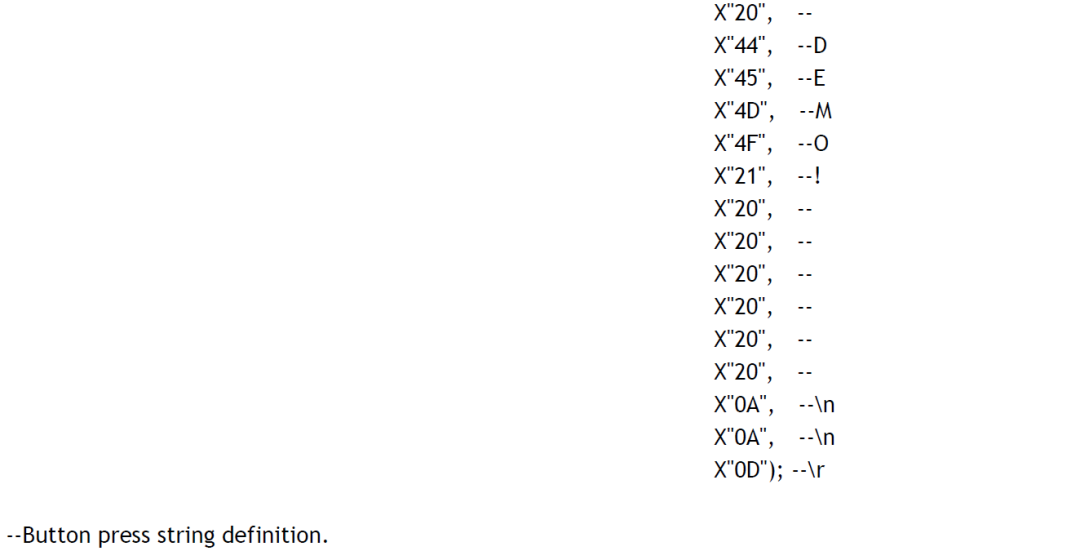

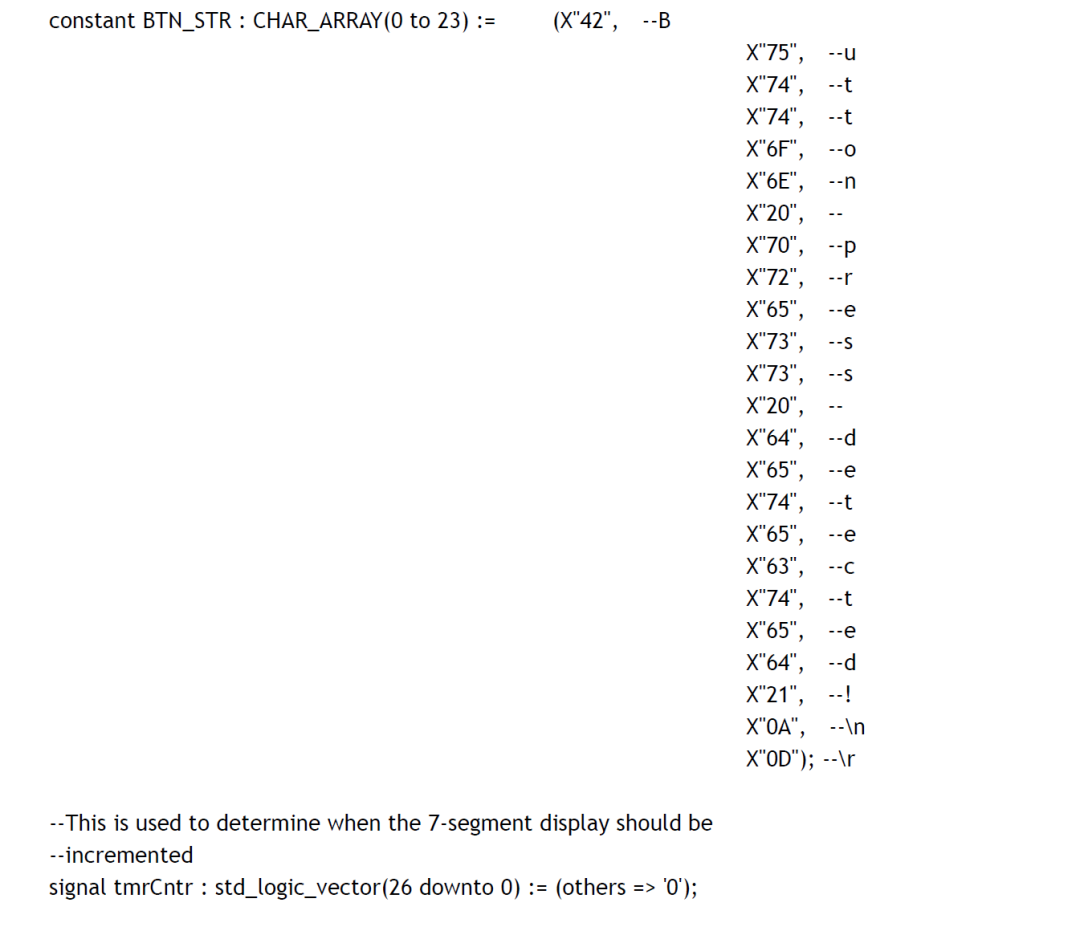

在本樣例中,UART端口在板卡上電后,直接輸出“ ARTY GPIO/UART DEMO! ”消息,我們選擇將UART設計中的“bit_done”作為中斷觸發信號,表示“串口已發送1 bit數據”。

換而言之,當事件斷點設置為0x31,表示設計將在傳輸49 bit,即傳輸第五個字符“T”的停止位時,暫停運行。

時鐘使能信號(PROBE_OUT1)

信號位寬Probe Width [1-256]:1;

初始值Initial Value (in hex):0x1

初始值設置為1,表示開啟時鐘使能。

點擊“OK”,確認以上參數配置。

點擊“Generate”,生成VIO IP核。

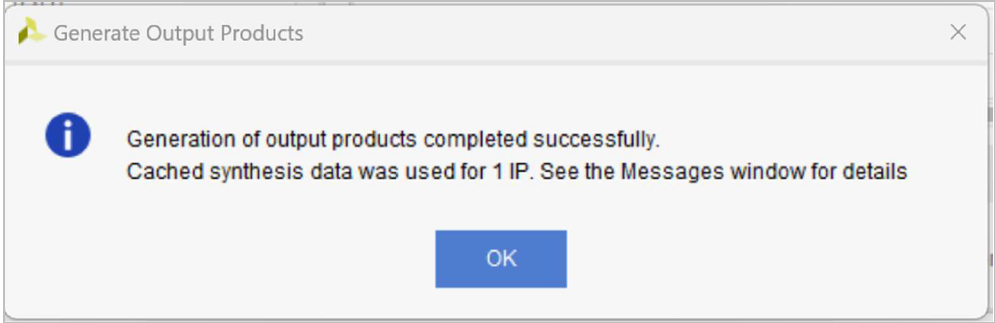

顯示“Generation of output products completed successfully”消息,表示IP核已成功導入。

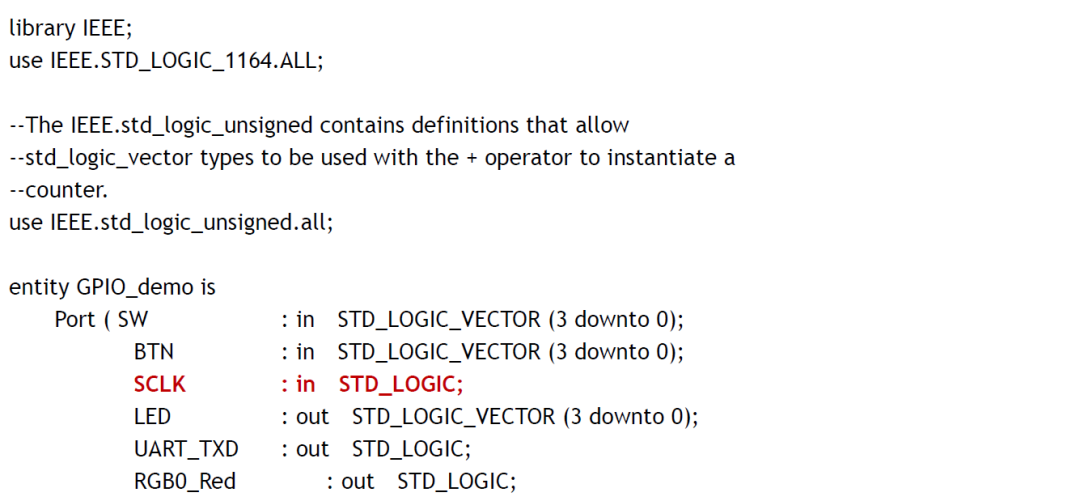

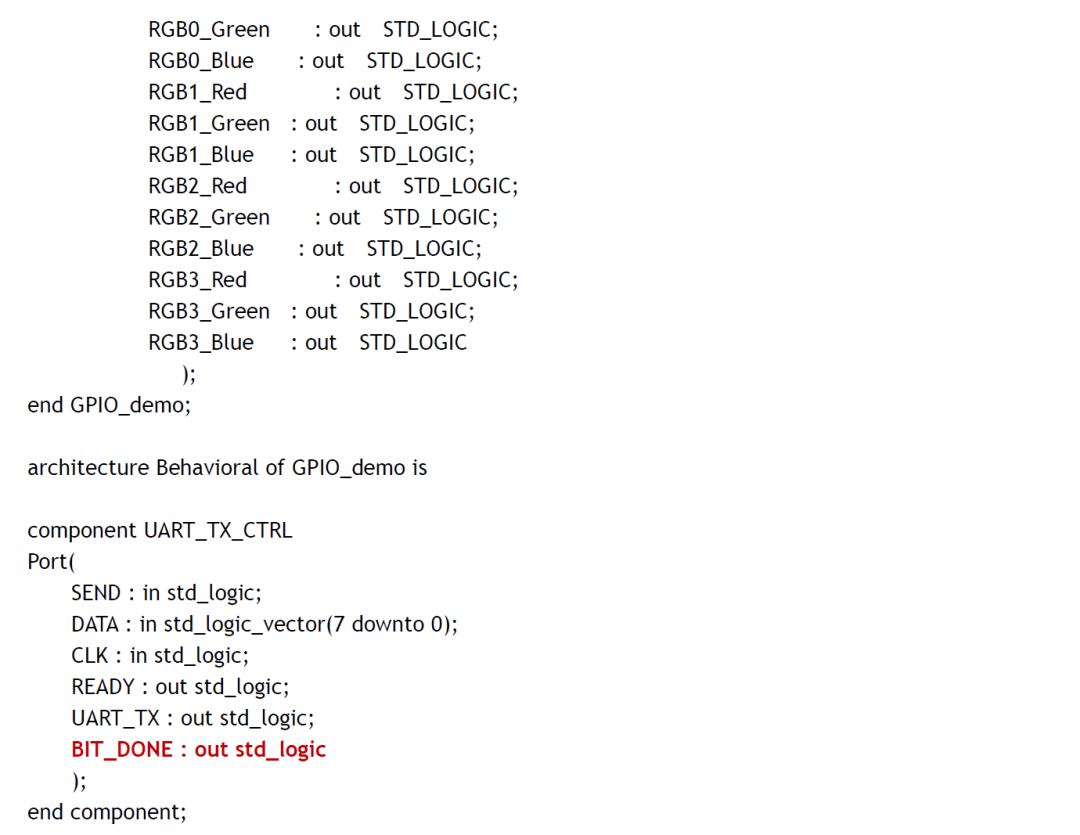

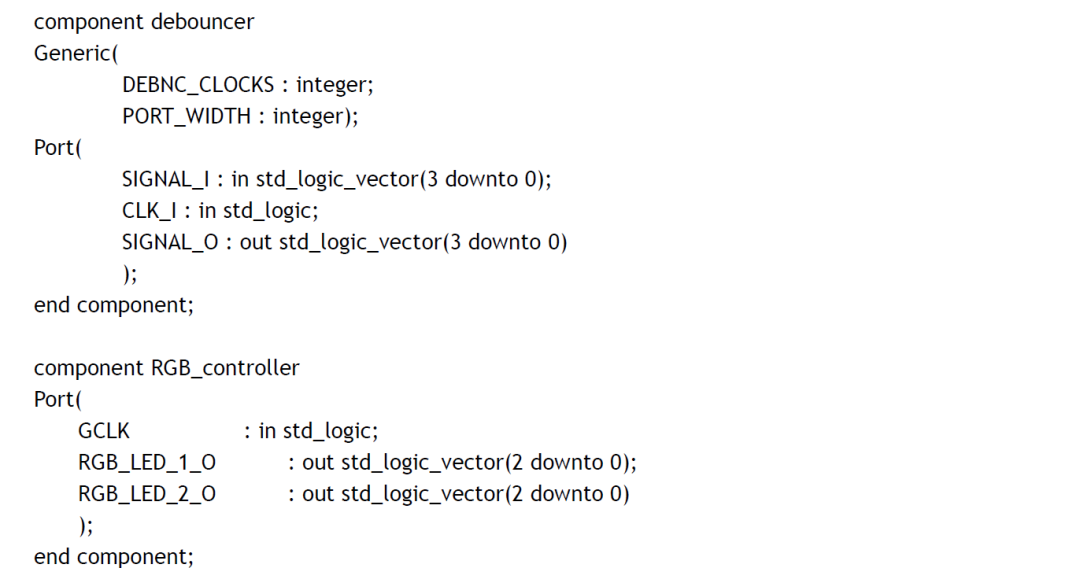

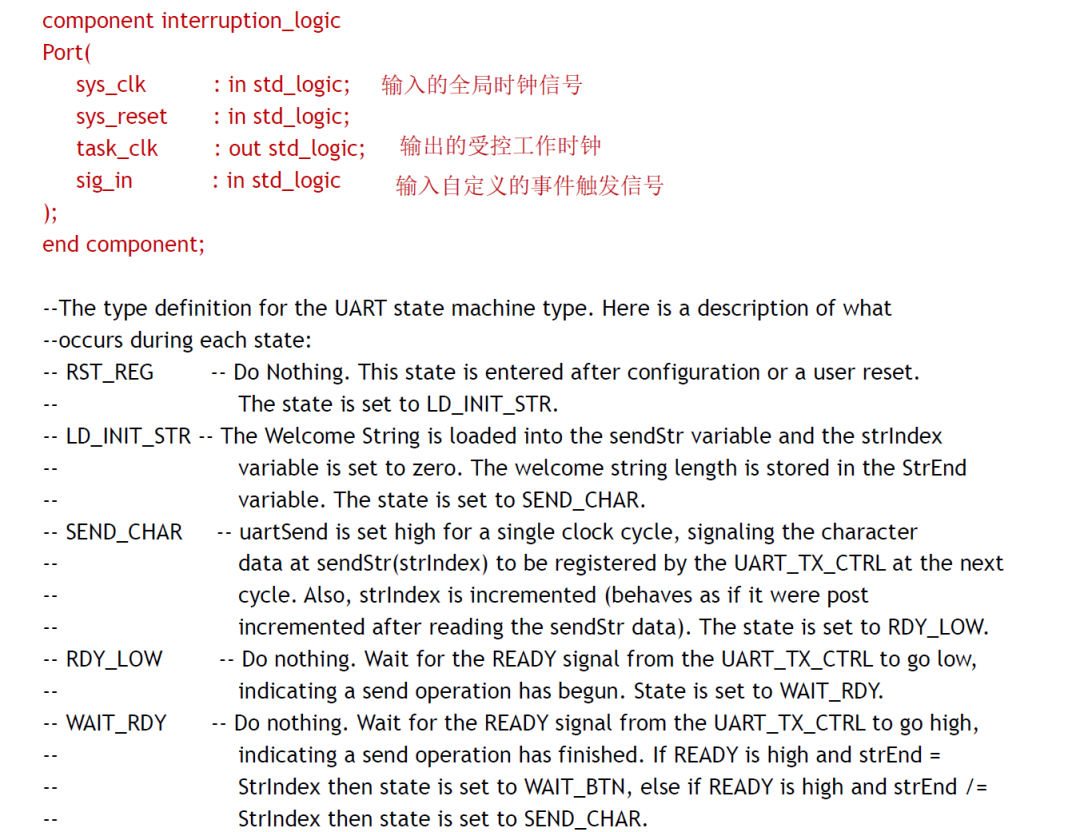

Step 2. 對設計頂層(hw_top)進行更改處理

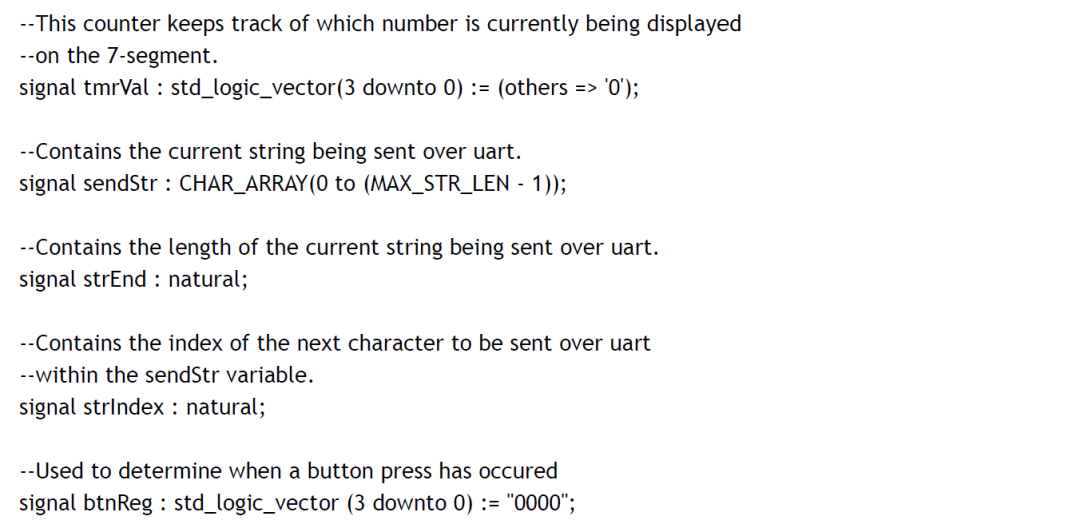

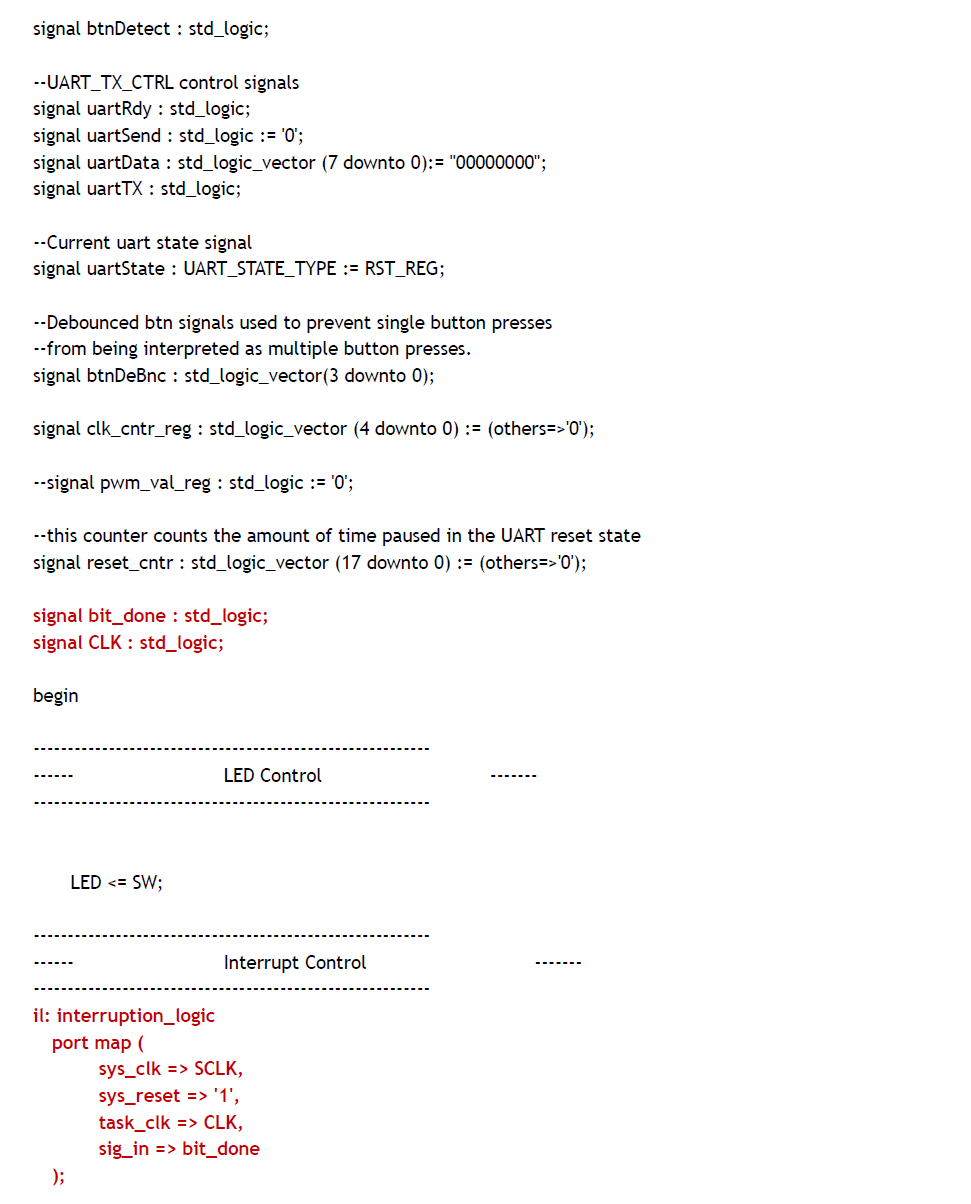

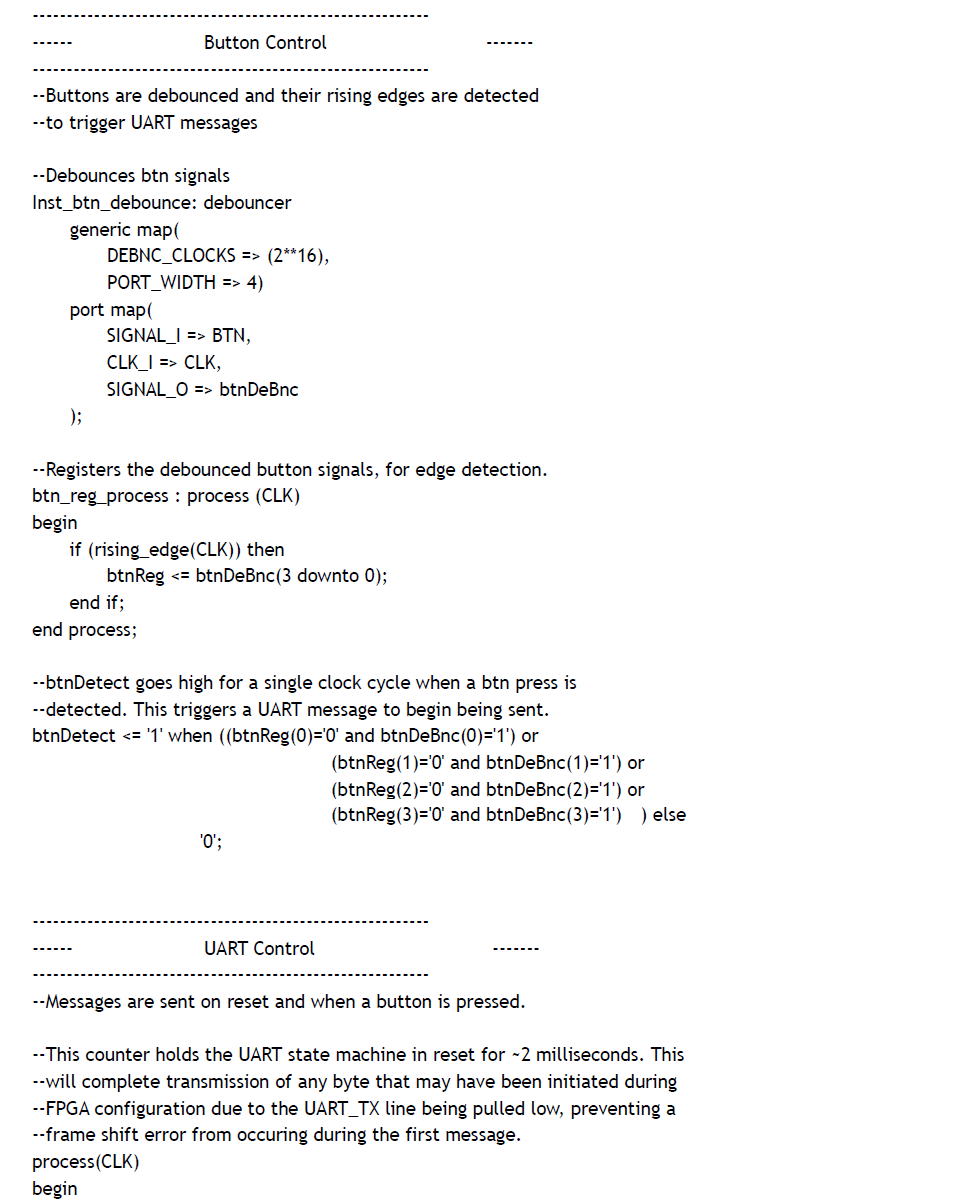

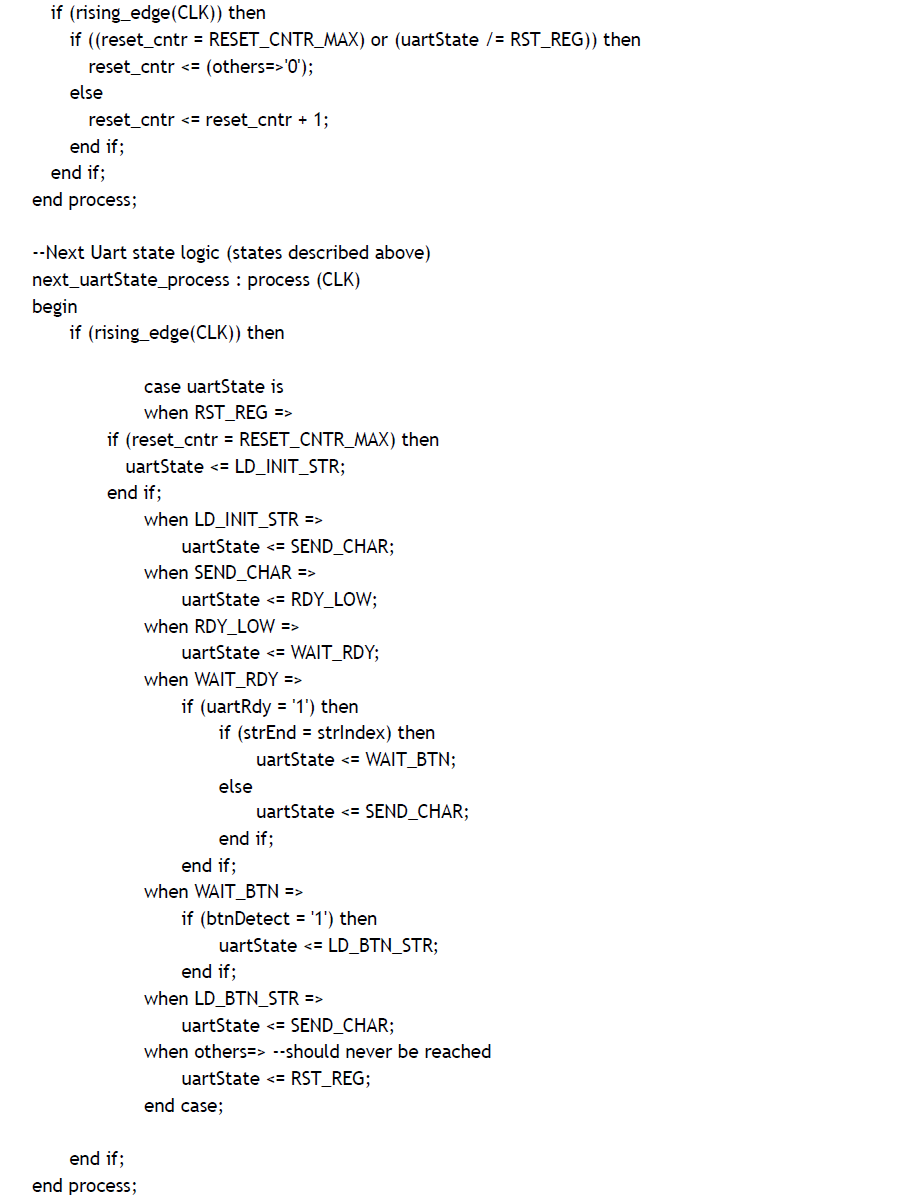

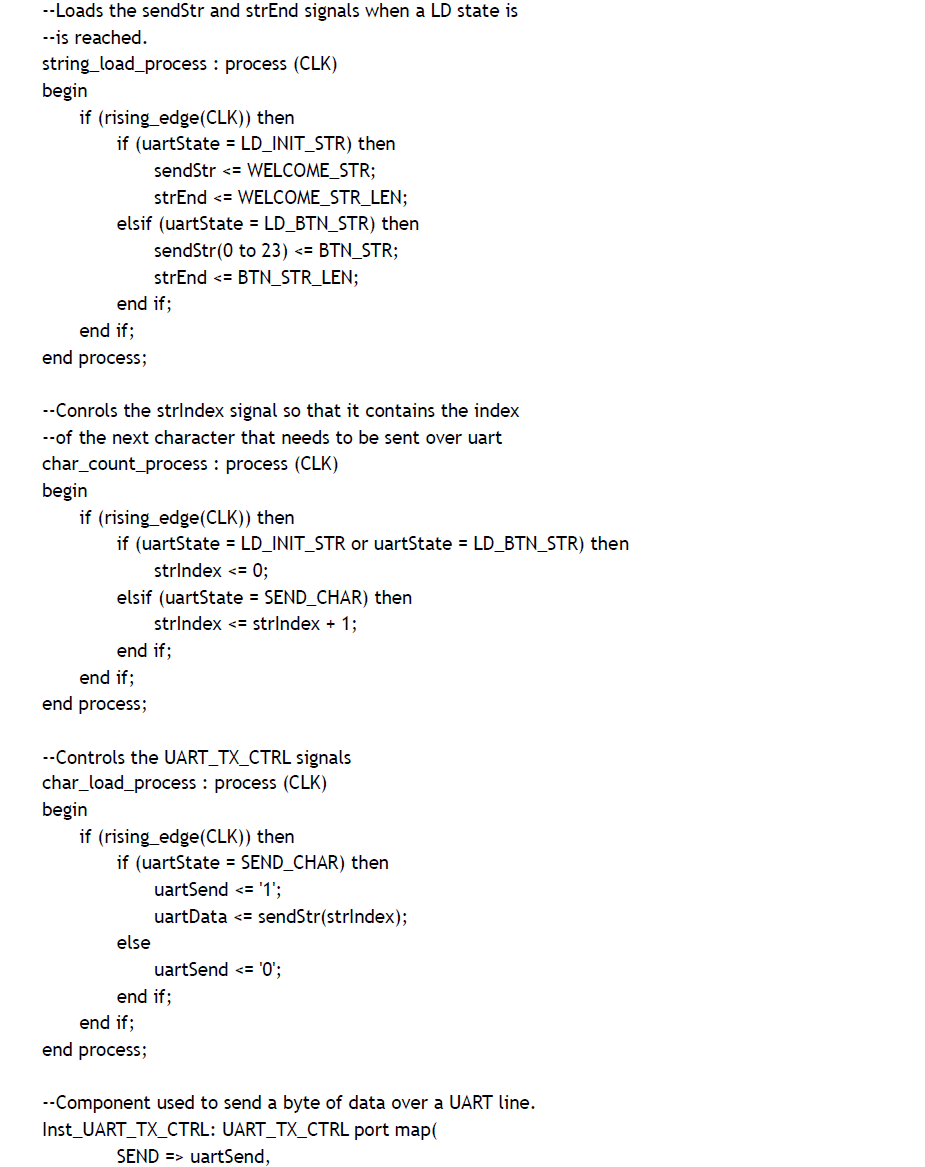

以下為集成事件斷點模塊后的設計頂層,原有設計的改動部分已用紅色標記。

集成斷點控制模塊之后的Vivado工程文件,詳見

https://gitee.com/forgeda/forgedaX-35T/tree/master/demo/vivado_uart_event_bp/uart_breakpoint

Step 3.重新啟動Vivado編譯過程

啟動Vivado編譯,生成新的設計結果文件(.dcp), 得到的配置位流文件top.bit,以及調試支撐文件debug_nets.ltx。

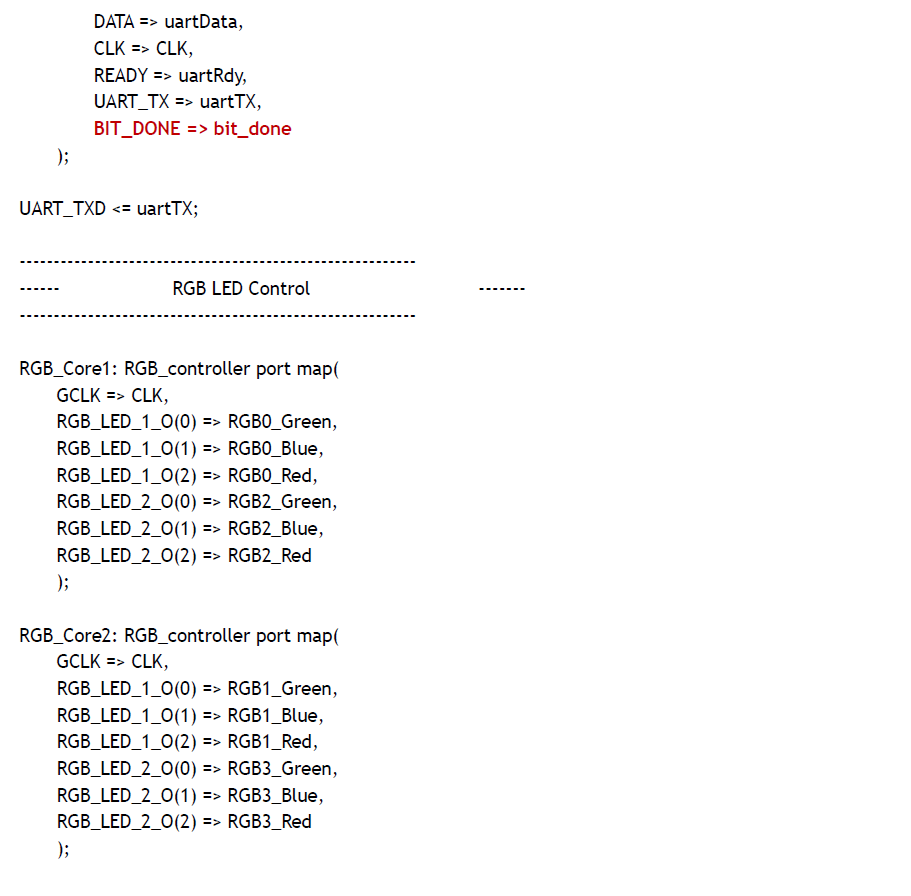

完成以上工作后,就可以直接下載運行,并通過Hardware Manager,自行驗證以上集成過程是否已經正確無誤。

4. 自檢方法

您可直接在Vivado Hardware Manager中快速驗證,具體步驟如下:

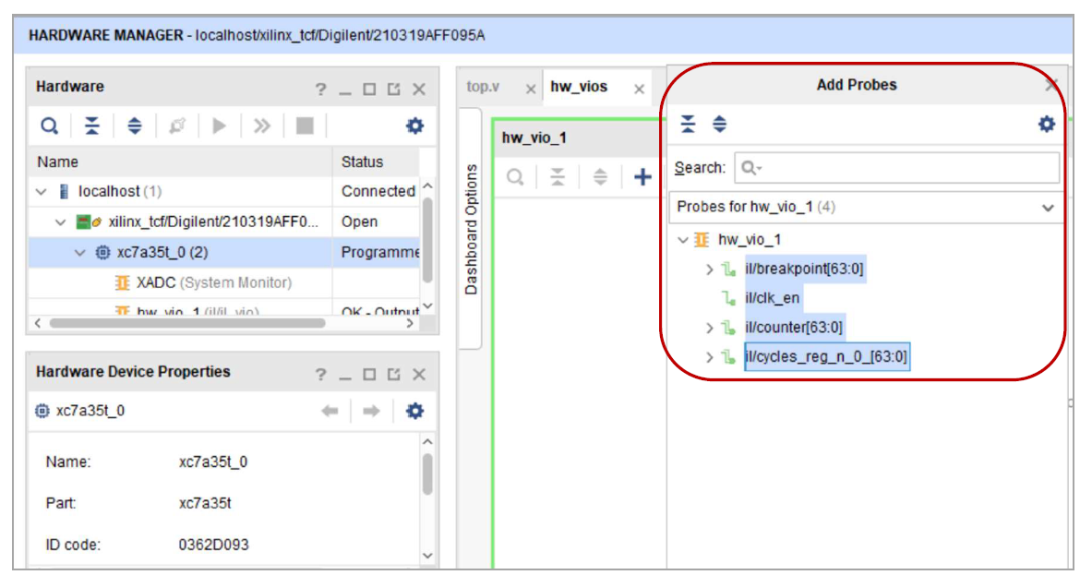

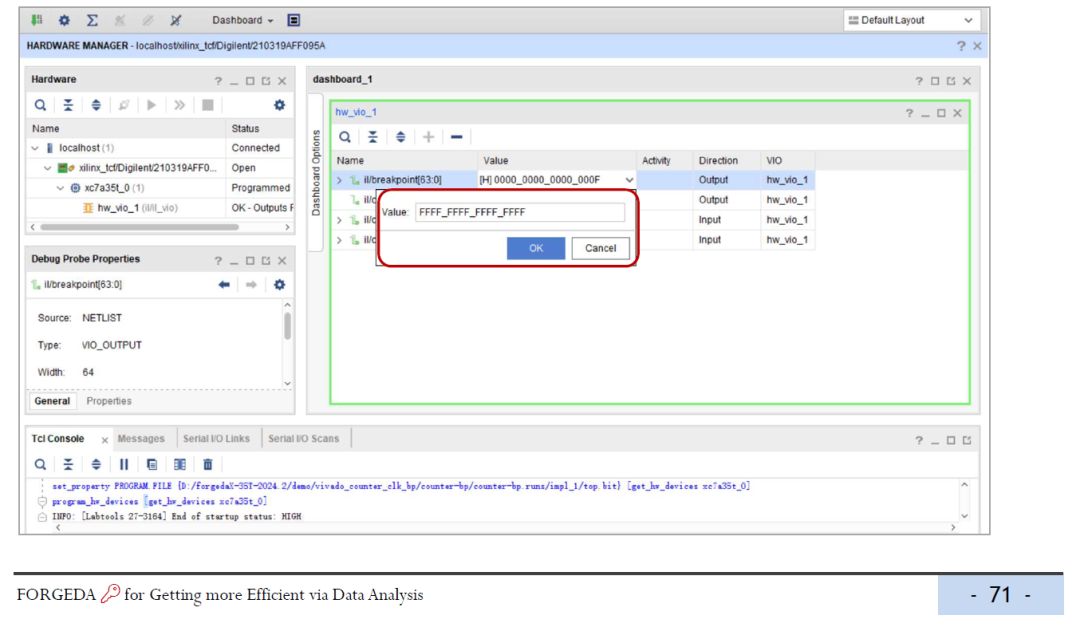

如下圖所示,樣例在初始化結束后,輸出字符“ART”之后暫停運行,該斷點地址即為Step 2 設置的0x31。

可繼續在VIO窗口,設置新的斷點地址,例如,輸入“0x3B”,表示設計將在傳輸59 bit,即第六個字符“Y”發送結束時,暫停運行。

最后,將斷點地址設置為FFFF_FFFF_FFFF_FFFF,清除斷點,如下圖所示。

樣例將繼續全速運行,輸出完整的“ARTY GPIO/UART DEMO! ”消息。

在前文的時鐘斷點、本文的事件斷點這兩個硬件斷點準備工作后,下一篇我們將介紹如何在板級在線調試過程中,無需在源碼、網表插探針,在不占用任何硬件資源,就可得FPGA運行狀態的全可觀測能力,對設計擁有100%的信號可見性,這是ILA、Chipscope等現有工具不能提供的功能;

以及RTL代碼在經過硬件編譯后,信號名稱可能會被優化改變,那么如何在源碼和調試信號(位流數據)之間建立精準對應關系,大幅減少工程師的硬件經驗成本;

-

FPGA

+關注

關注

1662文章

22448瀏覽量

637605 -

硬件

+關注

關注

12文章

3603瀏覽量

69085 -

時鐘

+關注

關注

11文章

1993瀏覽量

135117

原文標題:如何將FPGA設計驗證效率提升

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA在線配置模塊和自動測試模塊實現過程

在FPGA體系結構能夠實現的并行運算

如何使用嵌入式Jetty容器在Jersey中集成Webapp應用

在FPGA中集成ARM核的話可以做些什么事情

FPGA,FPGA工作原理是什么?

一個FPGA中現在可集成多少32位RISC處理器?

在FPGA設計中集成事件斷點的實現過程

在FPGA設計中集成事件斷點的實現過程

評論