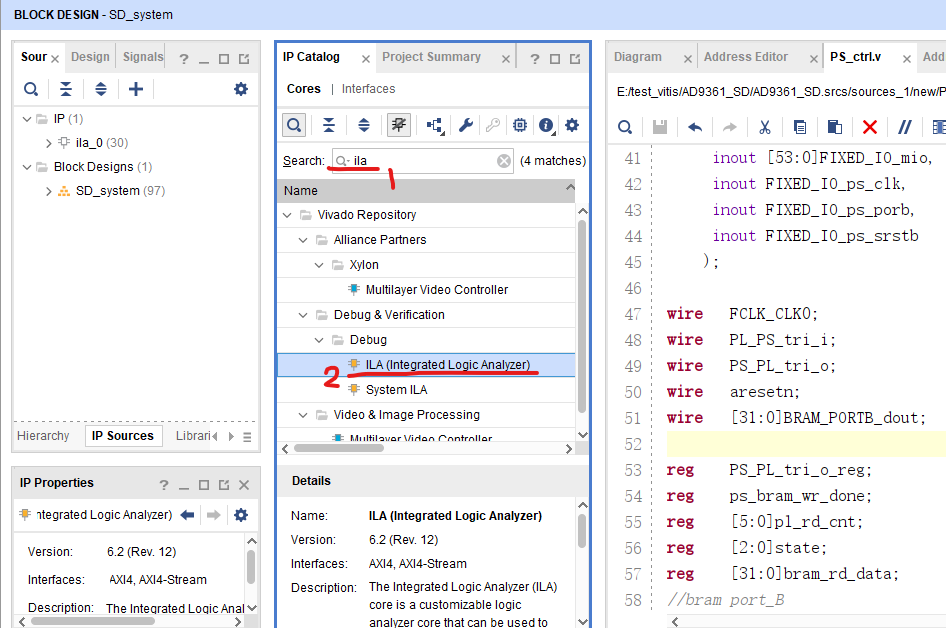

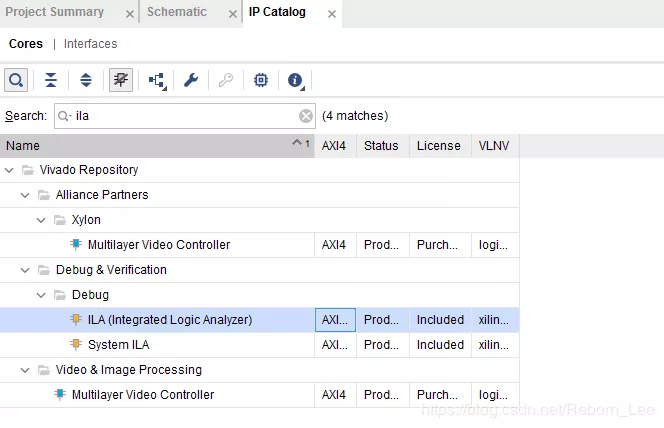

在vivado頁面中搜索ila IP核,然后雙擊打開。

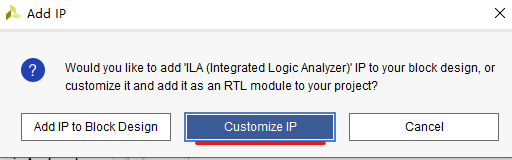

點擊中間這個。

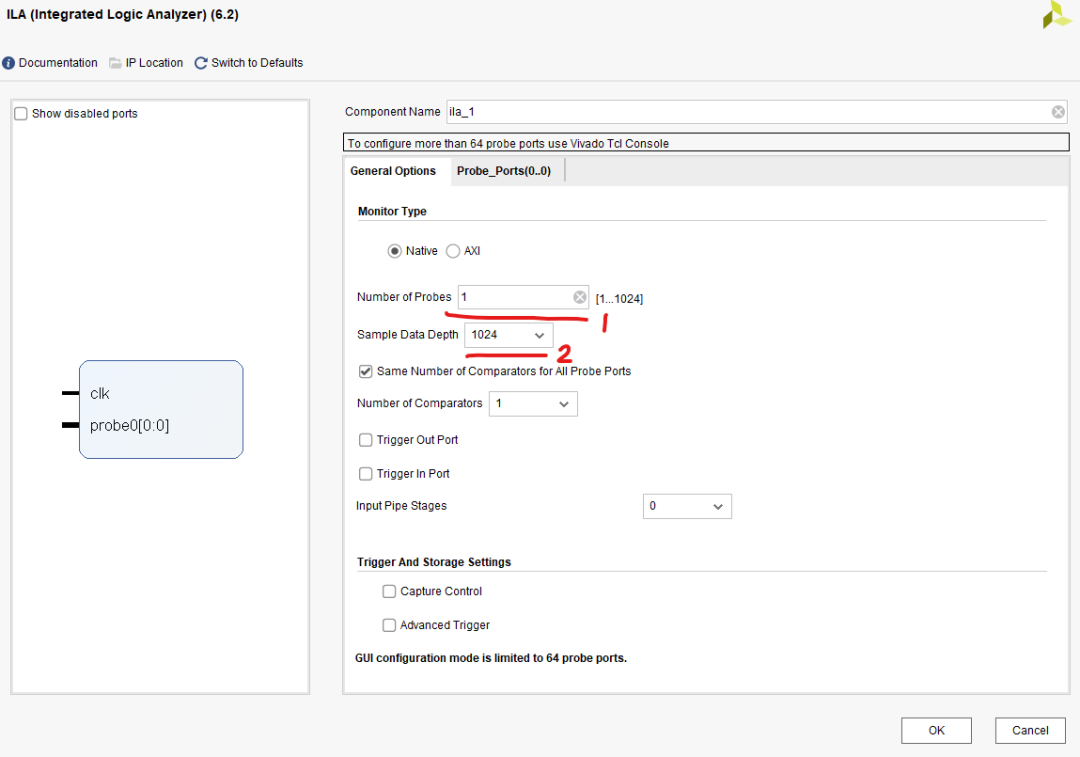

其中1是添加幾個觀察信號,2是采樣深度。1根據自己要觀察的信號進行選擇,2一般越大越好。

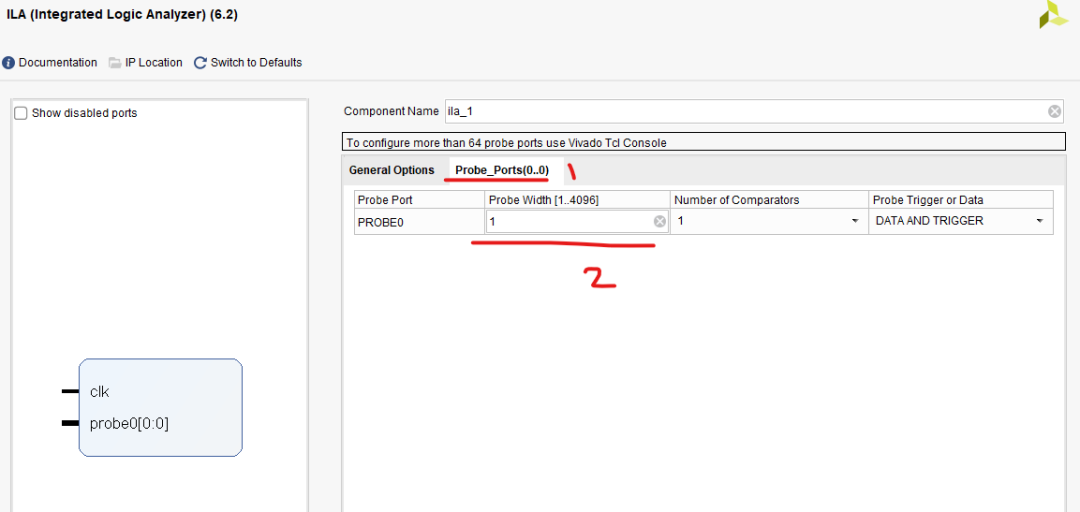

點擊1,然后可以在2處選擇信號的寬度,一般根據所配置的寄存器寬度進行填寫。

其他選項一般保持默認即可。然后點擊OK,進行添加ila。

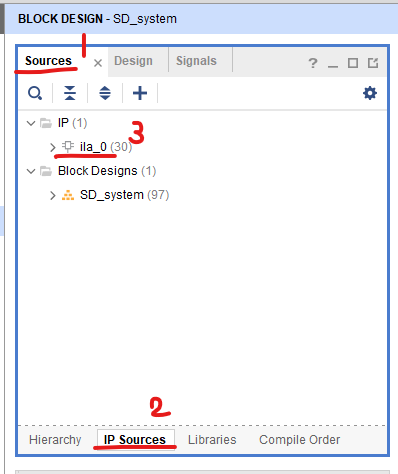

點擊所添加的ila。

打開.voe文件。

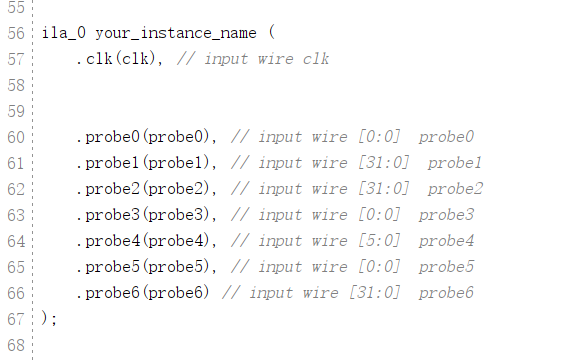

可以查看到生成后的參考代碼。

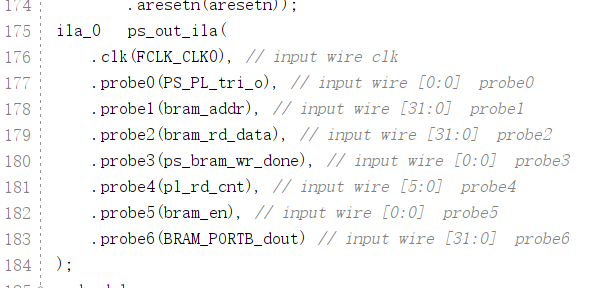

復制下來添加到需要觀察的信號的.v文件中,進行連接。

我這個是示例,根據自身需要觀察的信號進行連接。

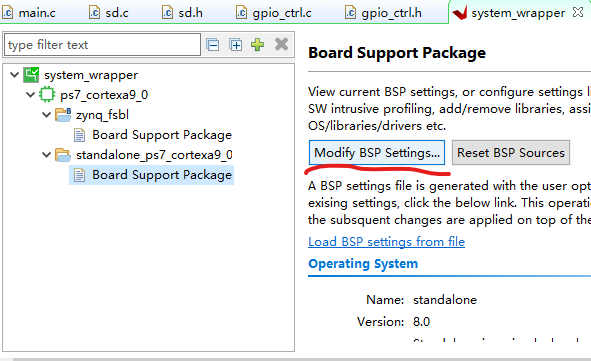

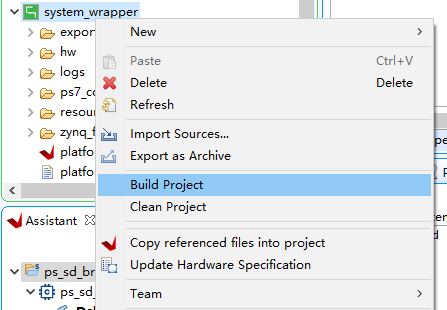

添加好后,生成bit流文件,然后導出,打開vitis文件。重新加載bsp。

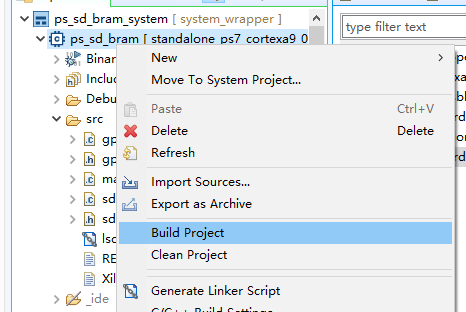

然后點擊vitis左上角的小錘子,然后編譯。

都進行編譯

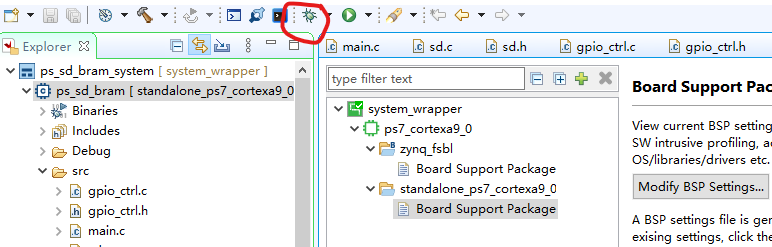

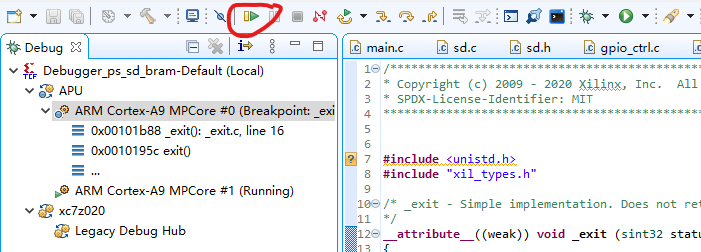

點擊小瓢蟲進入調試模式,等加載好后再進行下一步操作。

進入調試模式后先不要動vitis。

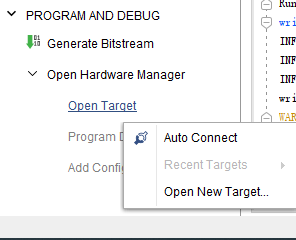

進入vivado,點擊自動連接。

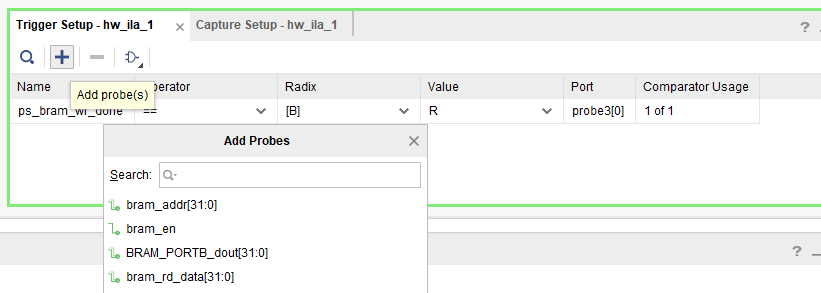

下面可以添加觸發信號。

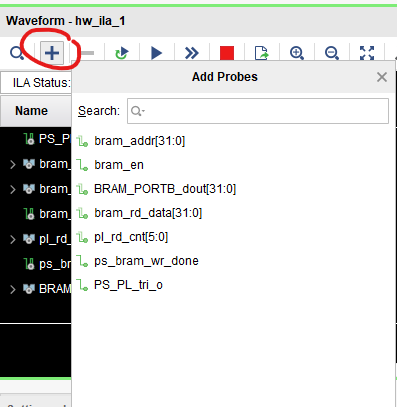

上面添加待觀察信號。

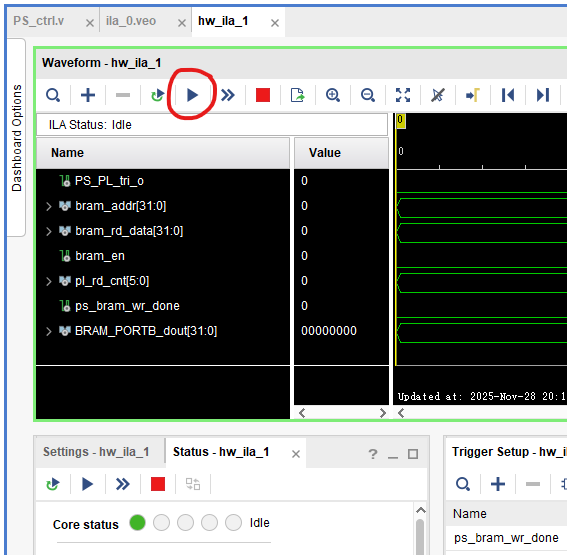

點擊開始,等待捕捉波形。

點擊vitis的調試模式下的運行鍵。

出現波形,捕捉成功。

-

調試

+關注

關注

7文章

650瀏覽量

35799 -

IP核

+關注

關注

4文章

344瀏覽量

52038 -

Vivado

+關注

關注

19文章

859瀏覽量

71270

原文標題:如何在vivado用ila進行debug調試

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

vivado ILA 實現在線調試功能報錯,顯示沒有添加ILA,怎么解決?

vivado ILA在線調試求助

ILA存在時實施失敗

Arty是否有可能不支持ILA調試?

Vivado+FPGA:如何使用Debug Cores(ILA)在線調試

Vivado中使用debug工具步驟與調試技巧

xilinx vivado zynq pldma PL部分ILA調試

如何使用Vivado Logic Analyzer與邏輯調試IP進行交互

如何使用Vivado在設備啟動時進行調試

Vivado調試ILA debug結果也許不對

關于Vivado中三種操作Debug的方式

Vivado使用技巧:debug仿真設計的三種調試方法

如何在vivado用ila進行debug調試

如何在vivado用ila進行debug調試

評論