基于ZYNQ-MZ702P開發(fā)板實現(xiàn)以太網(wǎng)通信

本章以太網(wǎng)通信實驗是基于ZYNQ-MZ702P開發(fā)板進行實現(xiàn),在配置方面,需要讀者自主修改不同的地方....

Vivado時序約束中invert參數(shù)的作用和應(yīng)用場景

在Vivado的時序約束中,-invert是用于控制信號極性的特殊參數(shù),應(yīng)用于時鐘約束(Clock ....

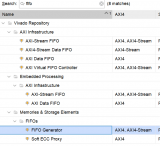

使用Vivado ILA進行復(fù)雜時序分析的完整流程

在 HDL 代碼中標(biāo)記待觀測信號,添加 (* mark_debug = "true" *) 屬性(V....

HLS設(shè)計中的BRAM使用優(yōu)勢

高層次綜合(HLS)是一種將高級編程語言(如C、C++或SystemC)轉(zhuǎn)換為硬件描述語言(HDL)....

FPGA+GPU異構(gòu)混合部署方案設(shè)計

為滿足對 “納秒級實時響應(yīng)” 與 “復(fù)雜數(shù)據(jù)深度運算” 的雙重需求,“FPGA+GPU”異構(gòu)混合部署....

FPGA DSP模塊使用中的十大關(guān)鍵陷阱

FPGA 芯片中DSP(數(shù)字信號處理)硬核是高性能計算的核心資源,但使用不當(dāng)會引入隱蔽性極強的“坑”....

數(shù)字IC/FPGA設(shè)計中的時序優(yōu)化方法

在數(shù)字IC/FPGA設(shè)計的過程中,對PPA的優(yōu)化是無處不在的,也是芯片設(shè)計工程師的使命所在。此節(jié)主要....

FPGA實現(xiàn)基于SPI協(xié)議的Flash驅(qū)動控制芯片擦除

本篇博客具體包括SPI協(xié)議的基本原理、模式選擇以及時序邏輯要求,采用FPGA(EPCE4),通過SP....

基于FPGA的高效內(nèi)存到串行數(shù)據(jù)傳輸模塊設(shè)計

本文介紹了一個基于FPGA的內(nèi)存到串行數(shù)據(jù)傳輸模塊,該模塊設(shè)計用來高效地處理存儲器中的數(shù)據(jù)并傳輸至串....

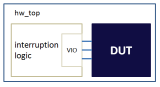

在FPGA設(shè)計中集成事件斷點的實現(xiàn)過程

如果對處于全速(at-speed)運行下的FPGA調(diào)試,工程師在現(xiàn)有通用“能力技術(shù)”基礎(chǔ)上,再增加“....

vivado JTAG鏈、連接、IP關(guān)聯(lián)規(guī)則介紹

這列出了定義板上可用的不同JTAG鏈。每個鏈都列在下面<jtag_chain>以及鏈的名稱,以及定義名稱和鏈中組件的位置。