多芯片LED集成封裝是實現大功率白光LED照明的方式之一。本文歸納了集成封裝的特點,從產品應用、封裝模式,散熱處理和光學設計幾個方面對其進行了介紹,并分析了集成封裝的發展趨勢,隨著大功率白光LED在照明領域的廣泛應用,集成封裝也將得到快速發展。

2016-01-19 11:30:02 4253

4253 去年年底已全球首發了“3DIC先進封裝設計分析全流程”EDA平臺,是其成為首家加入UCIe聯盟的中國本土EDA企業的關鍵推動力。 ? ? UCIe產業聯盟是一個由諸多半導體、科技、互聯網巨頭所建

2022-04-29 15:46:50 3180

3180

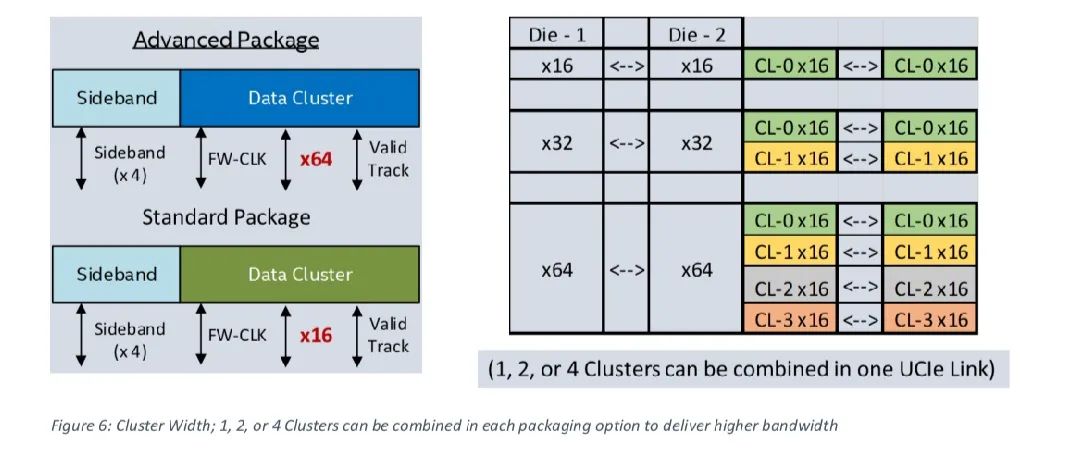

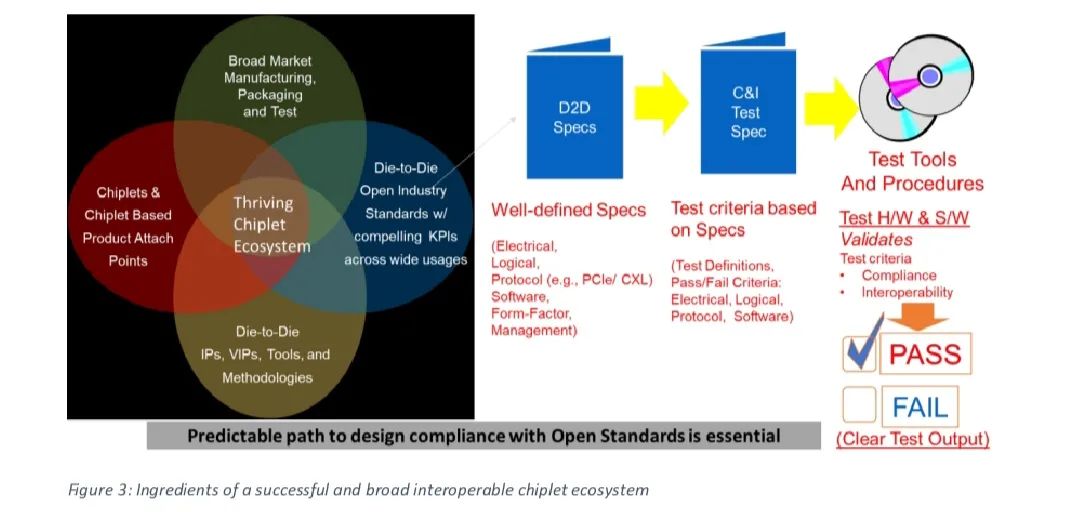

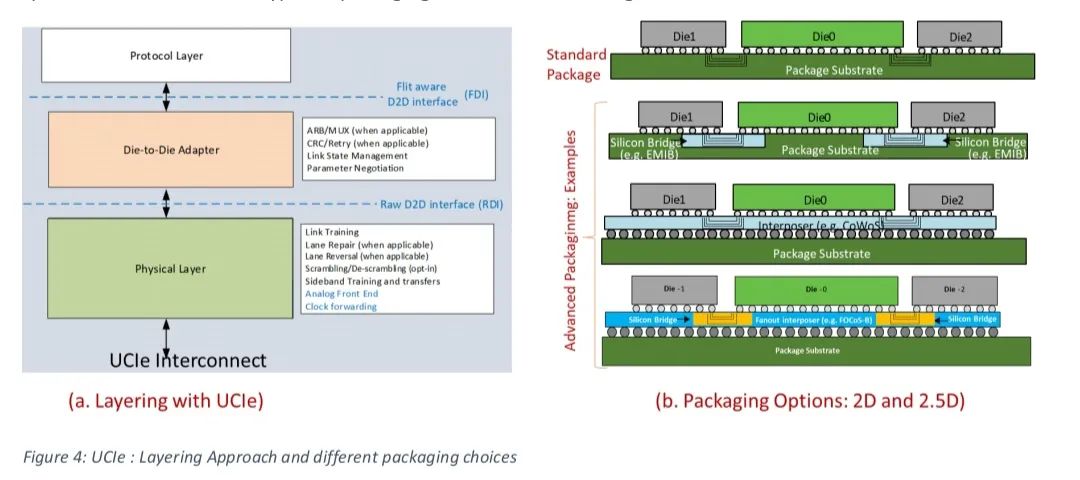

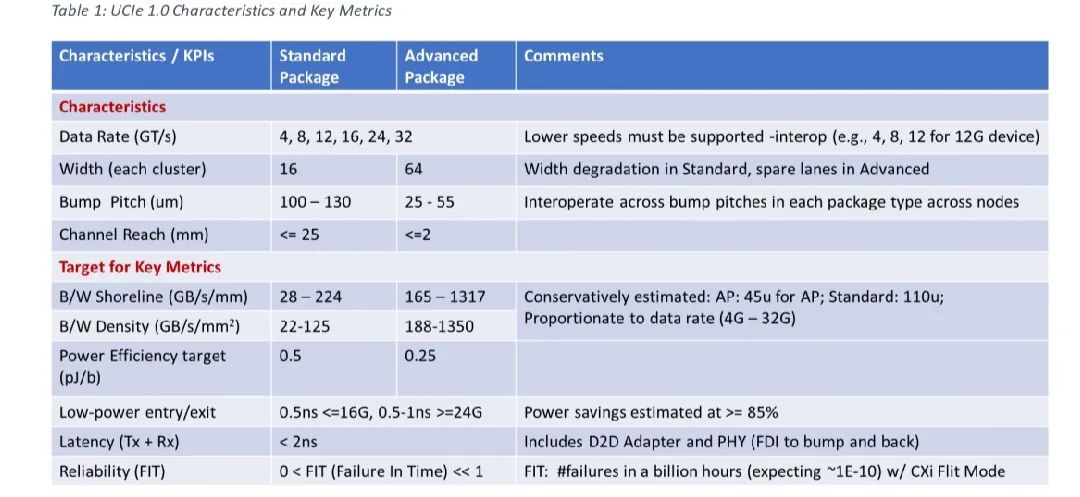

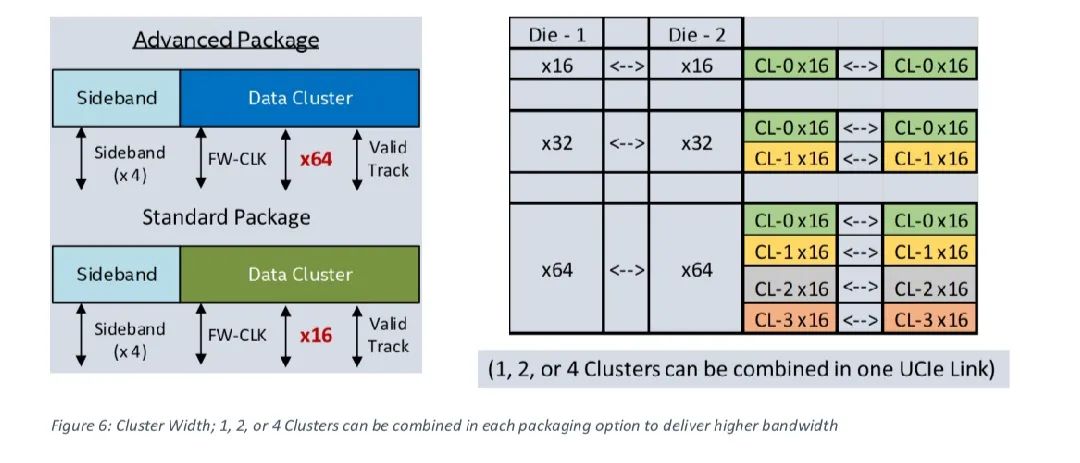

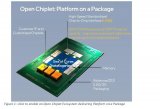

UCIe[4]是一種開放的行業標準互連,為異構芯片間提供了高帶寬、低延遲、高電源效率和高性價比的封裝內連接,以滿足整個計算系統的需求。

2022-10-10 09:33:49 4118

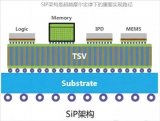

4118 SiP(System in Package)技術是一種先進的封裝技術,SiP技術允許將多個集成電路(IC)或者電子組件集成到一個單一的封裝中。這種SiP封裝技術可以實現不同功能組件的物理集成,而這些組件可能是用不同的制造工藝制造的。

2024-02-19 15:22:19 7275

7275

為適應異構集成技術的應用背景,封裝天線的實現技術也應有所變化,利用封裝工藝的優點以實現更佳的性能。

2024-02-29 11:11:30 2773

2773

通用芯粒互連技術(UCIe)為半導體行業帶來了諸多可能性,在Multi-Die設計中實現了高帶寬、低功耗和低延遲的Die-to-Die連接。它支持定制HBM(cHBM)等創新應用,滿足了I/O裸片

2025-08-04 15:17:24 2452

2452 電子發燒友網報道(文/李誠)3月2日,AMD、ARM、英特爾等多家國際半導體巨頭聯合推出了全新的芯片互聯標準UCIe 1.0。UCIe 1.0標準是針對Chiplet技術建立的,致力于推動芯片互聯

2022-03-04 07:16:00 2815

2815 在半導體封裝領域,堆疊技術作為推動高集成度與小型化的核心趨勢,正通過垂直堆疊芯片或封裝實現更緊湊的封裝尺寸及優化的電氣性能——其驅動力不僅源于信號傳輸與功率分布路徑的縮短,更體現在對系統級封裝(SiP)與三維集成(3D IC)的深度探索中。

2025-10-21 17:29:17 4787

4787

封裝技術與加密技術一.4大主流封裝技術半導體 封裝 是指將通過測試的晶圓按照產品型號及功能需求加工得到獨立芯片的過程。封裝技術是一種將集成電路用絕緣的塑料或陶瓷材料打包的技術。以CPU為例,實際看到

2022-01-25 06:50:46

》報告呈獻給大家。摘要:封裝天線(簡稱AiP)是基于封裝材料與工藝,將天線與芯片集成在封裝內實現系統級無線功能的一門技術。AiP技術順應了硅基半導體工藝集成度提高的潮流,為系統級無線芯片提供了良好的天線

2019-07-16 07:12:40

`本文指出了集成電源是電源技術發展的必然方向,目前混合封裝技術是集成電源模塊的主流方式,闡述了混合封裝技術的若干關鍵技術問題和發展方向,最后介紹了若干基于混合封裝技術的集成電源模塊。`

2011-03-09 17:15:59

研究院(先進電子封裝材料廣東省創新團隊)、上海張江創新學院、深圳集成電路設計產業化基地管理中心、桂林電子科技大學機電工程學院承辦的 “第二期集成電路封裝技術 (IC Packaging

2016-03-21 10:39:20

什么是集成電路?有哪些分類?集成電路的工作原理是什么?由什么組成?集成電路的封裝形式有哪幾種?

2021-11-02 09:48:31

《集成電路芯片封裝技術》是一本通用的集成電路芯片封裝技術通用教材,全書共分13章,內容包括:集成電路芯片封裝概述、封裝工藝流程、厚膜與薄膜技術、焊接材料、印制電路板、元件與電路板的連接、封膠材料

2012-01-13 13:59:52

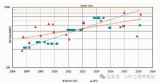

和其他LSI集成電路都起著重要的作用。新一代CPU的出現常常伴隨著新的封裝形式的使用。芯片的封裝技術已經歷了好幾代的變遷,從DIP、QFP、PGA、BGA到CSP再到MCM,技術指標一代比一代先進,包括

2018-08-28 11:58:30

集成電路芯片封裝技術知識詳解本電子書對封裝介紹的非常詳細,所以和大家分享。因為太大,沒有上傳。請點擊下載。[此貼子已經被作者于2008-5-12 22:45:41編輯過]

2008-05-12 22:44:28

跪求指點,AD20 建立集成庫老是出錯,原理圖庫添加不了封裝,集成庫編譯過,有時候關閉了,下次打開又能關聯起來

2023-10-14 11:05:19

本帖最后由 jun228zhang 于 2018-4-3 10:58 編輯

Altium Designer PCB封裝集成庫,三年的結晶 Altium Designer PCB封裝集成庫

2013-03-07 16:42:27

別告訴我把它打開,然后把那里面的庫提取出來。我以前在選PCB封裝時,可以直接選集成庫里的封裝,最近不知怎么的集成庫里的封裝就不顯了,我希望可以把這個功能調出來,使用時會方便很多。電腦重啟了,軟件重裝

2012-11-09 18:40:18

BGA封裝技術是一種先進的集成電路封裝技術,主要用于現代計算機和移動設備的內存和處理器等集成電路的封裝。與傳統的封裝方式相比,BGA封裝具有更小的體積,更好的散熱性能和電性能,可在相同體積下提高

2023-04-11 15:52:37

來看看。 一、CPU封裝的定義 所謂的CPU,拆開外殼來看,其實也是一個滲入高技術含量的集成電路板。那么在業內就有按照CPU的實質給出其封裝技術的定義: 封裝技術是一種將集成電路用絕緣的塑料或陶瓷材料

2013-09-17 10:31:13

來看看。 一、CPU封裝的定義 所謂的CPU,拆開外殼來看,其實也是一個滲入高技術含量的集成電路板。那么在業內就有按照CPU的實質給出其封裝技術的定義: 封裝技術是一種將集成電路用絕緣的塑料或陶瓷材料

2013-10-17 11:42:40

什么影響呢?我們一起來看看。 一、CPU封裝的定義 所謂的CPU,拆開外殼來看,其實也是一個滲入高技術含量的集成電路板。那么在業內就有按照CPU的實質給出其封裝技術的定義: 封裝技術是一種將集成電路用

2018-09-17 16:59:48

這種技術的中文含義叫方型扁平式封裝技術(Plastic Quad Flat Pockage),該技術實現的CPU芯片引腳之間距離很小,管腳很細,一般大規模或超大規模集成電路采用這種封裝形式,其引腳

2018-08-23 09:33:08

所謂“CPU封裝技術”是一種將集成電路用絕緣的塑料或陶瓷材料打包的技術。以CPU為例,我們實際看到的體積和外觀并不是真正的CPU內核的大小和面貌,而是CPU內核等元件經過封裝后的產品

2018-08-29 10:20:46

誰來闡述一下cof封裝技術是什么?

2019-12-25 15:24:48

在主板上。qfp封裝 這種技術的中文含義叫方型扁平式封裝技術(plastic quad flat pockage),該技術實現的cpu芯片引腳之間距離很小,管腳很細,一般大規模或超大規模集成電路采用

2015-02-11 15:36:44

集成無源元件技術可以集成多種電子功能,具有小型化和提高系統性能的優勢,以取代體積龐大的分立無源元件。文章主要介紹了什么是集成無源元件?集成無源元件對PCB技術發展產生了什么影響?

2019-08-02 07:04:23

微波集成電路技術是無線系統小型化的關鍵技術.在毫米波集成電路中,高性能且設計緊湊的功率放大器芯片電路是市場迫切需求的產品.

2019-09-11 11:52:04

電話網已有PBX的情況下,得到一個針對多種計算機電話集成技術業務的統一平臺。但是統一設計出開發計算機電話集成技術業務的平臺,以便通過集成已有產品來保證用戶的投資,實現起來卻遠非易事,其原因主要有兩個方面,一是技術, 二是業務。

2019-09-10 10:42:17

Anatya vallaph 說,為了實現無傳感器控制、自動和集成狀態機邏輯控制電機等功能,“需要高度智能的算法來控制系統。”。他補充道,“這些應該遵循旋轉發動機的理論機制。”此外,還要注意操作過程

2022-03-07 18:22:23

如電阻、電容、電感、濾波器、耦合器等集成到一個封裝體內,因而可以有效而又最便宜地使用各種工藝組合,實現整機系統的功能。 LTCC技術是近年來興起的一種令人矚目的整合組件技術,由于LTCC材料優異

2019-07-29 06:16:56

移動機器人利用導航技術,獲得機器人的目前所處的位置,結合傳感器技術對周圍外界環境(障礙物等)作實時探測,并根據環境提供的信息規劃一條可行路徑完成達到目標點的任務。移動機器人技術涉及到傳感器技術

2020-11-23 15:08:52

沒有讀者認識到發生在3DIC集成中的技術進步,他們認為該技術只是疊層和引線鍵合,是一種后端封裝技術。而我們該如何去拯救3DIC集成技術?

2021-04-07 06:23:51

封裝。20世紀90年代,隨著技術的進步,芯片集成度不斷提高,I/O引腳數急劇增加,功耗也隨之增大,對集成電路封裝的要求也更加嚴格。為了滿足發展的需要,BGA封裝開始被應用于生產。采用BGA技術封裝的內存

2020-02-24 09:45:22

由于引線互連帶來的種種問題,人們開始研究如何改進互連技術,以避免采用引線。1995年以后,陸續開發出了一些無引線的集成功率模塊,其特點是:互連結構的電感小、散熱好、封裝牢固等。圖1(a)、圖1

2018-11-23 16:56:26

的現有低寄生電感封裝方式進行分類對比;羅列比較現有提高封裝高溫可靠性的材料和制作工藝,如芯片連接材料與技術;最后,討論現有多功能集成封裝方法,介紹多種先進散熱方法。在前面綜述的基礎上,結合電力電子

2023-02-22 16:06:08

變頻器和PLC的雙饋電動機節能技術優勢是什么?怎么實現基于PLC和變頻器的雙饋電動機節能控制系統設計?

2021-05-31 06:37:08

如何往AD集成庫增加PCB封裝?

2019-09-16 10:28:13

急需一個HR911105A的集成封裝......

2016-03-02 20:03:41

裝SMC和SMD來實現立體封裝,這種結構稱為埋置型3D封裝;第二種是在硅圓片規模集成(WSl)后的有源基板上再實行多層布線,最上層再貼裝SMC和SMD,從而構成立體封裝,這種結構稱為有源基板型3D封裝

2018-09-12 15:15:28

新建元器件時,追加封裝,我在集成庫里搜索到我需要的封裝,但是選擇后出不來封裝圖,顯示在集成庫和封裝庫里沒有找到,這是什么情況,封裝在集成庫里的時候怎么設置

2017-03-21 22:34:36

`求教大蝦,附圖所示的SOP20封裝集成電路是啥?最好有詳細的相關技術資料。`

2018-04-08 08:12:57

真正將集成模塊的概念付諸實現,在很大程度上取決于集成和封裝的工藝技術。1傳統封裝結構與互連方式存在的主要問題1 封裝技術是研究電力電子集成模塊的核心問題電力電子集成的基本思路可以分成單片集成和多芯片

2018-08-28 11:58:28

產業的發展也帶動了與之密切相關的電子封裝業的發展,其重要性越來越突出。電子封裝已從早期的為芯片提供機械支撐、保護和電熱連接功能,逐漸融人到芯片制造技術和系統集成技術之中。電子工業的發展離不開電子封裝的發展

2018-08-23 12:47:17

SMD即表面貼裝技術是在大約二十年前推出。 SMD:它是表面安裝設備的縮寫,意思是:表面貼裝器件,它是表面貼裝技術(表面貼裝技術:表面安裝技術)中,從而開創了一個新的時代。從被動到主動元件和集成

2012-06-07 08:55:43

SMD即表面貼裝技術是在大約二十年前推出。 SMD:它是表面安裝設備的縮寫,意思是:表面貼裝器件,它是表面貼裝技術(表面貼裝技術:表面安裝技術)中,從而開創了一個新的時代。從被動到主動元件和集成

2012-06-09 09:58:21

和其他LSI集成電路都起著重要的作用。新一代CPU的出現常常伴隨著新的封裝形式的使用。芯片的封裝技術已經歷了好幾代的變遷,從DIP、QFP、PGA、BGA到CSP再到MCM,技術指標一代比一代先進

2018-09-03 09:28:18

、半導體集成電路技術于一體,是典型的垂直集成技術,對半導體器件來說,它是典型的柔型封裝技術,是一種電路的集成。MCM的出現使電子系統實現小型化、模塊化、低功耗、高可靠性提供了更有效的技術保障[5]。 MCM

2018-11-23 16:59:52

集成電路封裝技術詳解包括了概述,陶瓷封裝,塑料封裝,金屬封裝,其它封裝等。

2008-05-12 22:41:56 705

705 系統級封裝(SiP)集成技術的發展與挑戰:摘要:系統級封裝集成技術是實現電子產品小型化和多功能化的重要手段。國際半導體技術發展路線已經將SiP 列為未來的重要發展方向。本文

2009-12-21 09:30:30 24

24 LED 在照明領域的廣泛應用,集成封裝也將得到快速發展。 目前,實現大功率LED 照明的方法有兩種:一是對單顆大功率LED 芯片進行封裝,二是采用多芯片集成封裝。對于前者來說,隨著芯片技術的發展,尺寸增大,品質提高,可通過大電流驅動實現

2017-10-10 17:07:20 9

9 照明領域的廣泛應用,集成封裝也將得到快速發展。 目前,實現大功率LED照明的方法有兩種:一是對單顆大功率LED芯片進行封裝,二是采用多芯片集成封裝。對于前者來說,隨著芯片技術的發展,尺寸增大,品質提高,可通過大電流驅動實現大功

2017-11-10 14:50:45 1

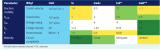

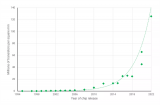

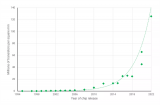

1 除了先進制程之外,先進封裝也成為延續摩爾定律的關鍵技術,像是2.5D、3D 和Chiplets 等技術在近年來成為半導體產業的熱門議題。究竟,先進封裝是如何在延續摩爾定律上扮演關鍵角色?而2.5D、3D 和Chiplets 等封裝技術又有何特點?

2020-10-09 11:35:35 5749

5749 除了先進制程之外,先進封裝也成為延續摩爾定律的關鍵技術,像是2.5D、3D 和Chiplets 等技術在近年來成為半導體產業的熱門議題。究竟,先進封裝是如何在延續摩爾定律上扮演關鍵角色?而2.5D、3D 和Chiplets 等封裝技術又有何特點?

2020-10-12 09:34:00 2822

2822 封裝對于集成電路來講是最主要的工具,先進的封裝方法可以顯著地幫助提高IC性能。了不起的是,這些技術中有許多已經足夠成熟,而且已經存在足夠長的時間,現在甚至連初創公司和大學都可以使用它們。

2020-11-17 11:51:42 1286

1286 最近兩周,Chiplet相關新聞的頻出 。NVIDIA宣布了一款令人興奮的新型NVLink-C2C互連,用于其CPU、DPU、GPU以及與其合作伙伴和客戶的其他集成之間的緊密耦合鏈路。 UCIe

2022-03-29 18:12:31 9462

9462

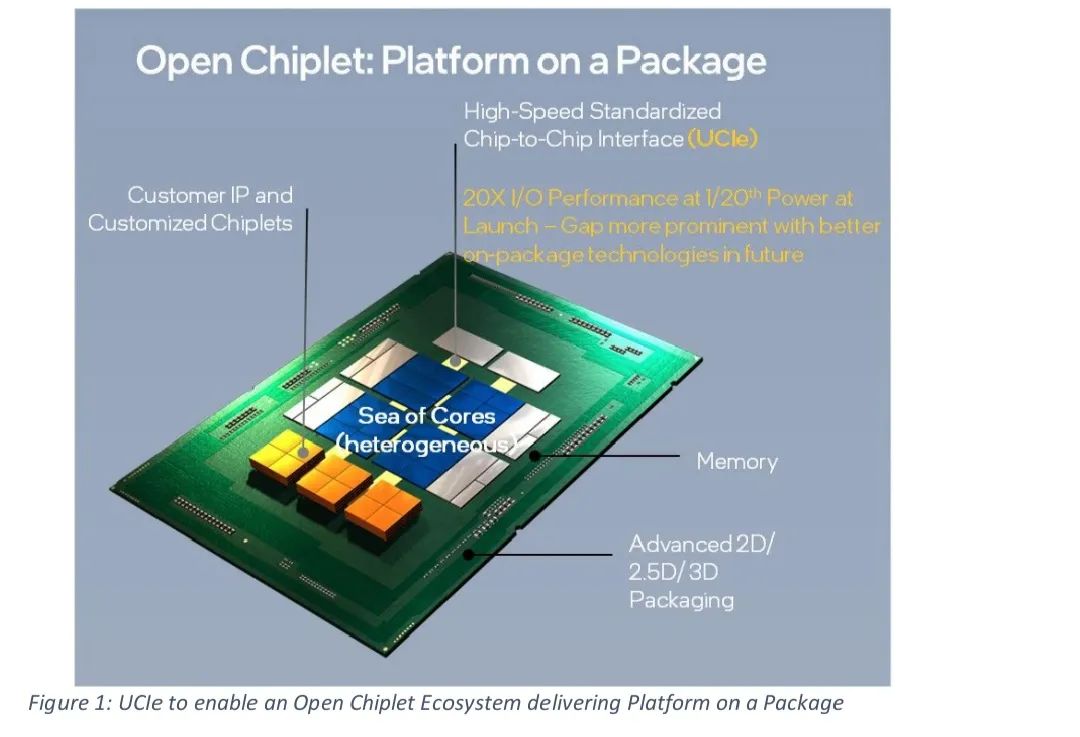

今年3月,由日月光、AMD、ARM、谷歌 Cloud、英特爾、微軟、高通、三星和臺積電十家公司成立UCIe(Universal Chiplet Interconnect Express)產業聯盟。該聯盟是由全球科技行業巨頭共同推出的一個全新的通用芯片互連標準。

2022-04-07 11:12:03 1448

1448 上月初,英特爾攜手日月光半導體(ASE)、AMD、Arm、谷歌云、Meta、微軟、高通、三星和臺積電等廠商發起UCIe產業聯盟(通用芯粒高速互連),意欲推行開放的晶片間互連標準。可以說UCIe的出現

2022-04-08 11:26:53 1373

1373 國產EDA行業的領軍企業芯和半導體近日宣布正式加入UCIe(Universal Chiplet Interconnect Express)產業聯盟。芯和半導體早在去年年底已全球首發了“3DIC先進封裝設計分析全流程”EDA平臺,是其成為首家加入UCIe聯盟的中國本土EDA企業的關鍵推動力。

2022-05-09 11:28:07 2972

2972 中國一站式IP和定制芯片領軍企業芯動科技(INNOSILICON)宣布正式加入UCIe產業聯盟,助力Chiplet標準化,致力于Chiplet創新、迭代和商用。同時,芯動自研的首套跨工藝、跨封裝

2022-08-16 09:39:58 2436

2436 支持 UCIe 的還有云和技術領導者 Google、Meta 和 Microsoft。總共約有 50 家公司加入了 UCIe 聯盟,以幫助構建Chiplet生態系統,為不同供應商在封裝中采用不同工藝技術設計和制造的 IP 的混合和匹配打開了大門。

2022-09-05 15:41:12 953

953 UCIe 是唯一為芯片到芯片接口定義完整堆棧的規范。其他標準僅關注特定層,并且與 UCIe 不同,不為協議棧的完整裸片到裸片接口提供全面的規范。

2022-09-28 10:30:34 1658

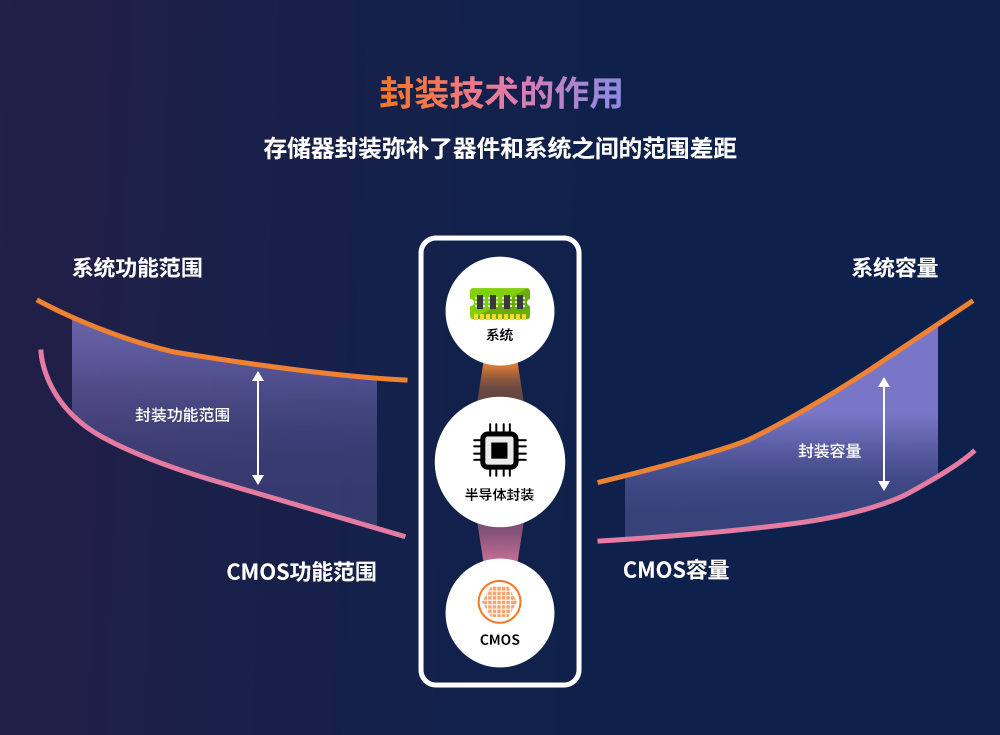

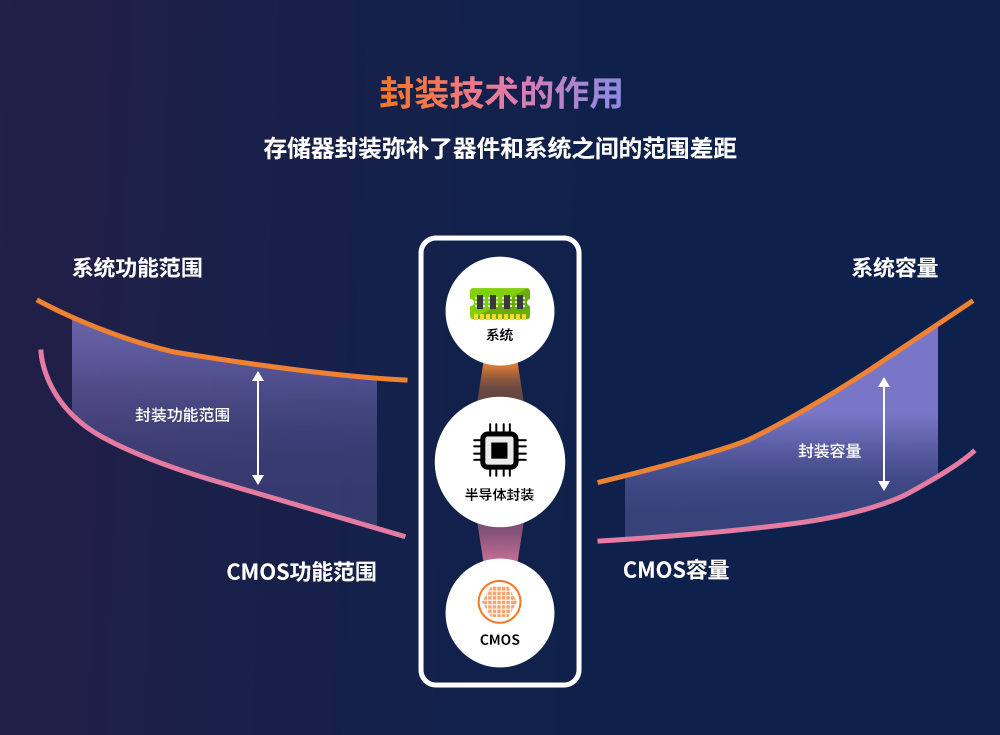

1658 。其他名稱包括半導體器件組裝、組裝、封裝或密封。封裝階段之后是集成電路的測試。下面小編就來講訴一下半導體集成電路封裝技術的作用,以及體集成電路芯片封裝的意義。 集成電路封裝技術 “封裝”一詞伴隨集成電路制造技術

2022-12-13 09:18:24 6105

6105 世芯電子正式宣布以貢獻者(Contributor)會員身份加入UCIe?(Universal Chiplet Interconnect Express?)產業聯盟,參與UCIe技術標準的研究,結合

2022-12-22 14:55:26 1744

1744 技術標準的研究,結合本身豐富的先進封裝(2.5D及CoWoS)量產及HPC ASIC設計經驗,將進一步鞏固其高性能ASIC領導者的地位。 UCIe可滿足來自不同的晶圓廠、不同工藝、有著不同設計的各種

2022-12-22 20:30:36 3185

3185 ?)產業聯盟。結合自身豐富的先進封裝(2.5D/3D)經驗,華邦將積極參與UCIe產業聯盟,助力高性能chiplet接口標準的推廣與普及。 ? UCIe產業聯盟聯合了諸多領先企業,致力于推廣UCIe開放標準

2023-02-15 10:38:47 762

762

的領先企業,廣立微將與聯盟內的其他成員一道,共同致力于下一代UCIe技術標準的研究與應用,結合自身在測試芯片設計和良率分析領域的優勢 ,為推動先進封裝技術的開發做出積極貢獻。 關于UCIe UCIe成立

2023-02-21 09:43:29 1346

1346

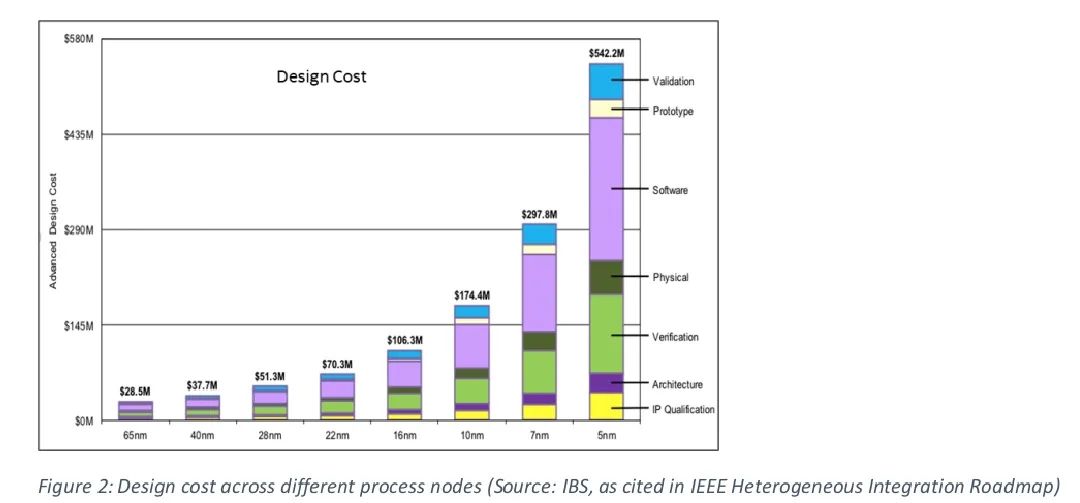

2022年3月,Intel、AMD、ARM、高通、三星、臺積電、ASE、Google Cloud、Meta和微軟十家巨頭成立Chiplet標準聯盟,制定了通用Chiplet的高速互聯標準UCIe

2023-02-22 08:40:04 1123

1123 來源:Cadence楷登 2023年4月26日,楷登電子近日宣布基于臺積電 3nm(N3E)工藝技術的 Cadence? 16G UCIe? 2.5D 先進封裝 IP 成功流片。該 IP 采用臺積電

2023-04-27 16:35:40 1377

1377

Chiplet也稱為“小芯片”或“芯粒”,它是一種功能電路塊,包括可重復使用的IP塊。出于成本和良率等考慮,一個功能豐富且面積較大的芯片裸片(die)可以被拆分成多個小芯片,這些預先生產好的、能實現特定功能的小芯片組合在一起,借助先進的集成技術(比如3D封裝)被集成封裝在一起即可組成一個系統芯片。

2023-05-18 09:17:57 1502

1502 多芯片封裝技術是一種將多個芯片封裝在同一個封裝體內的集成封裝技術。在傳統的單芯片封裝中,一個封裝體內只封裝一個芯片,而多芯片封裝技術將多個芯片封裝在一個封裝體中,實現了不同功能芯片的集成和協同工作。

2023-05-24 16:22:31 4884

4884 Chiplets的主導地位才剛剛開始。

2023-06-05 18:08:42 853

853

(UniversalChipletInterconnectExpress,UCIe),旨在標準化小芯片的構建和相互通信方式。過去幾年的一大趨勢是業內越來越多地使用多裸片先進封裝

2022-10-18 09:31:47 1985

1985

上海伯東美國 Gel-Pak 以 Vertec? 技術開發了新一代專利的 BTXF 芯片盒, 使用了一種非粘性的微紋理彈性體, 將其涂覆在 JEDEC 托盤上, 可以將 Chiplets 產品固定其上, Gel-Pak?BTXF 芯片盒可以廣泛的應用在 Chiplets 的內部流轉, 整體運輸上.

2023-05-26 14:40:59 1630

1630

此外,智原對于Interposer的需求會進行芯片大小、TSV、微凸塊間距和數量、電路布局規劃、基板、功率分析和熱仿真等信息研究,深入了解Chiplets信息并評估Interposer制造及封裝的可執行性。

2023-09-12 16:27:47 1345

1345 實現Chiplets封裝集成的動機有很多。為了滿足不斷增長的性能需求,芯片面積不斷增加,有些設計甚至會超出掩模版面積的限制,比如具有數百個核心的多核 CPU,或扇出非常大的交換[曹1] 電路(Switch)。

2023-11-06 09:19:48 2529

2529

異構集成時代半導體封裝技術的價值

2023-11-28 16:14:14 1012

1012

Universal Chiplet Interconnect Express (UCIe) 是一個開放的行業互連標準,可以實現小芯片之間的封裝級互連,具有高帶寬、低延遲、經濟節能的優點。

2023-12-11 10:37:32 5092

5092

先進的封裝技術可以將多個半導體芯片和組件集成到高性能的系統中。隨著摩爾定律的縮小趨勢面臨極限,先進封裝為持續改善計算性能、節能和功能提供了一條途徑。但是,與亞洲相比,美國目前在先進封裝技術方面落后

2023-12-14 10:27:14 2276

2276

什么是Chiplet技術?Chiplet技術是一種在半導體設計和制造中將大型芯片的不同功能分解并分散實現在多個較小和專用的芯片(Chiplets)上的方法。這些較小的芯片隨后通過高速互連方式集成到一個封裝中,共同實現全功能的芯片系統。

2024-01-25 10:43:32 4059

4059

當前,由于整個半導體產業步入將多個‘芯粒’(Chiplets)整合于單一封裝的新世代,芬柯斯(Foveros)與 EMIB(嵌入式多芯片互聯橋接)等英特爾先進封裝技術應運而生。

2024-01-25 14:47:14 1405

1405 英特爾在封裝技術方面取得了重大突破,并已經開始大規模生產基于3D Foveros技術的產品。這項技術使得英特爾能夠在單個封裝中整合多個小芯片(Chiplets),從而提高了芯片的性能、尺寸和設計靈活性。

2024-01-26 16:04:50 1281

1281 《半導體芯科技》雜志文章 芯問科技“太赫茲芯片集成封裝技術”項目近日順利通過上海市科學技術委員會的驗收。 該項目基于太赫茲通信、太赫茲成像等應用對高集成太赫茲封裝系統的迫切需求,開展了太赫茲集成封裝

2024-04-02 15:23:09 1488

1488 英特爾的測試芯片Pike Creek由基于Intel 3技術制造的英特爾UCIe IP小芯片組成。它與采用臺積電公司N3工藝制造的新思科技UCIe IP測試芯片形成組合。

2024-04-18 14:22:54 1756

1756 基于 CoWoS-R 技術的 UCIe 協議與 IPD 的高速互連是小芯片集成和 HPC 應用的重要平臺。

2024-04-20 17:48:37 2940

2940

電子發燒友網站提供《集成電路中的封裝技術.pdf》資料免費下載

2024-05-23 09:16:23 0

0 IP,可實現異構和同構芯片之間的快速連接。 新思科技40G UCIe PHY IP 能夠在同樣的芯片尺寸和能效基礎上,提供比 UCIe 規范高 25% 的帶寬。 集成了信號完整性監控器和可測試性功能從而提高多芯片系統封裝的可靠性,并可在整個芯片生命周期內進行現場監控。 新思科技40G UC

2024-09-10 13:45:37 771

771 ? 本文將分享 MathWorks 參與 中國集成電路設計業高峰論壇暨展覽會 ICCAD-Expo 的展臺展示以及發表主題演講《MATLAB 加速數字和模擬芯片設計--高效實現 HLS、UCIe

2024-12-20 11:11:22 1348

1348

(UCIe)系列產品在性能與效率上實現了重大突破。新一代UCIe物理層IP基于臺積電N4制程,預計于今年完成設計定案,支持每通道高達64GT/s的傳輸速度,展現了其在高帶寬應用領域的技術實力。 憑借豐富

2025-01-17 10:55:12 332

332 取得了重大進展。這一突破性成果標志著乾瞻科技在高速傳輸技術領域再次邁上了新的臺階。 據悉,乾瞻科技新一代UCIe物理層IP是基于臺積電先進的N4制程打造的。該IP設計預計在今年內完成定案,并將支持每通

2025-01-21 10:44:01 906

906 受限,而芯片級架構通過將SoC分解為多個小芯片(chiplets),利用先進封裝技術實現高性能和低成本。 芯片級架構通過將傳統單片系統芯片(SoC)分解為多個小芯片(chiplets),利用先進封裝技術實現高性能和低成本。 3.5D封裝結合了2.5D和3D封裝技術的優點,通

2025-02-14 16:42:43 1964

1964

我們很高興能在此宣布,Cadence 基于 UCIe 標準封裝 IP 已在 Samsung Foundry 的 5nm 汽車工藝上實現首次流片成功。這一里程碑彰顯了我們持續提供高性能車規級 IP 解決方案?的承諾,可滿足新一代汽車電子和高性能計算應用的嚴格要求。

2025-04-16 10:17:15 843

843

3D異質集成(3DHI)技術可將不同類型、垂直堆疊的半導體芯片或芯粒(chiplet)集成在一起,打造高性能系統。因此,處理器、內存和射頻等不同功能可以集成到單個芯片或封裝上,從而提高性能和效率

2025-06-13 16:27:54 511

511

電子發燒友App

電子發燒友App

評論