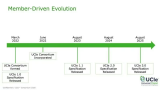

全球高速接口IP領域的佼佼者乾瞻科技(InPsytech, Inc.)近日宣布,其Universal Chiplet Interconnect Express(UCIe)系列產品在性能與效率方面取得了重大進展。這一突破性成果標志著乾瞻科技在高速傳輸技術領域再次邁上了新的臺階。

據悉,乾瞻科技新一代UCIe物理層IP是基于臺積電先進的N4制程打造的。該IP設計預計在今年內完成定案,并將支持每通道高達64GT/s的傳輸速度。這一速度的提升,無疑將為高帶寬應用領域帶來更為出色的性能和效率表現。

乾瞻科技作為高速接口IP設計的領先企業,一直致力于推動相關技術的創新與發展。此次UCIe系列產品的重大突破,不僅展示了乾瞻科技在高速傳輸技術領域的深厚積累,也為其在未來市場競爭中占據了有利地位。

乾瞻科技表示,他們將繼續加大在高速接口IP領域的研發投入,不斷推出更加先進、高效的產品解決方案,以滿足市場對于高性能、高效率傳輸技術的迫切需求。同時,他們也將積極與產業鏈上下游企業開展合作,共同推動高速傳輸技術的持續進步與發展。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

臺積電

+關注

關注

44文章

5803瀏覽量

176277 -

接口

+關注

關注

33文章

9519瀏覽量

157014 -

UCIe

+關注

關注

0文章

53瀏覽量

2016

發布評論請先 登錄

相關推薦

熱點推薦

如何突破AI存儲墻?深度解析ONFI 6.0高速接口與Chiplet解耦架構

:ONFI 6.0 PHY IP作為全球領先的集成電路IP供應商,奎芯科技已實現對ONFI 6.0標準的全面支持,旨在破解大數據時代的存取鴻溝。? 極致傳輸速率:支持最高 4800Mb

發表于 01-29 17:32

國產高性能ONFI IP解決方案全解析

單一IP到Chiplet架構? 接口解耦與異質集成:奎芯通過 M2LINK 等互聯方案,將高速接口IP與 IO Die 技術結合,實現了存儲

發表于 01-13 16:15

Cadence公司成功流片第三代UCIe IP解決方案

為推動小芯片創新的下一波浪潮,Cadence 成功流片其第三代通用小芯片互連技術(UCIe)IP 解決方案,在臺積電先進的 N3P 工藝上實現了業界領先的每通道 64Gbps 速率。隨

隼瞻科技:以DSA技術為核,IP+EDA工具雙驅,賦能端側AI NPU算力效率躍升

設計的需求變化,以及隼瞻科技自研EDA、IP產品如何積極助力客戶成功等話題。 ? 端側AI芯片設計的痛點 ? “隼瞻科技定位于服務半導體設計公司,提供IP核及EDA工具等解決方案,助力

RDMA設計5:RoCE V2 IP架構

專注高性能存儲與傳輸,在本博客已給出相關博文已100多篇,希望對初學者有用。注意這里只是拋磚引玉,切莫認為參考這就可以完成商用IP設計。

為便于讀者更好的理解IP設計,這里以高速數據

發表于 11-25 10:34

華為助力南非MTN在IP網絡領域實現突破

在全球通信行業權威機構TM Forum(全球電信管理論壇)組織的自智網絡(Autonomous Network,簡稱“AN”)等級測評中,華為助力南非MTN在IP網絡領域實現突破,獲得TM

高速光耦的技術突破與系統賦能

工業自動化與數字控制系統的實時性需求持續升級,對信號隔離技術提出更嚴苛要求。高速光耦作為光電隔離領域的核心器件,通過創新的載流子調控機制與材料體系突破,在電力電子、通信控制及精密設備中構建高速

Cadence基于臺積電N4工藝交付16GT/s UCIe Gen1 IP

我們很高興展示基于臺積電成熟 N4 工藝打造的 Gen1 UCIe IP 的 16GT/s 眼圖。該 IP 一次流片成功且眼圖清晰開闊,為尋求 Die-to-Die連接的客戶再添新選擇。

奇異摩爾Die-to-Die片內互聯方案持續升級

當AI大模型參數規模突破萬億級別,傳統單芯片設計遭遇物理極限。芯粒技術通過模塊化組合突破瓶頸,而芯片間互聯帶寬成為決定性因素之一。近期,UCIe 3.0規范將數據

華為高管:搭載華為乾崑智駕的汽車突破100萬輛

電子發燒友網綜合報道 2025年8月12日,華為智能汽車解決方案BU CEO靳玉志在社交媒體平臺發文稱,搭載華為乾崑智駕的汽車突破100萬輛。 ? 華為乾崑智駕是華為2024年發布的以智能駕駛為核心

新思科技UCIe IP解決方案實現片上網絡互連

通用芯粒互連技術(UCIe)為半導體行業帶來了諸多可能性,在Multi-Die設計中實現了高帶寬、低功耗和低延遲的Die-to-Die連接。它支持定制HBM(cHBM)等創新應用,滿足了I/O裸片

晟聯科受邀出席臺積電技術研討會,高速接口IP組合及解決方案助推海量數據暢行

接口 IP 組合與解決方案,助力客戶創新。 高速接口IP組合驚艷亮相,“打破邊界,讓數據暢行” 在數字化浪潮席卷全球的當下,數據量呈指數級增長,數據的高效穩定傳輸成為數字經濟蓬勃發展的

NVMe IP高速傳輸卻不依賴便利的XDMA設計之三:系統架構

應用環境中, 并提供簡易的操作方式實現數據的傳輸與存儲。 因此, 設計需要采用標準化接口, 實現盡可能低的資源占用率, 并具備 DMA 數據傳輸功能。

基于以上需求, 本

發表于 06-29 17:42

突破速度極限,定義未來視界 | 深視智能實時傳輸系列高速相機震撼上市!

Coaxpress2.0傳輸技術,滿畫幅滿幀率可達1920×1080@2250FPS,四通道帶寬達到50Gbit/s!產品優勢1體積小巧,靈活部署實時傳輸系列高速相機機身設計緊湊,

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現流片成功

我們很高興能在此宣布,Cadence 基于 UCIe 標準封裝 IP 已在 Samsung Foundry 的 5nm 汽車工藝上實現首次流片成功。這一里程碑彰顯了我們持續提供高性能車規級 I

乾瞻科技UCIe IP設計定案,實現高速傳輸技術突破

乾瞻科技UCIe IP設計定案,實現高速傳輸技術突破

評論