隨著高性能半導體需求的不斷增加,半導體市場越來越意識到“封裝工藝”的重要性。 順應發展潮流,SK海力士為了量產基于HBM(High Bandwidth Memory,高帶寬存儲器)的先進封裝產品和開發下一代封裝技術,盡力確保生產線投資與資源。一些曾經專注于半導體存儲器制造技術的企業也紛紛布局封裝技術領域,其投資力度甚至超過專攻此類技術的OSAT1(外包半導體組裝和測試)公司。這是因為,越來越多的企業深信封裝技術將會成為半導體行業及企業未來的核心競爭力。

1 OSAT(Outsourced Semiconductor Assembly and Test, 外包半導體組裝和測試):專門從事半導體封裝和測試業務的公司。

本文將以易于理解的語言來闡述封裝技術,幫助公眾不再因為復雜難懂而對這項技術望而卻步。文章將探究封裝技術的意義、作用和演變過程,并探討SK海力士封裝技術的發展歷程以及由此引發的當下對異構集成的關注。最后,本文也將介紹SK海力士的未來技術發展方向。

封裝技術的意義和作用

首先,我們來看封裝工藝的四項主要功能。第一也是最基本的,保護半導體芯片免受外部沖擊或損壞。第二,將外部電源傳輸至芯片,以確保芯片的正常運行。第三,為芯片提供線路連接,以便執行信號輸入和輸出操作。第四,合理分配芯片產生的熱量,以確保其穩定運行。近來,散熱(Heat Dissipation)或熱分配功能的重要性與日俱增。

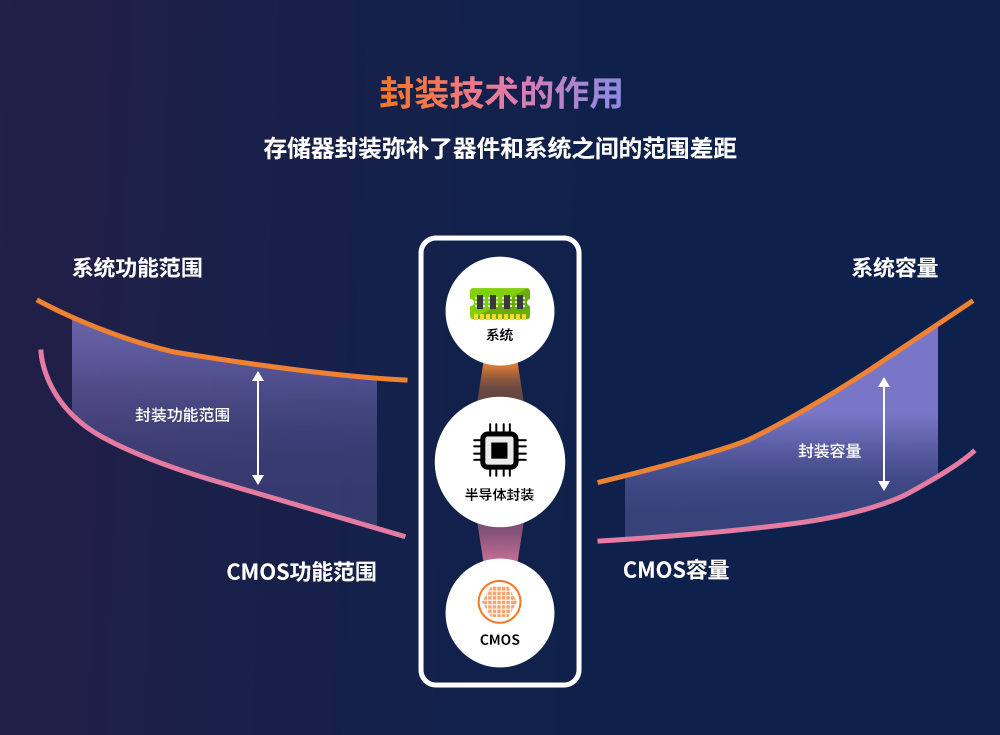

封裝的作用如圖1所示。例如,系統所需功能范圍與CMOS2(互補金屬氧化物半導體)提供的功能范圍之間存在顯著差距,但可通過封裝技術進行彌補。同樣,系統所需容量(Density)和CMOS提供的容量之間也存在差距,而這一問題也可借助封裝工藝加以解決,因為封裝工藝可提升密度(Density-up)從而提高CMOS的容量。換句話說,封裝技術充當著半導體器件(device)與系統之間的橋梁。因此,這種連接方法變得越來越重要。

2 CMOS(Complementary Metal Oxide Semiconductor, 互補金屬氧化物半導體):一種集成電路設計,應用于使用半導體技術的印刷電路板(PCB)。

圖1. 存儲器封裝彌補了器件和系統之間的范圍差距

封裝技術發展的三個階段:堆疊競爭、性能競爭、整合

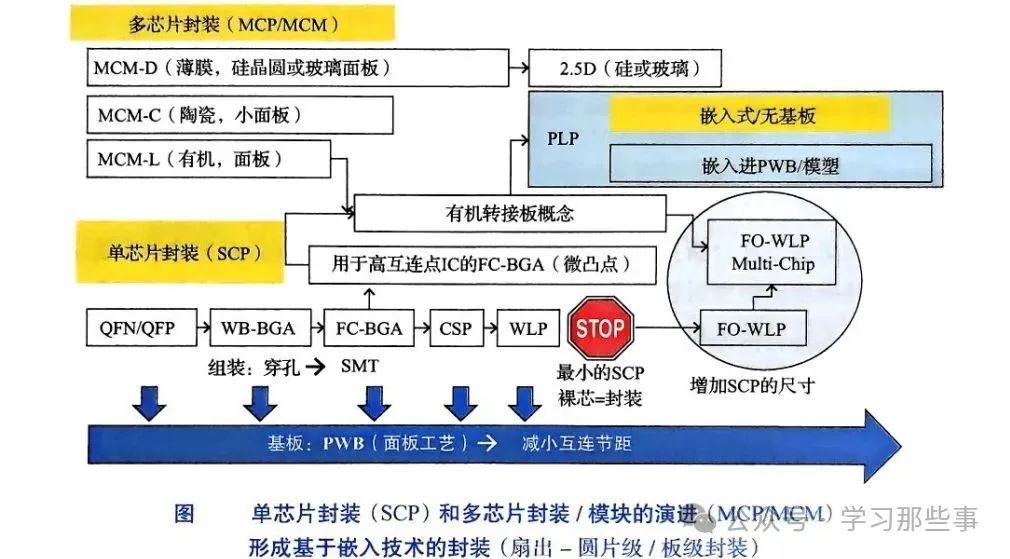

封裝技術的發展歷程可以劃分為三個主要時期。過去,一個封裝中只包含一個裸片。因此,封裝操作比較簡單,也沒有任何差異化因素,封裝技術的附加價值較低。然而,到了20世紀初,隨著向FBGA3(細間距球柵陣列)的轉變,多芯片堆疊封裝技術開始盛行。這一時期可以被稱為“堆疊競爭時期”。由于可以將芯片相互堆疊,因此封裝形式變得更加多樣化,還根據存儲器芯片的不同組合開發了各類衍生產品。MCP4(多芯片封裝)也出現在這一時期,該技術可以將DRAM和NAND集成在同一封裝中。

3 FBGA(Fine-pitch Ball Grid Array, 細間距球柵陣列):一種基于球柵陣列技術的集成電路表面貼裝型封裝(芯片載體)形式。其觸點更薄,主要用于系統級芯片設計。

4 MCP(Multi Chip Package, 多芯片封裝):通過在一個封裝外殼內垂直堆疊兩種或兩種以上不同類型存儲器半導體形成的產品。

第二個時期始于2010年之后,當時出現了一種利用芯片凸塊(Bump)的互連(Interconnection)方法。因此,運行速度和器件屬性裕度(Margin)發生了變化。這一時期可以稱為“性能競爭時期”,因為在2010年之前,封裝技術通常涉及金屬線連接,而凸塊的引入縮短了信號路徑(Signal Path),提高了速度。同時,采用TSV5(硅通孔)技術的堆疊方法大幅增加了I/O(輸入/輸出)數量,可連接10246 個wide I/O,即使在低電壓狀態下也可實現高速運行。在性能競爭時期,芯片性能依據封裝技術而異,這成為滿足客戶要求的重要因素。由于封裝技術可能影響企業的成敗,因此封裝技術的價值持續增長。

第三也是最后一個時期始于2020年,是在先前所有封裝技術的基礎上發展起來的。這一時期可以被稱為“整合時期”,需要借助技術將各類芯片集成到同一封裝內,還需要在整合系統時將多個部分連接至同一模塊。在這一時期,封裝技術本身已成為一種系統解決方案,可為客戶提供定制化的封裝解決方案,來實現小批量生產。從這一點來說,封裝技術將成為決定企業成敗的關鍵因素。

5 TSV(Through-Silicon Via, 硅通孔):一種在DRAM芯片內鉆數千個細孔并通過垂直貫通的電極將上下兩層的通孔連接在一起的互聯技術。

6 1,024:標準DRAM最多包含64個I/O,而HBM3最多包含1024個wide I/O。

圖2. 封裝技術發展帶來的變化

SK海力士封裝技術的發展歷程

直到堆疊競爭時期,SK海力士的封裝技術并未表現出顯著優勢;而隨著性能競爭時期的到來,SK海力士的封裝技術開始在市場中嶄露頭角。CoC(芯片內建芯片)7技術表現尤為突出,這項技術將凸塊互聯 (Bump Interconnection)與引線鍵合(Wire Bonding)相結合,在提高運行速度和降低成本方面實現了突破。如今,該技術已專門應用于SK海力士高密度模塊的生產和量產。SK海力士還開發了MR-MUF(批量回流模制底部填充)8技術并將其應用于HBM產品中。通過這項技術確保了HBM 10萬多個微凸塊互連的優良質量。此外,該封裝技術還增加了散熱凸塊的數量,同時由于其采用具有高導熱性的模制底部填充材料,與競爭產品相比具有更加出色的散熱性能。這項技術的應用鞏固了SK海力士在HBM市場的地位,并使SK海力士在HBM3市場占據領先地位。

7 CoC(Chip-on-Chip, 芯片內建芯片):是指在不使用TSV(硅通孔)技術的情況下,以電氣方式連接兩個(或以上)die的封裝技術。

8 MR-MUF(Mass Reflow Molded Underfill, 批量回流模制底部填充):將半導體芯片貼附在電路上,并在堆疊芯片時使用“EMC (Epoxy Molding Compound, 液態環氧樹脂模塑料”填充芯片之間或芯片與凸塊之間間隙的工藝。截至目前,NCF技術已經用于該工藝。NCF是一種在芯片之間使用薄膜進行堆疊的方法。MR-MUF與NCF相比,導熱率高出兩倍左右,對工藝速度和良率都有很大影響。

在如今的融合時期,SK海力士正積極發展混合鍵合(Hybrid Bonding)技術,這種技術采用Cu-to-Cu(銅-銅)鍵合9替代焊接。此外,SK海力士也在研究采用Fan-out RDL(扇出型重新分配層)技術10等各種封裝技術的方案。混合鍵合技術可以進一步縮小間距11,同時作為一種無間隙鍵合(Gapless Bonding)技術,在芯片堆疊時不使用焊接凸塊(Solder Bump),因此在封裝高度上更具優勢。此外,扇出型RDL技術適用于多個平臺,SK海力士計劃將該技術用于芯粒(Chiplet)12技術為基礎的集成封裝。線間距(Line Pitch)和多層(Multi-Layer)是扇出型技術的關鍵組成部分,SK海力士計劃到2025年將確保1微米以下或亞微米(Sub-micron)級水平的RDL技術。

9 Cu-to-Cu(Copper-to-Copper, 銅-銅)鍵合:封裝工藝的一種混合鍵合方法,可在完全不使用凸塊的情況下將間距縮小至10微米及以下。當需要將封裝內的die相互連接時,可在此工藝中采用銅-銅直接連接的方法。

10 RDL(Redistribution Layer, 重新分配層):集成電路上形成的額外金屬布線層,旨在重新排列I/O焊盤,將焊盤重塑到所需位置,以便于在必要時操作焊盤。例如,芯片中心的凸塊陣列可重新分配到靠近芯片邊緣的位置。重新分配焊盤有助提高接觸密度,并實現后續封裝步驟。

11 間距:互連線之間中心到中心的最小距離

12 芯粒:該技術使用控制器或高速存儲器等將芯片分開,并將它們作為單獨晶圓進行制造,最后在封裝工藝中對它們進行重新連接

圖3. SK海力士最新封裝技術

封裝技術將成為提供整體系統解決方案的重要手段,其功能不再局限于原始的芯片保護和電源供應等功能。在不久的將來,各公司將依賴封裝技術助力其成為半導體行業的領軍者。幾年前,東亞地區一家大型晶圓代工企業使用集成式扇出型(Integrated fan-out, InFO)封裝技術建立起全新的系統級封裝(System-in-Package, SiP)業務,同時擴大了晶圓代工銷售業務范圍。就像這家晶圓代工企業以生產控制器而聞名,SK海力士以生產HBM等高性能半導體存儲器著稱。SK海力士在整合時期進一步加強異構集成和扇出型RDL技術等先進封裝技術。不僅作為存儲器IDM(Integrated Device Manufacturer, 垂直集成制造)公司引領業界,進一步成為引領未來半導體儲存器行業的“解決方案提供者(Solution Provider)”。

文章來源:SK海力士

審核編輯 黃宇

-

半導體

+關注

關注

339文章

30725瀏覽量

264041 -

封裝

+關注

關注

128文章

9248瀏覽量

148612 -

異構

+關注

關注

0文章

47瀏覽量

13544

發布評論請先 登錄

多Chiplet異構集成的先進互連技術

奧芯明:AI驅動半導體產業迎來“異構集成”新紀元,先進封裝成破局關鍵

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

智聚芯能,異構互聯,共贏AI時代機遇——芯和半導體領銜揭幕第九屆中國系統級封裝大會

半導體先進封測年度大會:長電科技解讀AI時代封裝趨勢,江蘇拓能半導體科技有限公司技術成果受關注

現代集成電路半導體器件

功率半導體器件——理論及應用

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

AI時代,封裝材料如何助力實現更優的異構集成?

異構集成時代半導體封裝技術的價值

異構集成時代半導體封裝技術的價值

評論