上月初,英特爾攜手日月光半導體(ASE)、AMD、Arm、谷歌云、Meta、微軟、高通、三星和臺積電等廠商發起UCIe產業聯盟(通用芯粒高速互連),意欲推行開放的晶片間互連標準。可以說UCIe的出現,代表著全球半導體產業已經進入到成熟的產業階段,但因為標準體系涉及到產業各環節間的協調和產業推廣,UCIe真正被行業認可和開始實施預計還需要比較長的時間。

目前大陸已經有第一批企業率先加入了該組織,與UCIe產業聯盟其他成員共同致力于UCIe 1.0版本規范和新一代UCIe技術標準的研究與應用,這是值得高興的。但就是在該聯盟熱度持續不下的時候,我們也應該沉下心來思考這對技術研發與生態發展的影響。打鐵還需自身硬,在聯盟標準熱度之下,除了加入標準獲得話語權,芯片研發企業還應該冷靜打磨自身,潛心研發攻克核心技術,為國內自主可控技術突破作出切實的貢獻。

從產業角度來看,Chiplet目前主要以英特爾為代表等具有強大設計能力的公司可以做,UCIe產業聯盟成員包括日月光、超威(AMD)、Google Cloud(谷歌)、臉書母公司Meta、微軟、高通、三星和臺積電等多家業者,包括半導體、封裝、IP供應商、晶圓代工廠和云端服務提供廠商,基本可以形成一個小的產業生態閉環,這將進一步提高各產業環節的集中度,進一步鞏固了龍頭優勢,是否會真正利好半導體產業的發展也是存疑的。

尤其需要注意到英特爾在美國半導體產業中扮演的敏感角色,在此特定背景下,我們不希望看到UCIe會成為政治化的工具。國內方面,我們要繼續走好自己的路,加速國產化的同時,我們要做好應對一切沖擊的準備。一方面,UCIe提供了一種可參考的產業平臺機制,我們亦可以通過組建內部產業聯盟的方式來優化產業分工,進一步加快國內產業發展,提高國內半導體產業對于沖擊的耐受力。

就這一點,早在2020年國內舉辦的全球硬科技創新大會上,中國科學院院士/圖靈獎得主姚期智、西安市副市長馬鮮萍、芯動科技CEO敖海、紫光存儲總裁任奇偉就共同啟動了中國Chiplet產業聯盟。并提出該聯盟將致力于集聚人工智能、集成電路等領域產、學、研、金各類資源,搭建開放創新平臺,縮短芯片設計周期、降低芯片設計成本,解決我國高質量發展進程中相關“卡脖子”技術難題。

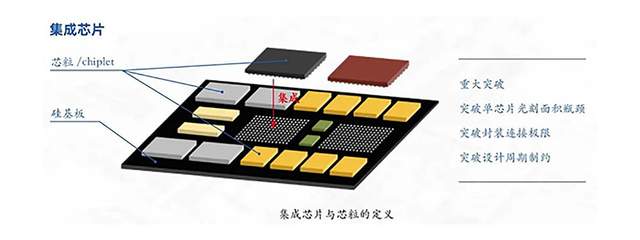

另一方面,我們可以盡早開發出標準化的自主Chiplet技術,為高性能CPU/GPU/NPU芯片的異構實現提供保障。就我所知,目前國內真正推出自主Chiplet技術的有芯動科技,我們來看看它推出的國內第一款自主Chiplet技術——Innolink? Chiplet。據悉,Innolink? Chiplet是第一款國產自主研發物理層兼容UCIe標準的IP解決方案。

據公開資料介紹,芯動在Chiplet技術領域積累了大量的客戶應用需求經驗,并且和臺積電、intel、三星、美光等業界領軍企業有密切的技術溝通和合作探索,在近幾年各大巨頭推行自己的Chiplet互聯標準時,芯動科技也奮起直追緊隨其后,兩年前就開始了Innolink? 的研發工作,率先明確Innolink B/C基于DDR的技術路線,并于2020年的Design Reuse全球會議上首次向業界公開Innolink A/B/C技術,率先推出自主研發的Innolink? Chiplet標準并實現授權量產。

Innolink? Chiplet具有自主知識產權,填補了國內的異構集成技術空白,打破了國外核心技術壟斷,成功應用于國產GPU及其他高性能計算芯片,為國產高性能芯片的發展提供了一條新的道路。得益于正確的技術方向和超前的布局規劃,Innolink? 的物理層與UCIe的標準保持一致,成為國內首發、世界領先的自主UCIe Chiplet解決方案。

Innolink A/B/C實現方法

看到Innolink? Chiplet實實在在的硬數據,我們確實驚訝于國內已在Chiplet領先技術領域實現了領先超越。盡管芯動科技在消費者領域并不為人熟知,但在很多B端企業中已頗具盛名,服務了數百家知名企業,擁有超過200次的流片記錄、逾60億顆授權量產芯片。Innolink? Chiplet讓我們看到了市場熱度之下國內半導體耕耘者們默默無聞、腳踏實地的努力,也看到了國產半導體技術的更多未來。

總的來說,Chiplet發展需要整個半導體產業鏈的協同分工,從芯片設計、EDA工具、晶圓制造到封裝測試,需要統一的標準和工藝升級,這需要時間探索和協作,不斷地迭代前進。在當前的國際市場背景下,國產自主可控、可以持續迭代和發展的Chiplet技術顯得尤為重要。芯動科技推出的自主Chiplet技術已成功運用于國產第一款高性能GPU“風華1號”,提升了產品性能和帶寬,成為國產芯片里走在最前列的異構集成設計的實踐者,期待更多本土企業和技術的突破,加快實現國產芯片自主可控。

審核編輯:符乾江

-

chiplet

+關注

關注

6文章

495瀏覽量

13603 -

UCIe

+關注

關注

0文章

53瀏覽量

2016

發布評論請先 登錄

多Chiplet異構集成的先進互連技術

得一微電子受邀出席第四屆HiPi Chiplet論壇

UCIe協議代際躍遷驅動開放芯粒生態構建

解構Chiplet,區分炒作與現實

CMOS 2.0與Chiplet兩種創新技術的區別

新思科技UCIe IP解決方案實現片上網絡互連

技術資訊 I 完整的 UCIe 信號完整性分析流程和異構集成合規性檢查

從技術封鎖到自主創新:Chiplet封裝的破局之路

Chiplet與先進封裝設計中EDA工具面臨的挑戰

奇異摩爾受邀出席第三屆HiPi Chiplet論壇

Chiplet:芯片良率與可靠性的新保障!

UCIe聯盟熱之下的思考,Chiplet技術本身更值得關注

UCIe聯盟熱之下的思考,Chiplet技術本身更值得關注

評論