啟動 mqSemi 引入了單點源 MOS (S-MOS) 單元設計,適用于基于功率 MOS 的設備。S-MOS 技術采用 Silvaco Victory 工藝和器件軟件在 1200V SiC MOSFET 結構上采用和實施。提供了一整套靜態和動態結果,用于將 S-MOS 與使用平面和溝槽 MOS 單元設計的標準SiC MOSFET 2D 結構進行比較,如參考文獻中所定義。

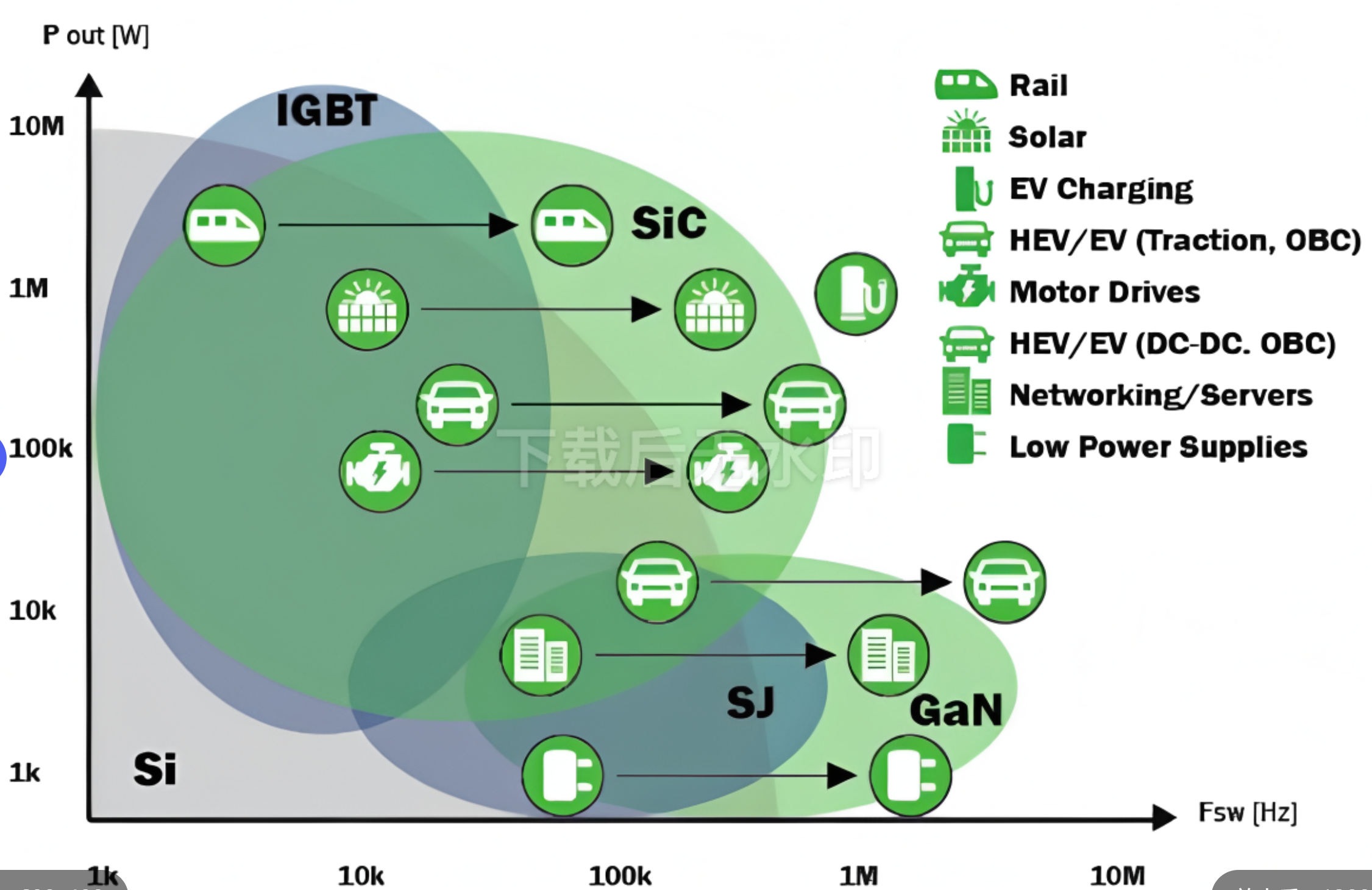

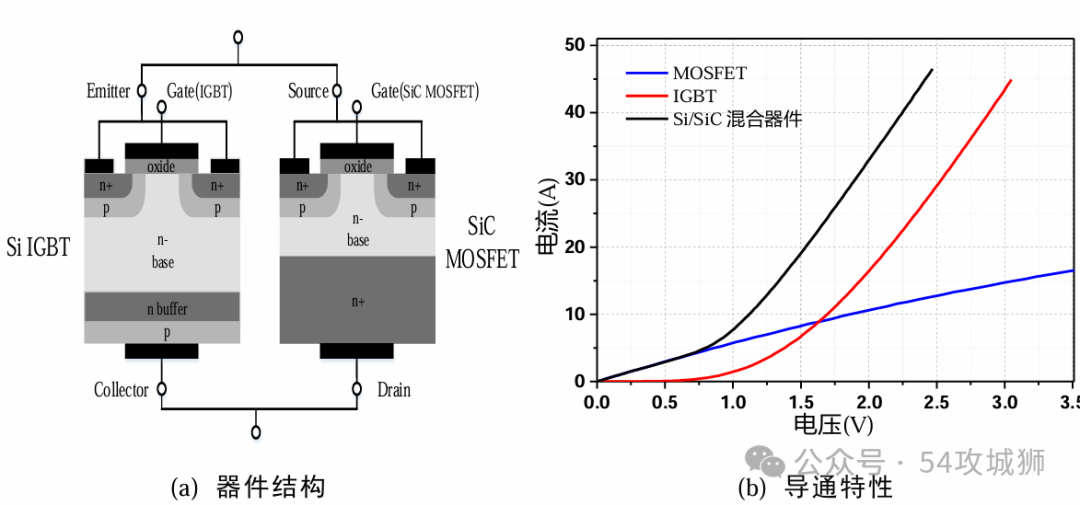

隨著時間的推移,MOS 單元制造和設計平臺顯著提高了功率 MOSFET 和絕緣柵雙極晶體管 (IGBT) 等硅基功率器件的性能。在這兩種器件中,平面或溝槽 MOS 單元都以蜂窩或線性模式分組。

硅基 MOS 器件的結果可用于制造需要高單元封裝密度的 SiC 功率 MOSFET。近年來,人們提出了先進的 3D 設計方法來改進設備的靜態和動態特性。利用多維通道寬度來提高單元密度并最小化 RDS(通態電阻)的低壓 FinFET 單元架構連接到這些 3D 拓撲 (ON)。

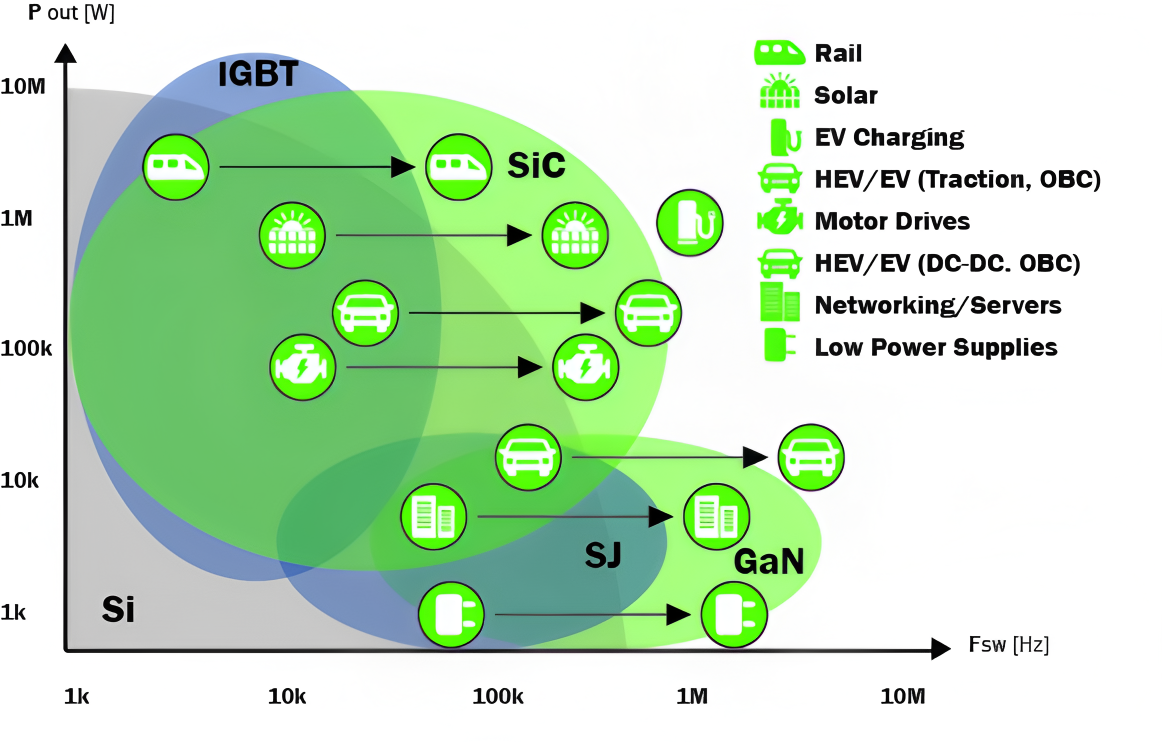

采用 SiC 作為功率器件材料的優點之一是能夠使用許多眾所周知的硅器件原理和制造程序。基本器件拓撲包括垂直肖特基二極管或垂直功率 MOSFET(在通過 JFET 適當分流后)。

因此,許多用于保持硅器件長期穩定性的工藝也可以用于保證 SiC 器件的長期穩定性。然而,仔細觀察發現,基于 SiC 的器件需要比基于 Si 的器件進行額外且不同的可靠性測試,例如材料的獨特性能和缺陷、更大的帶隙和更高的電場,特別是在結終端區域,以及在更高的溫度和開關頻率。

S-MOS 電池概念

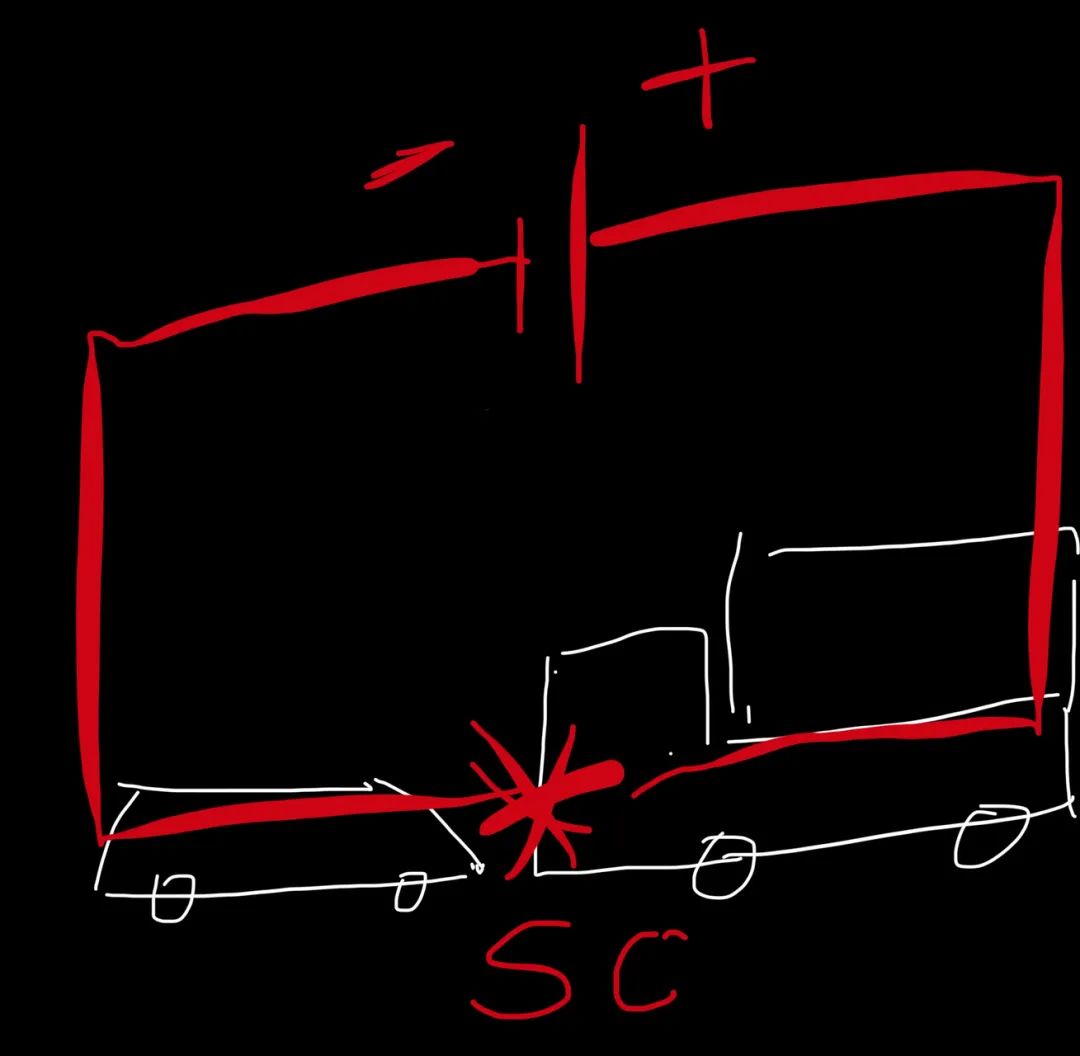

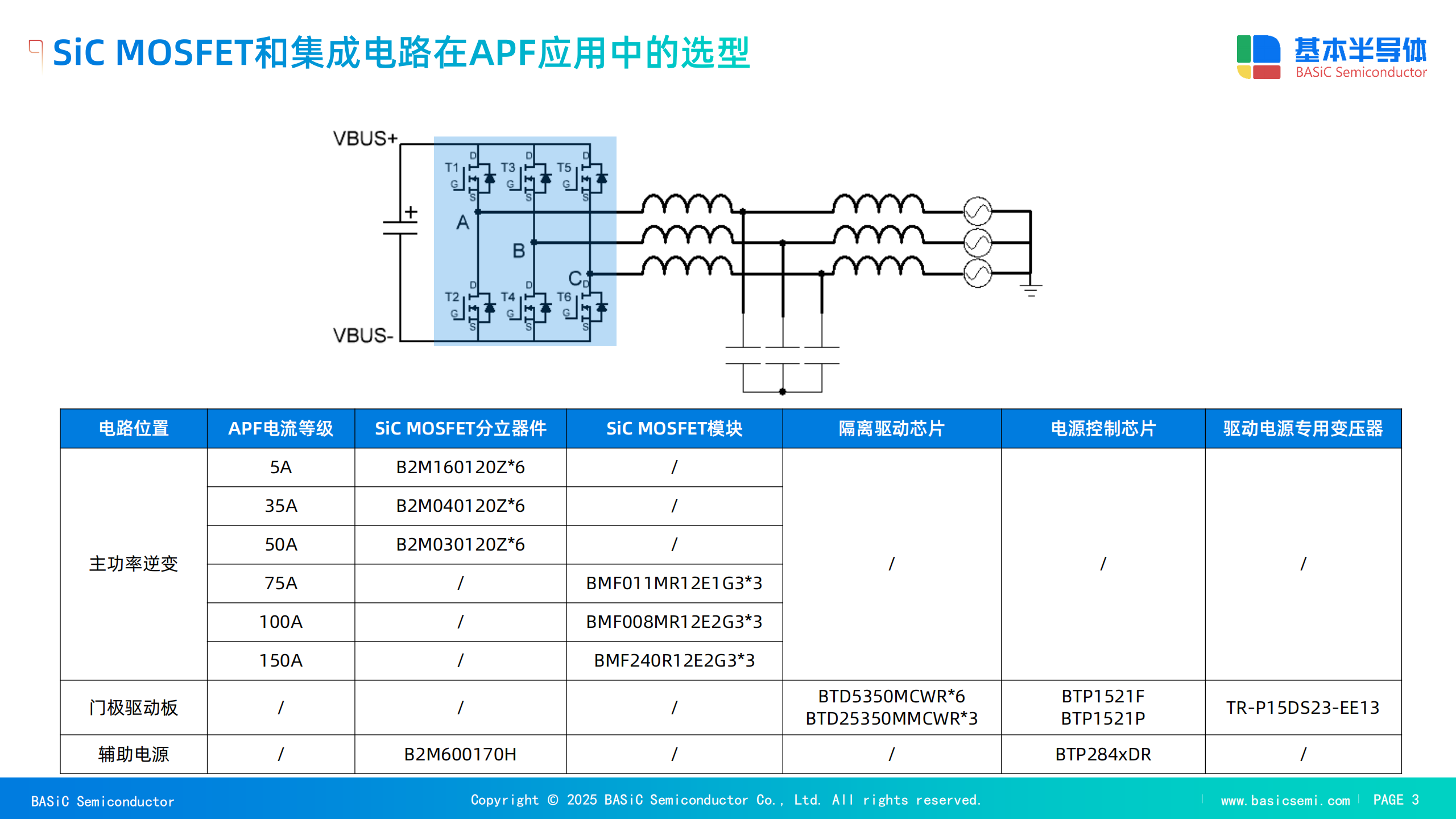

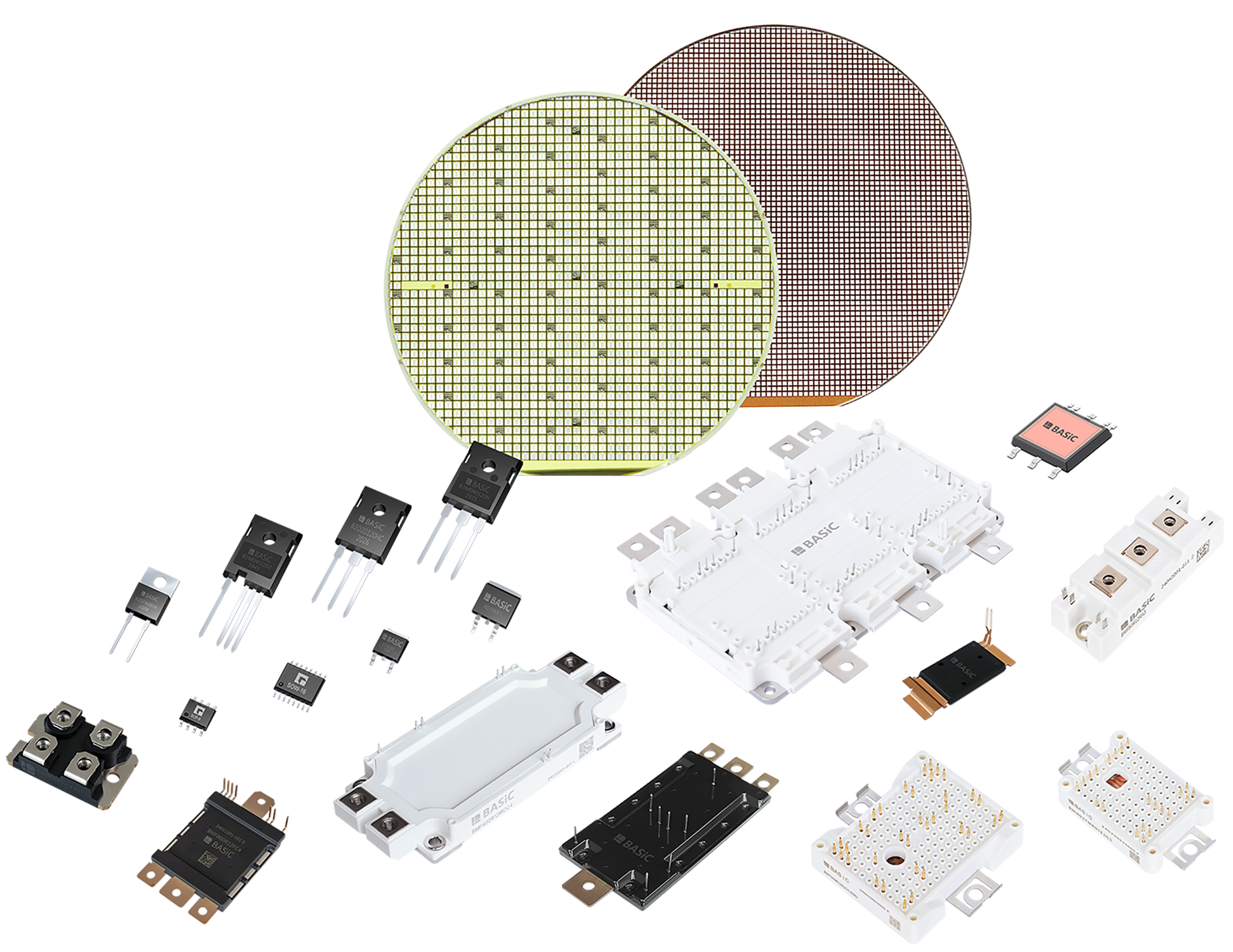

與這種三維結構趨勢相吻合的是由初創公司mqSemi開發的“Singular Point Source”MOS單元概念(也稱為S-MOS)。mqSemi 由 Munaf Rahimo 和 Iulian Nistor 創立,總部位于瑞士,致力于開發先進的功率半導體概念,解決用于電動汽車、汽車和可再生能源等應用的下一代電力電子系統。mqSemi 在過去兩年中申請了 20 多項專利,已經進行了大量的模擬,現在已準備好進入原型制作階段。mqSemi 團隊在 IGBT 方面獲得的多年經驗和知識,對解決碳化硅 MOSFET 的關鍵問題有很大幫助;例如降低損耗、提供穩健的短路模式和阻斷行為、柵極驅動控制和高頻振蕩。

mqSemi 的發言人 Rahimo 和 Nistor 表示:“我們相信,對于一個可持續發展的世界,我們將需要基于高效、緊湊、可靠和具有成本效益的功率半導體器件的應用,這些器件是技術領先和以創新為中心的。”

S-MOS 的好處是雙重的:一方面,它使用獨特的方法精心定義了總通道寬度,也稱為通道面積;另一方面,它可以實現更高的 MOS 單元封裝密度。此外,S-MOS 概念可以在 MOSFET 和 IGBT 上實現,從而提高開關性能,同時實現更高的效率和更低的整體損耗。

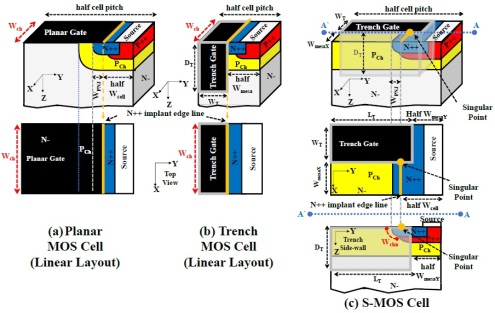

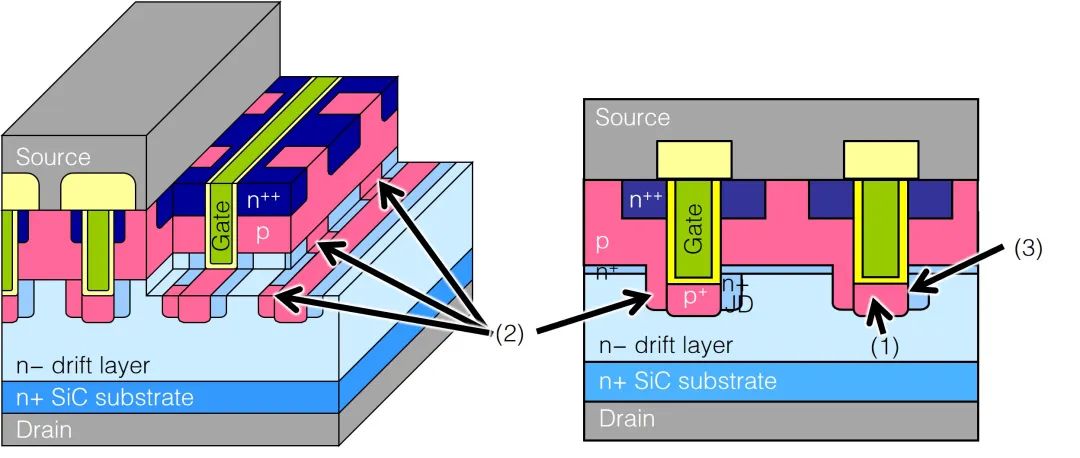

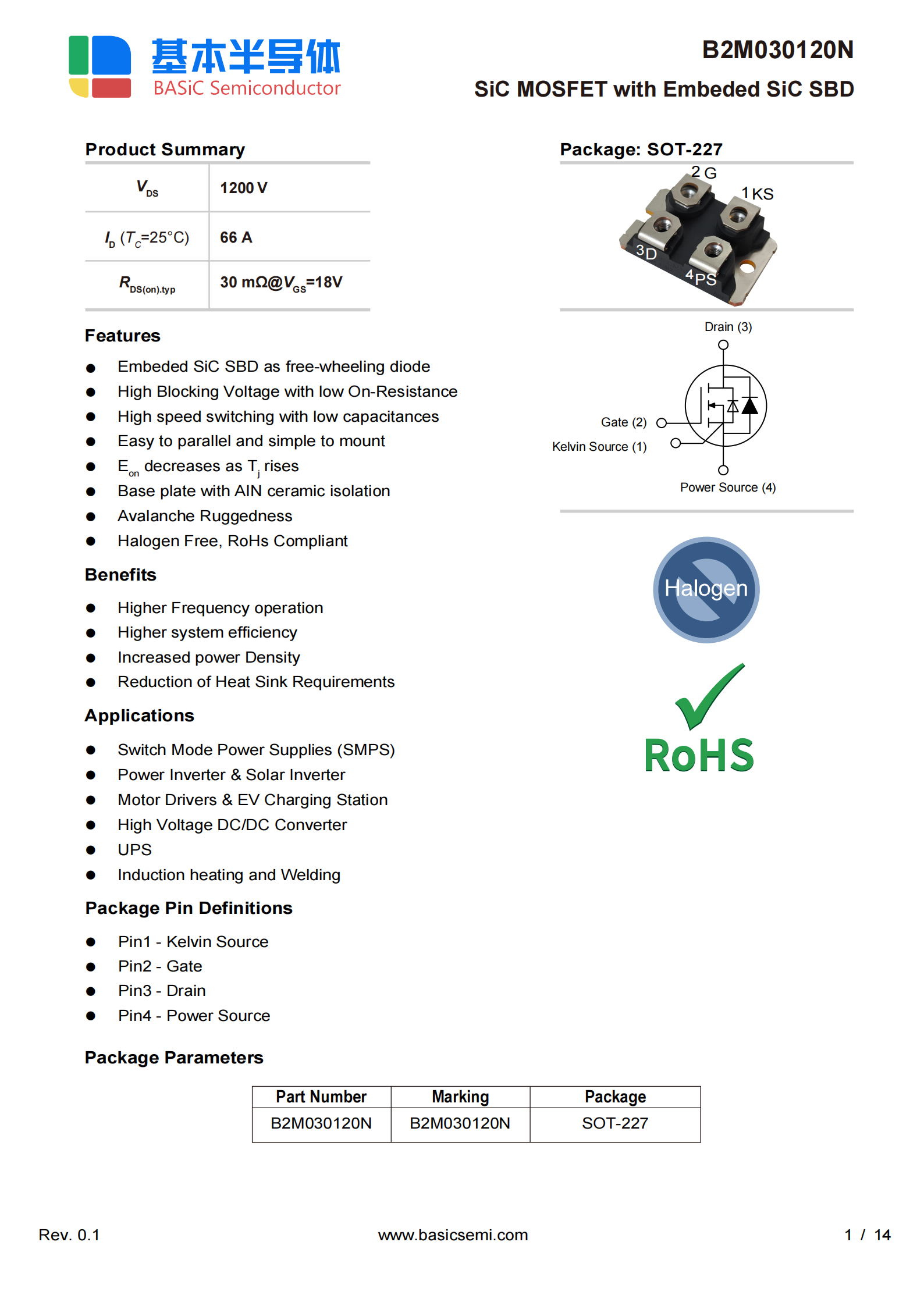

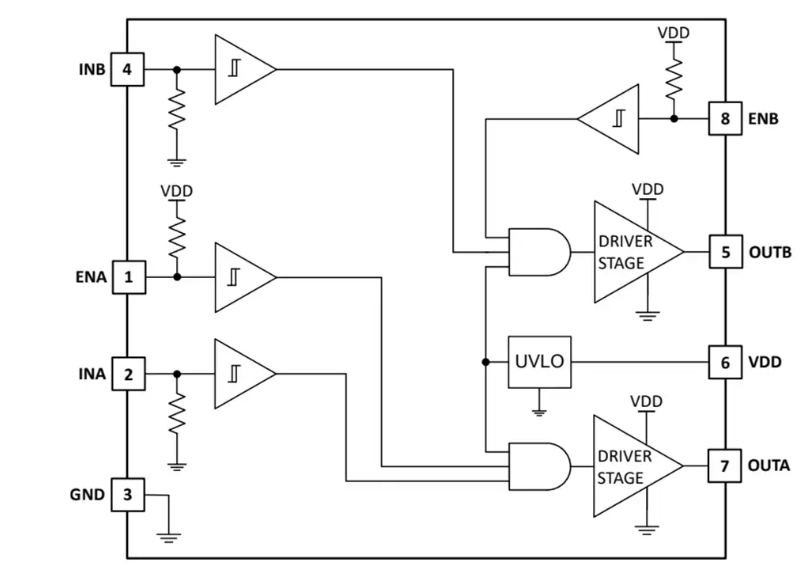

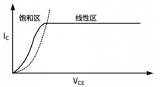

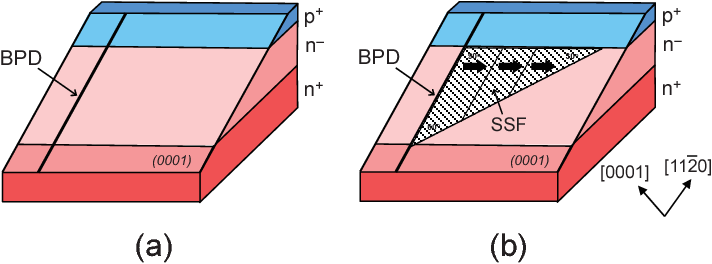

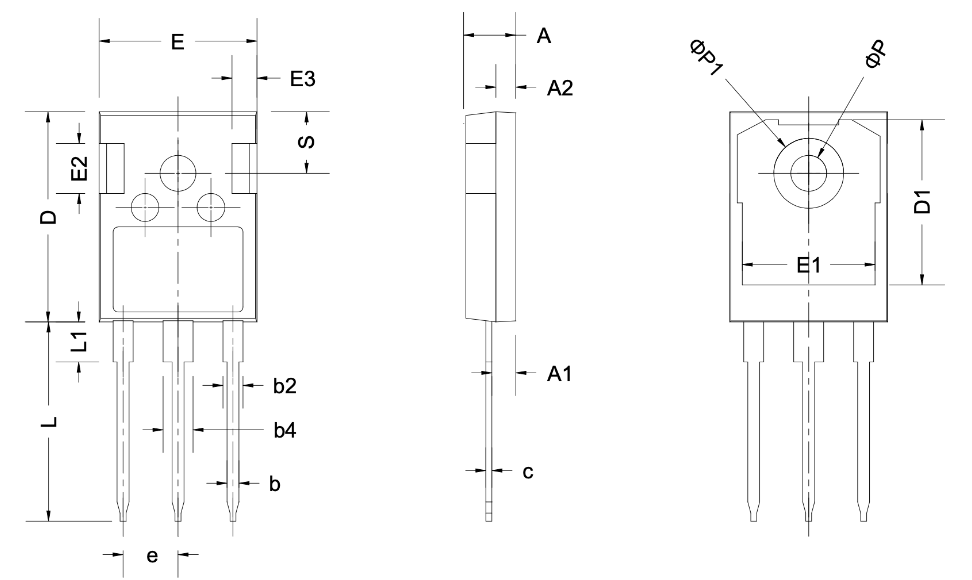

S-MOS 單元與標準平面單元和溝槽 MOS 單元的不同之處在于如何設計每個器件面積的總溝道寬度(W ch參數)。如圖 1a 和圖 1b 所示,平面或溝槽 MOS 單元的溝道寬度 W ch定義為 N++ 源極周圍的總外圍距離,它還取決于 MOS 單元排列的幾何形狀(線性或蜂窩布局設計)。S-MOS 單單元溝道寬度 W ch,如圖 1c 所示,由 N++ 源極和 P溝道結 W PNJ長度的小尺度尺寸定義。通過將這個小的幾何特征定位在溝槽側壁上,預定的單位溝道長度 W chn提供。對于 S-MOS,N++ 和 P通道輪廓類似于平面單元的輪廓,但位于溝槽側壁上。因此,總溝道寬度取決于每個芯片的門控溝槽側壁的總數。如圖 1c 底部所示(紅色虛線),N++/P通道結的形狀可以近似為“四分之一圓”,單個溝槽的 W chn尺寸約為 150-300 nm側壁。給定芯片面積的總 W ch可以作為所有溝槽側壁上所有 W chn的總和獲得。

圖 1:源 MOS 單元概念

The S-MOS concept has been demonstrated by means of 2D and 3D TCAD simulations conducted on 1200V SiC MOSFETs, including the S-MOS and reference planar and trench structures.

“During the simulation, we found a very special feature, that we were not expecting, on the side-wall of a trench, where we could get the so called channel width which defines the total channel density which was something based on a diffusion profile”, said the speaker at mqSemi.

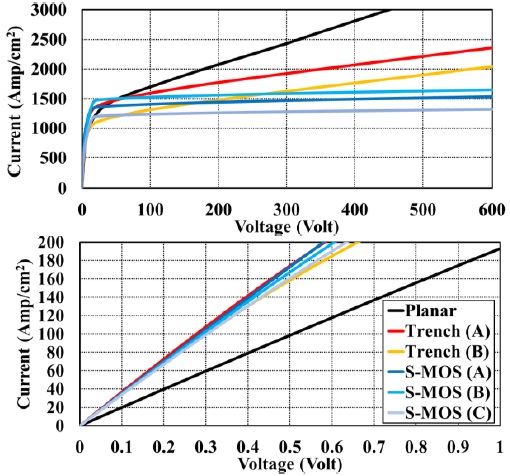

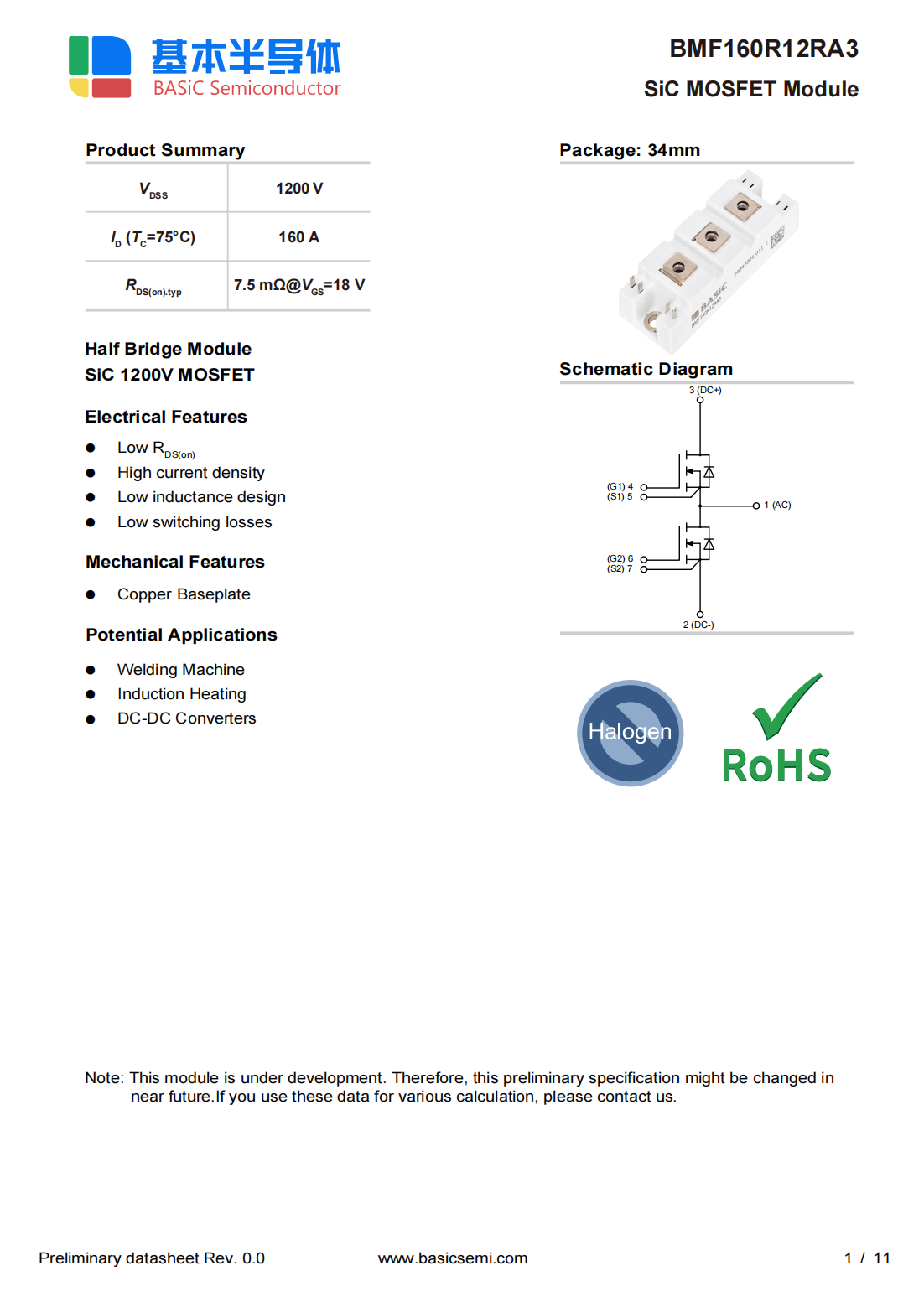

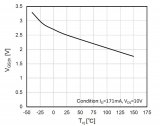

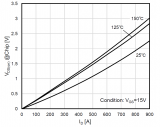

The simulation was peformed on a 1200V SiC MOSFET because the static losses, measured by Rds(on), are not difficult to assess. The same technology can be applied to different voltage classes, as well. Static and mixed mode inductive load dynamic simulations were carried for all device structures (S-MOS, Trench and 2D Planar) which were scaled for a total active area of 1cm2. The output voltage-current characteristics obtained with the simulation are shown in Figure 2; the upper image refers to a voltage range up to 600V, while the lower image is a zoom-in up to 1V at Vgs=15V and 150°C. The S-MOS concept has provided low Rdson levels (around 3 mΩ-cm2 在 150°C),類似于溝槽電池。然而,如圖 2 所示,與其他參考模型相比,S-MOS 還提供平坦的飽和電流。

圖 2:1.2kV SiC MOSFET 輸出曲線,Vgs=15V,150°C

“我們發現我們有更好的切換可控性,這就是進入第三維的全部想法。與溝槽電池相比,我們獲得了大大降低的開關損耗,并且我們有更多的設計自由度來進一步優化它并獲得更高的電池密度”,mqSemi 的發言人說。

在 150°C 下對所有器件的短路電流進行了仿真,顯示了 S-MOS 如何表現出更少的短溝道效應并改善了傳導損耗和短路性能之間的權衡。盡管 S-MOS 概念仍需要進一步的設計優化,但所展示的性能非常有前途,在 mqSemi,他們認為已經為下一階段做好準備,即原型設計。

審核編輯:劉清

電子發燒友App

電子發燒友App

評論