揚杰科技干貨分享-如何用雙脈沖測試更好的表征SiC MOS動態能力?

引言

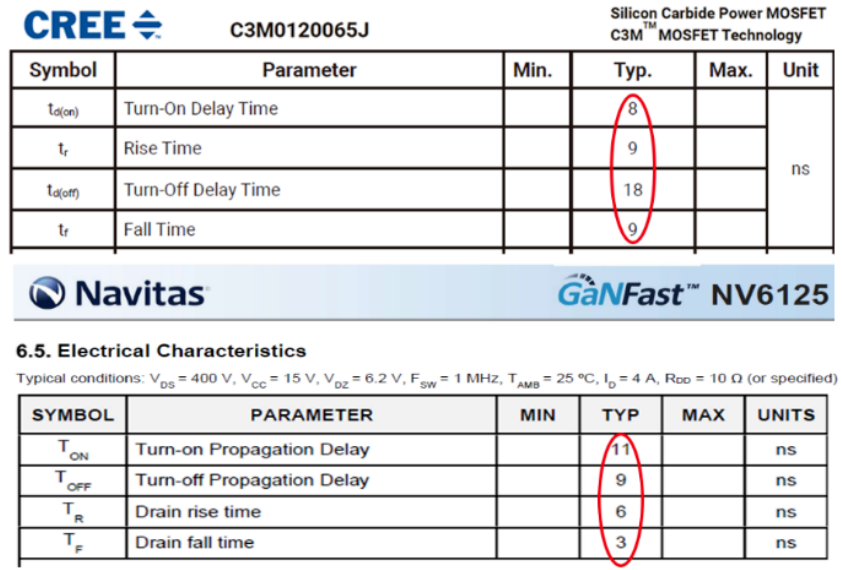

隨著碳化硅(SiC)MOS產品的迭代發展,SiC MOS相比于Si IGBT的高頻應用潛力得到越來越多工程師的關注。這是由于在開關過程中,得益于SiC MOS的高電子飽和漂移速度,載流子能迅速在導通與截止狀態間切換,從而顯著減少開關時間。與此同時,SiC MOS這一單極型器件在續流過程中沒有p型襯底的電荷存儲,使得反向恢復損耗低于Si IGBT這一雙極性器件,SiC MOS的反向恢復電荷僅為同規格硅器件的十分之一左右,在應用中可以選擇SiC MOS的體二極管作為續流二極管,進一步提升系統的功率密度并降低成本。

為了更好的挖掘SiC MOS的高頻應用潛力,業界逐步將雙脈沖測試(DPT)作為評估SiC MOS動態特性的標準方法,下面將介紹SiC MOS雙脈沖測試時的三個關鍵技術節點。

雙脈沖測試平臺

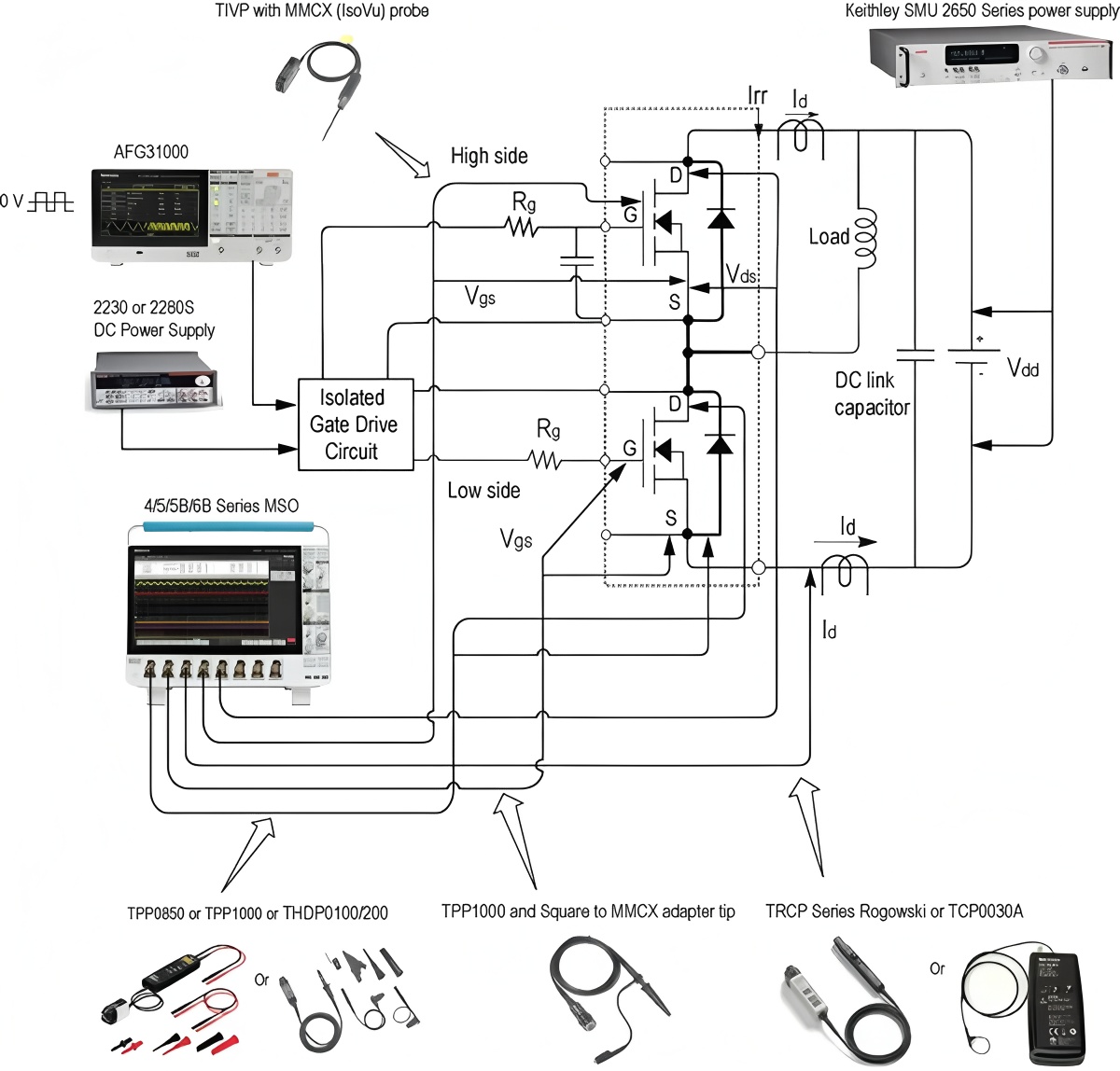

圖1. 雙脈沖測試電路的拓撲結構

一個典型的半橋感性負載雙脈沖測試電路拓撲如圖1所示,包括母線電源VBUS、母線電容CBUS、感性負載電感LLoad、陪測管、被測管、柵極驅動VG、柵極負載RG、電流探頭(通常為羅氏線圈或同軸電阻)以及走線和元器件引入的雜散電感。由于上橋的源端浮空,通常將陪測管保持被動續流狀態放置在上橋,被測管放置在下橋受VG控制,保持被測管的源極接地。測試過程中VG發射兩個脈沖,第一個脈沖T1的脈寬較長,感性負載電流IL線性上升,其計算公式為:ILoad≈(VBUS*T1)/LLoad。死區時間和第二個脈沖的脈寬較短,測試只需關注第一個脈沖的關斷波形和第二個脈沖的開啟波形。

探頭時間偏移

在進行雙脈沖測試時,示波器使用2個電壓探頭分別監控柵極電壓VG和漏極電壓Vds,電流探頭監控負載電流。通常同型號的兩個電壓探頭之間校準較為容易,可以通過測試同一個脈沖信號計算信號延遲,再補償信號差值,然而電流探頭與電壓探頭之間測量較為容易出現時間偏移,偏移量大概在幾個ns到幾十個ns,這樣微小的差距將導致測量的巨大誤差。圖2為一組SiC MOS的實測數據,兩組數據的電流數據偏差10ns,校準前的Eon=3618.4uJ、Eoff= 894.5uJ。校準過程將柵源電壓達到閾值電壓Vth的時刻和電流抬起的時刻對齊作為校準標準,將整體電流數據向前推移10ns,校準后的Eon=3218.7uJ、Eoff=1326.6uJ。因此,探頭時間偏移將對器件的性能判斷產生巨大的干擾,探頭時間偏移需要定期矯準。

(1)器件開啟過程

(2)器件關斷過程

圖2. 探頭時間偏移對雙脈沖測試的影響

柵極電阻

柵極電阻的選擇也將極大的影響測試結果,SiC MOS的規格書通常將Rg為2Ω左右作為測試標準,測得的開關損耗通常很低,但在實際應用中這樣小的Rg無法應用于實際工況。選擇更小的Rg可以提高柵極驅動向柵極電容的充電電流,加快SiC MOS溝道形成速度從而提高功率回路的di/dt,使得電壓和電流波形交疊的區域變窄,進而降低開關損耗。然而過高的di/dt會導致電流過沖,這也對器件的安全工作區(SOA)提出了挑戰。圖3(1)展示了Rg=2.4Ω、IL=40A時的開關波形,測得損耗Eon=724.9 uJ,Eoff=162.5 uJ,過沖電流在極短的時間內爬升至123A,達到了負載電流的三倍。圖3(2)展示了Rg=20Ω、IL=40A時的開啟波形,過沖電流被抑制到了57A,損耗Eon=2208.5 uJ,Eoff=928.4 uJ。綜上所述,Rg的選擇需要在電流過沖和開關性能之間折中選擇,或是針對客戶應用需求來設置。

(1)器件開啟過程

(2)器件關斷過程

圖3. 柵極電阻對雙脈沖測試的影響

雜散電感

雜散電感對開關損耗的影響是至關重要的,同樣也是容易被忽略的。這里描述的雜散電感不僅來自于測試拓撲,同樣來自于封裝引腳。在SiC MOS的柵極、源極和漏極都存在雜散電感,其中以源極的影響最大。以TO-247-3L封裝產品為例,其柵驅動回路和功率回路之間存在一個共源極電感,當較大的di/dt流經雜散電感會產生電位變化,使得源極電位浮動,最終反饋至柵驅動回路導致開關速度變慢。而TO-247-4L封裝產品為柵極引入了開爾文回路,將共源極電感旁路來降低開關損耗。

盡管TO-247-4L封裝已經在結構層面顯著降低了雜散電感的影響,但插件式封裝的引腳自身引入的雜散電感仍不可忽略。為了研究這一影響,分別用兩種插接方式測試了同一顆TO-247-4L器件,第一組測試器件完全插接至PCB測試板中,另一組測試則保留部分器件的引腳未插接至PCB測試板。兩組測試的測試結果如圖4所示,完全插接器件測得損耗Eon=3043uJ、Eoff=1145.9uJ,未完全插接器件測得損耗Eon=3219.2uJ、Eoff=1256.6uJ,未完全插接器件的開關損耗顯著提高。因此測試人員需要盡量規范化插接,保證測試的重復性。

為了更深入的量化分析測試結果,可以通過雙脈沖曲線的SiC MOS提取雜散電感。開啟過程中,漏源電流上升的電流變化率dIL/dt基本為定值,這會在漏源兩端產生了一個相反的感應電勢,致使Vds波形出現一段電壓下降△VL,通過這一現象即可大致估算測試回路的雜散電感L=△VL/(dIL/dt),完全插接器件測得雜散電感為31.1nH,未完全插接器件測得雜散電感為40.3nH,正是這9.2nH的差距導致了如此大的開關損耗差距。如果希望更進一步降低損耗,可以選擇貼片式產品如TOLL封裝,從而最大限度的消除插件式引腳帶來的雜散電感影響。

(1)器件開啟過程

(2)器件關斷過程

圖4. TO-247-4L引腳對雙脈沖測試的影響

小結

本文系統地闡述了如何利用雙脈沖測試來更精確地表征SiC MOS的動態開關能力,如果希望準確評估SiC MOS的動態性能,不能僅依賴規格書的標準數據,必須關注測試過程中的三個關鍵技術細節:

1、探頭時間偏移:電壓與電流探頭間的微小延時(納秒級)會顯著干擾開關損耗的測量結果,可以以器件的閾值電壓為基準進行定期校準,以確保數據的準確性。

2、柵極電阻選擇:柵極電阻(Rg)的取值直接影響開關速度、損耗和電流過沖。較小的Rg能降低開關損耗,但會引發嚴重的電流過沖,威脅器件安全;較大的Rg則能抑制過沖,但會增大損耗。因此,在實際應用中需要在開關性能與可靠性之間進行折衷選擇。

3、雜散電感管理:測試回路和器件封裝(尤其是源極)中的雜散電感會通過產生感應電壓負反饋,減緩開關過程,增加開關損耗,TO-247-4L在應用中更具有動態性能優勢。與此同時,改變TO-247-4L封裝器件的不同插接方式也十分重要,僅9.2nH的雜散電感差異即可導致損耗的顯著變化。

-

IGBT

+關注

關注

1289文章

4355瀏覽量

263626 -

MOS

+關注

關注

32文章

1749瀏覽量

100972 -

SiC

+關注

關注

32文章

3796瀏覽量

69697 -

脈沖測試

+關注

關注

1文章

38瀏覽量

11673 -

揚杰科技

+關注

關注

1文章

158瀏覽量

12352

原文標題:干貨分享|?如何用雙脈沖測試更好的表征SiC MOS動態能力?

文章出處:【微信號:yangjie-300373,微信公眾號:揚杰科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

碳化硅 (SiC) MOSFET 雙脈沖測試(DPT):探頭干擾排除與真實波形獲取技術研究

普科PKDV5151高壓差分探頭:光伏逆變器SiC MOSFET雙脈沖測試的優選工具

碳化硅MOS管測試技術及儀器應用(上)

《電子發燒友電子設計周報》聚焦硬科技領域核心價值 第38期:2025.12.1--2025.12.5

樂高化組裝,一鍵式測試 | 云鎵GaN自動化雙脈沖測試平臺

SiC-MOS與IGBT抗短路能力對比

同軸分流器SC-CS10在功率器件(IGBT、MOSFET等)動態雙脈沖測試中的應用

如何用雙脈沖測試更好的表征SiC MOS動態能力?

如何用雙脈沖測試更好的表征SiC MOS動態能力?

評論