傾佳電子寬禁帶時(shí)代下的效率優(yōu)化:SiC MOSFET橋式拓?fù)渲型秸骷夹g(shù)的必然性與精確定量分析

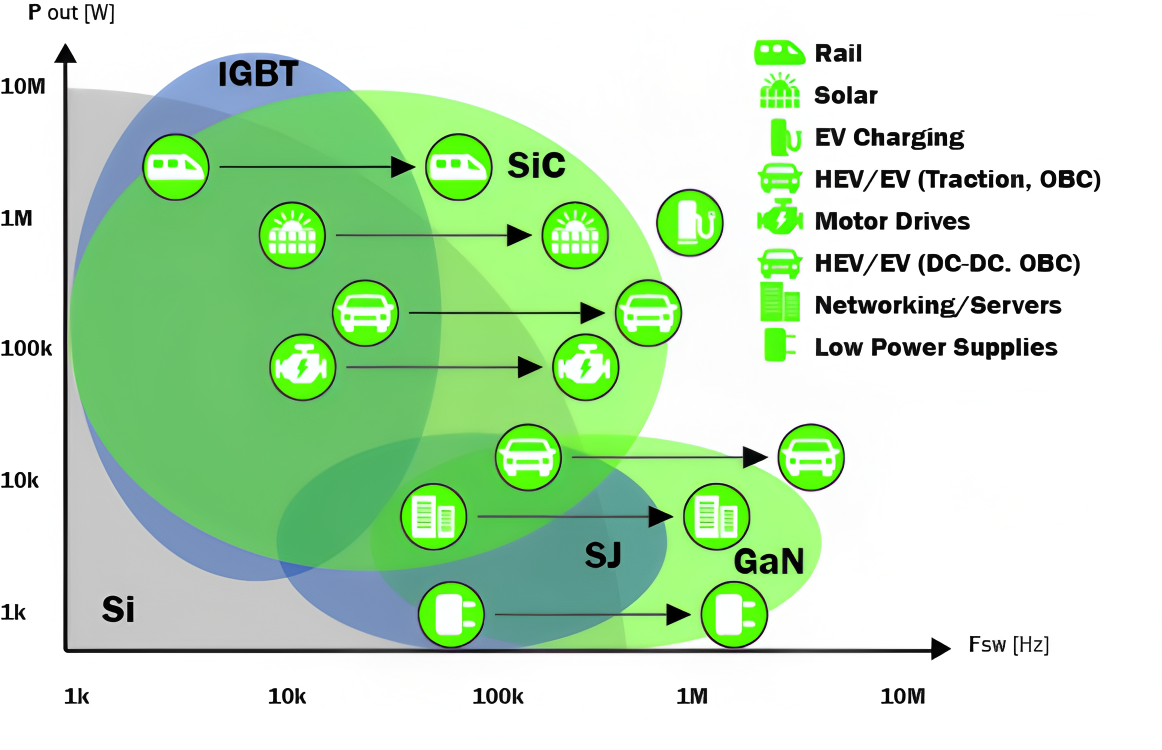

傾佳電子(Changer Tech)是一家專注于功率半導(dǎo)體和新能源汽車連接器的分銷商。主要服務(wù)于中國(guó)工業(yè)電源、電力電子設(shè)備和新能源汽車產(chǎn)業(yè)鏈。傾佳電子聚焦于新能源、交通電動(dòng)化和數(shù)字化轉(zhuǎn)型三大方向,并提供包括IGBT、SiC MOSFET、GaN等功率半導(dǎo)體器件以及新能源汽車連接器。

傾佳電子楊茜致力于推動(dòng)國(guó)產(chǎn)SiC碳化硅模塊在電力電子應(yīng)用中全面取代進(jìn)口IGBT模塊,助力電力電子行業(yè)自主可控和產(chǎn)業(yè)升級(jí)!

傾佳電子楊茜咬住SiC碳化硅MOSFET功率器件三個(gè)必然,勇立功率半導(dǎo)體器件變革潮頭:

傾佳電子楊茜咬住SiC碳化硅MOSFET模塊全面取代IGBT模塊和IPM模塊的必然趨勢(shì)!

傾佳電子楊茜咬住SiC碳化硅MOSFET單管全面取代IGBT單管和大于650V的高壓硅MOSFET的必然趨勢(shì)!

傾佳電子楊茜咬住650V SiC碳化硅MOSFET單管全面取代SJ超結(jié)MOSFET和高壓GaN 器件的必然趨勢(shì)!

第一部分:同步整流技術(shù)的歷史演進(jìn)與基礎(chǔ)理論

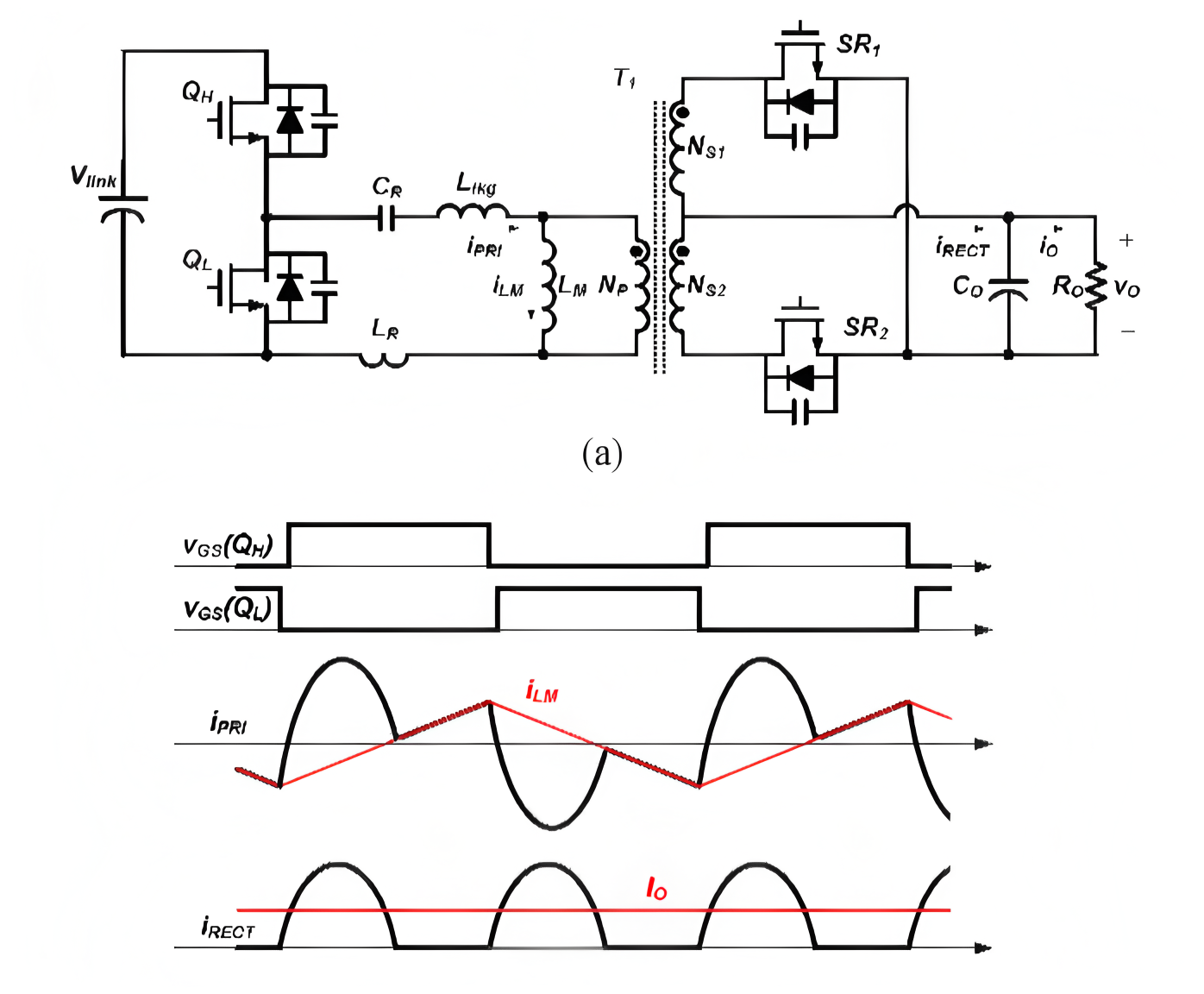

1.1. 同步整流(SR)概念的起源與發(fā)展初衷

同步整流(Synchronous Rectification, SR)技術(shù)的興起,是電力電子領(lǐng)域?yàn)檫m應(yīng)日益嚴(yán)苛的效率要求,特別是在低電壓、高電流輸出應(yīng)用中,所采取的關(guān)鍵技術(shù)飛躍。其歷史背景可追溯到20世紀(jì)90年代后期,當(dāng)時(shí)個(gè)人計(jì)算機(jī)和通信系統(tǒng)對(duì)供電電壓的要求逐漸從 5V 降至 1V 甚至更低 。

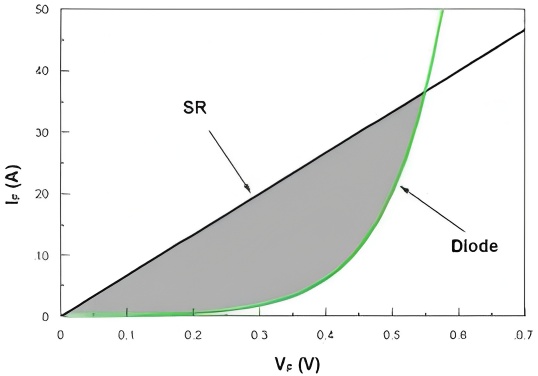

在傳統(tǒng)的開(kāi)關(guān)電源(SMPS)二次側(cè)整流中,通常使用PN結(jié)二極管或肖特基二極管(Schottky Diode)進(jìn)行整流。然而,這些傳統(tǒng)二極管具有固定的正向?qū)妷?VF。肖特基二極管的 VF 通常在 0.3V 左右,但這一壓降在輸出電壓極低時(shí),占據(jù)了總輸出電壓的顯著比例,導(dǎo)致整流階段的功耗 P∝VF?I 成為主要的效率瓶頸 。物理限制決定了二極管的 VF 很難降低到 0.3V 以下。

SR技術(shù)的核心思想是利用場(chǎng)效應(yīng)晶體管(MOSFET)取代傳統(tǒng)二極管。MOSFET在導(dǎo)通狀態(tài)下表現(xiàn)為純電阻特性,其導(dǎo)通壓降 VDS 由電流和導(dǎo)通電阻 RDS(on) 決定,即 VDS≈I?RDS(on)。通過(guò)設(shè)計(jì)和工藝優(yōu)化,MOSFET的 RDS(on) 可以不斷降低,或者通過(guò)并聯(lián)多個(gè)晶粒來(lái)減小等效電阻 。因此,在給定電流下,SR MOSFET的等效壓降能夠顯著低于傳統(tǒng)二極管的 VF,從而大幅提升效率。

1.2. MOSFET替代二極管的原理與量化優(yōu)勢(shì)

同步整流模式要求精確控制MOSFET的柵極驅(qū)動(dòng)電壓,使其導(dǎo)通與截止時(shí)間與被整流電壓的變化嚴(yán)格同步 。這種精確控制確保了電流流經(jīng)低損耗的MOSFET溝道,避免了傳統(tǒng)整流器件在電壓上升和下降過(guò)程中的瞬態(tài)損耗。

在實(shí)際應(yīng)用中,例如在快速充電電路的輸出級(jí),同步整流 MOSFET 通常選用 40V 到 100V 的低壓器件,內(nèi)阻 RDS(on) 可低至 3mΩ 到 8mΩ 。在設(shè)計(jì)權(quán)衡中,隨著負(fù)載電流密度的不斷增加,傳統(tǒng)的 VF 損耗雖然與電流呈線性關(guān)系,但其無(wú)法繼續(xù)降低的限制使其在高電流下不可避免地成為瓶頸。相比之下,SR 損耗 P∝I2?RDS(on) 雖然對(duì)電流的平方敏感,但 RDS(on) 具有持續(xù)降低的空間,使其在高電流應(yīng)用中具有優(yōu)越的損耗擴(kuò)展性。

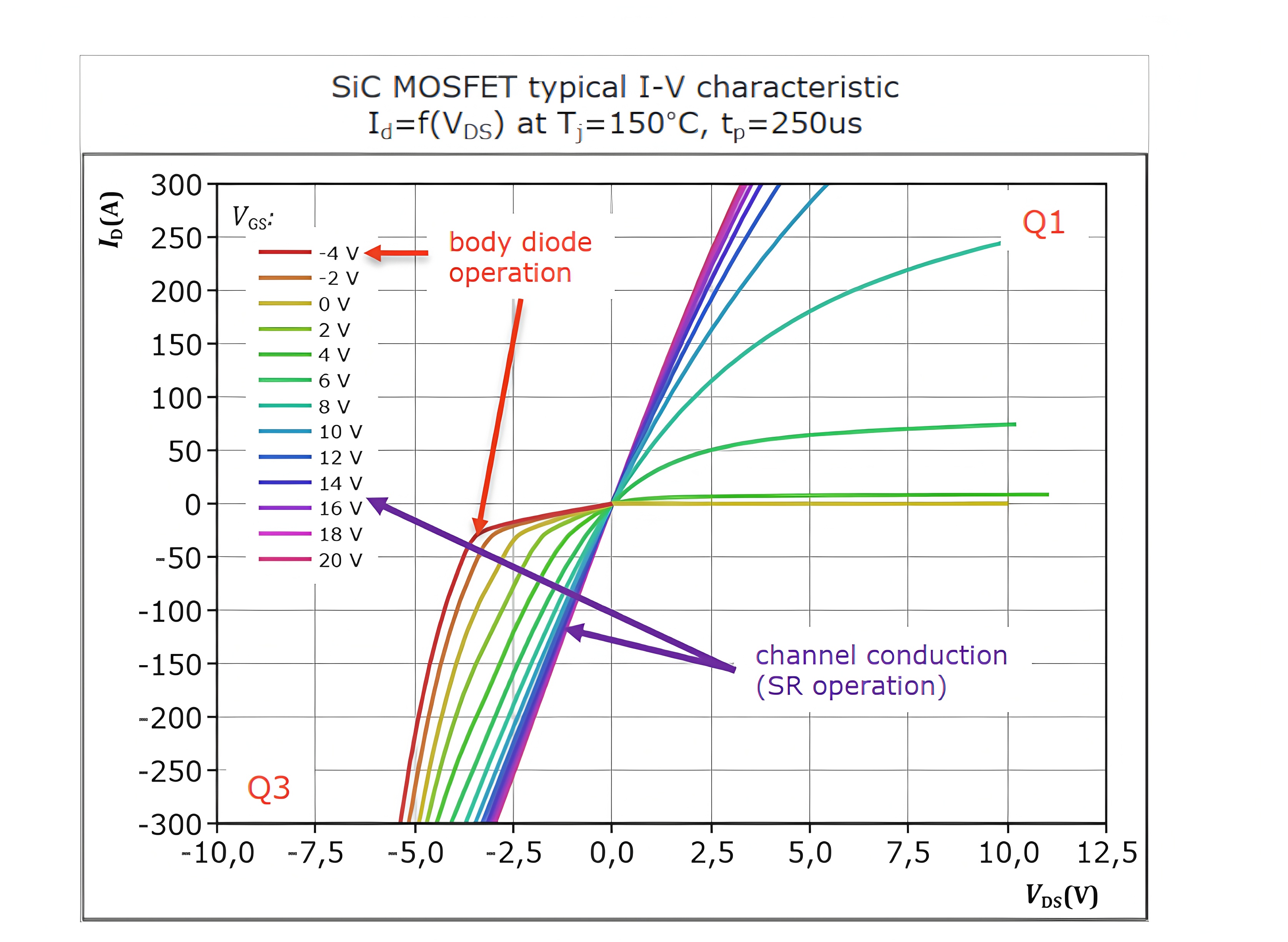

從技術(shù)發(fā)展歷程來(lái)看,同步整流技術(shù)在低壓輸出場(chǎng)景下,成功解決了 VF 這一核心效率障礙。然而,在寬禁帶(WBG)時(shí)代,特別是在高壓 1200V 碳化硅(SiC)器件的應(yīng)用中,同步整流的目標(biāo)發(fā)生了根本性轉(zhuǎn)變:它不再僅僅是用于解決低壓 VF 瓶頸,而必須解決高壓 SiC 器件在第三象限導(dǎo)通時(shí)面臨的體二極管(Body Diode)的高正向壓降和**反向恢復(fù)電荷(Qrr)**問(wèn)題。這一轉(zhuǎn)變將 SR 技術(shù)從純粹的“效率優(yōu)化”工具,提升為“確保 SiC 器件安全及高頻運(yùn)行的先決條件”。

第二部分:碳化硅功率器件(SiC MOSFET)的獨(dú)特電學(xué)特性分析

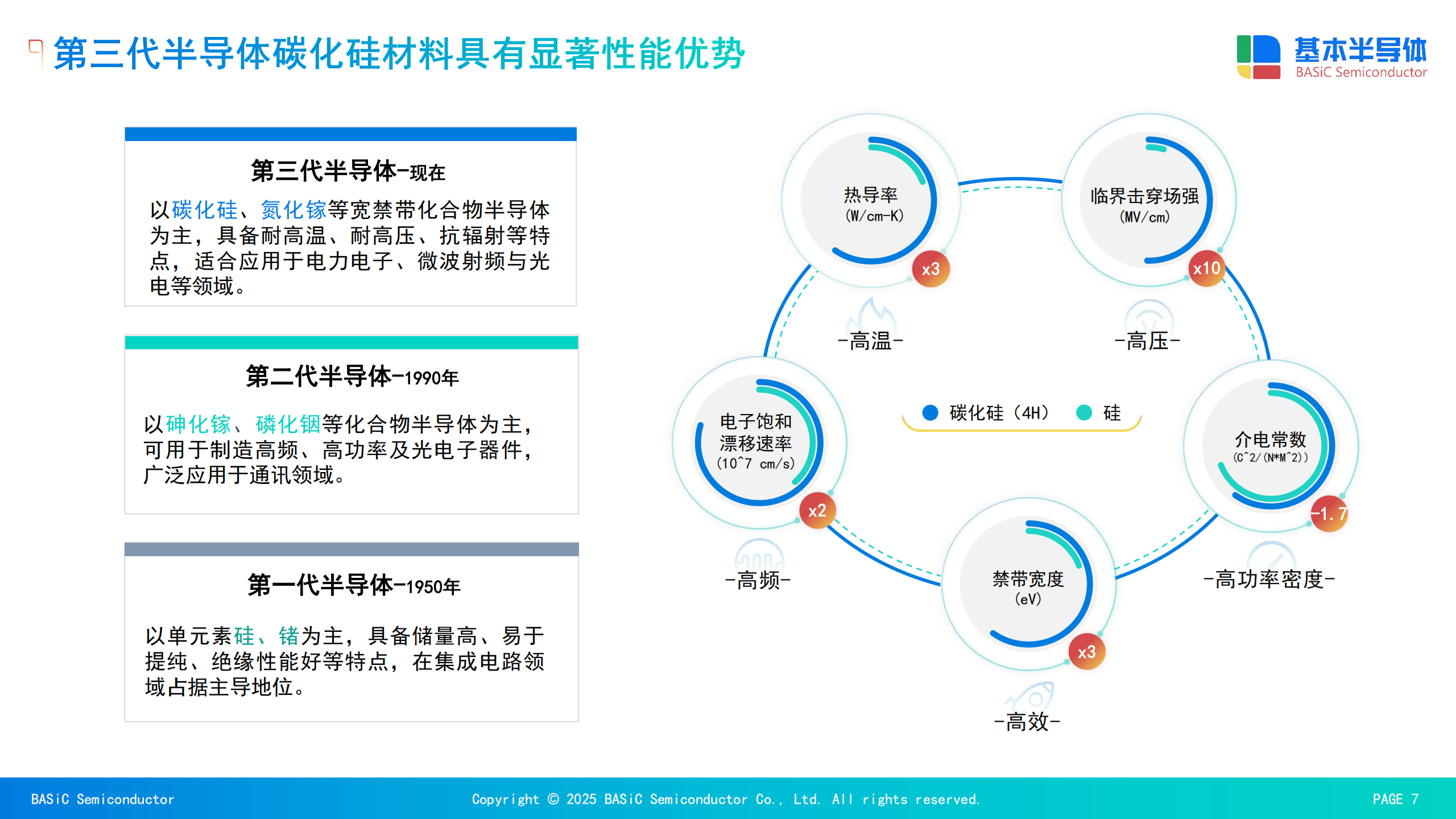

2.1. SiC WBG材料的本質(zhì)優(yōu)勢(shì)及其對(duì)系統(tǒng)損耗的影響

碳化硅(SiC)作為一種寬禁帶半導(dǎo)體材料,相比傳統(tǒng)的硅(Si)器件,具有卓越的電學(xué)和熱學(xué)特性,包括高擊穿場(chǎng)強(qiáng)(是 Si 的十倍)、寬禁帶(是 Si 的三倍)和高熱導(dǎo)率(是 Si 的三倍)。這些特性使得 SiC MOSFET 能夠?qū)崿F(xiàn)極低的導(dǎo)通電阻 RDS(on)、極高的開(kāi)關(guān)速度,并容許更高的工作溫度。

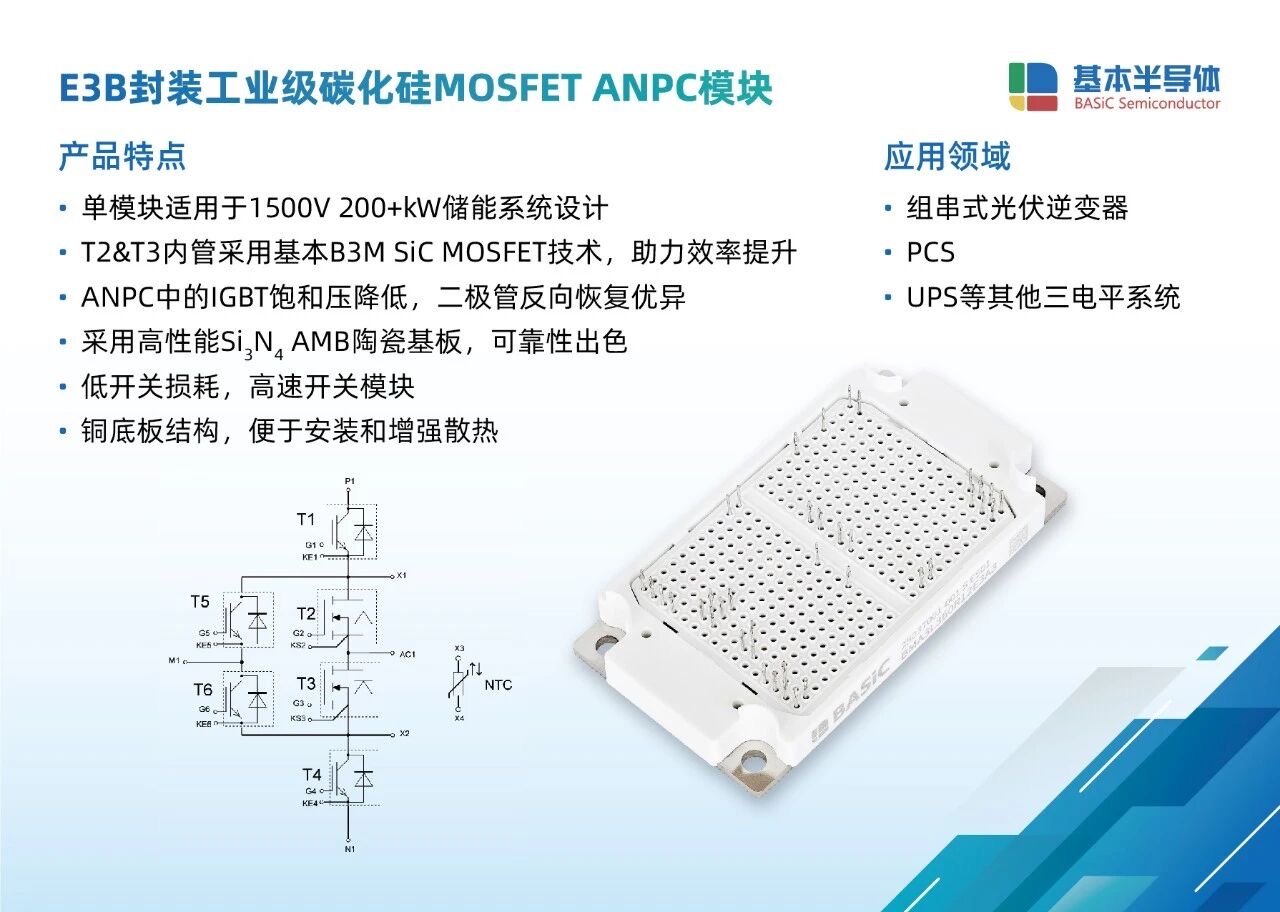

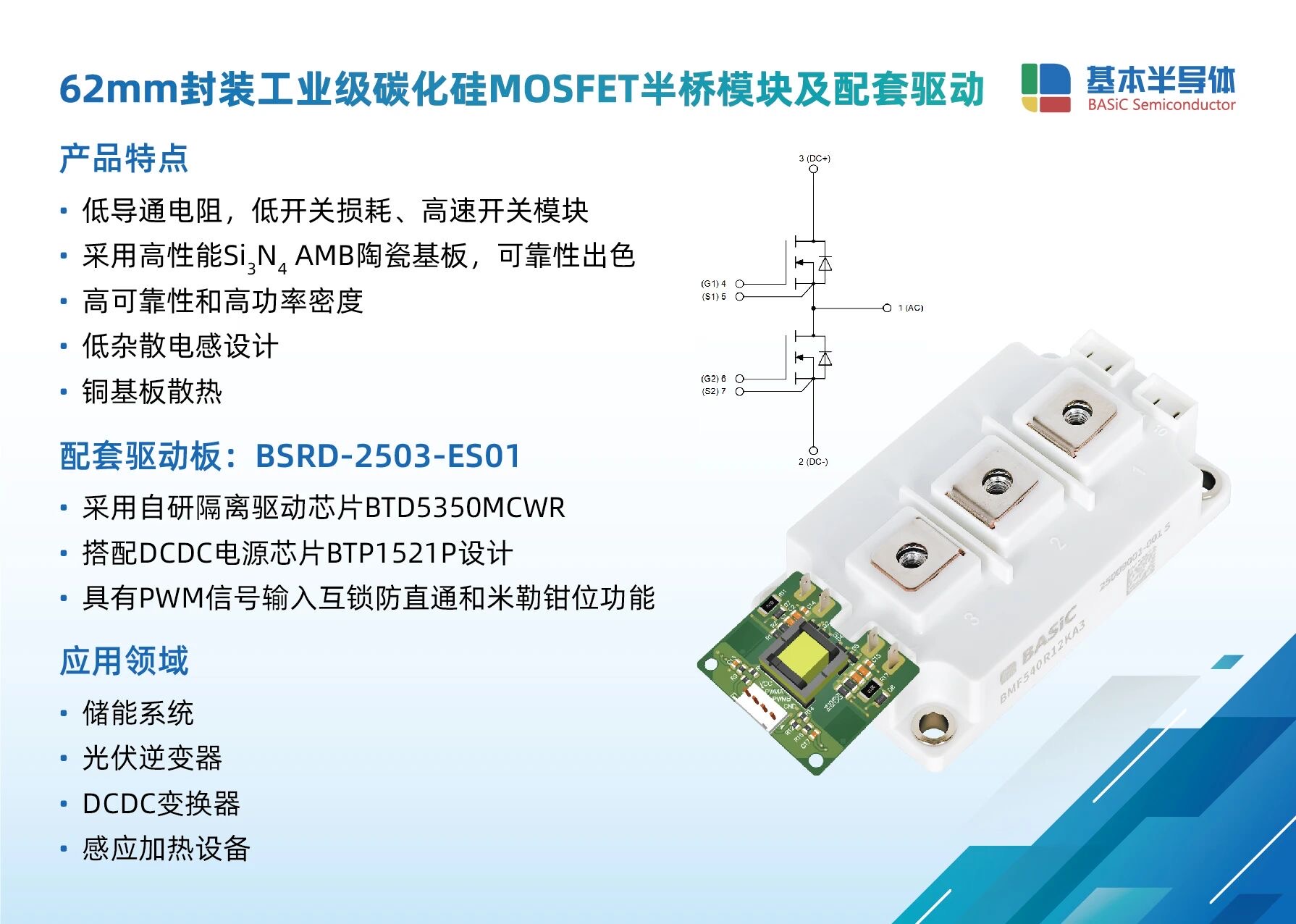

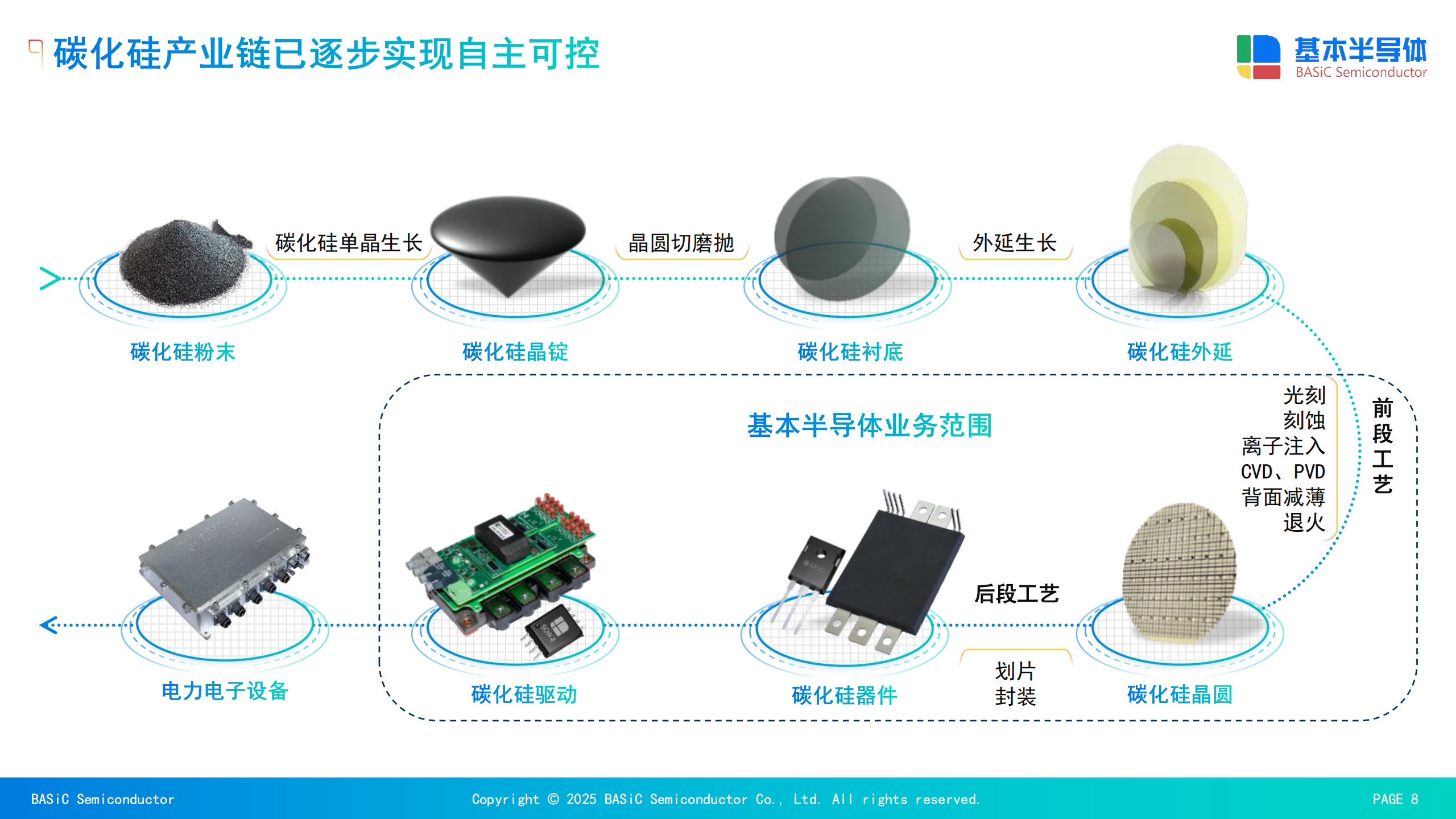

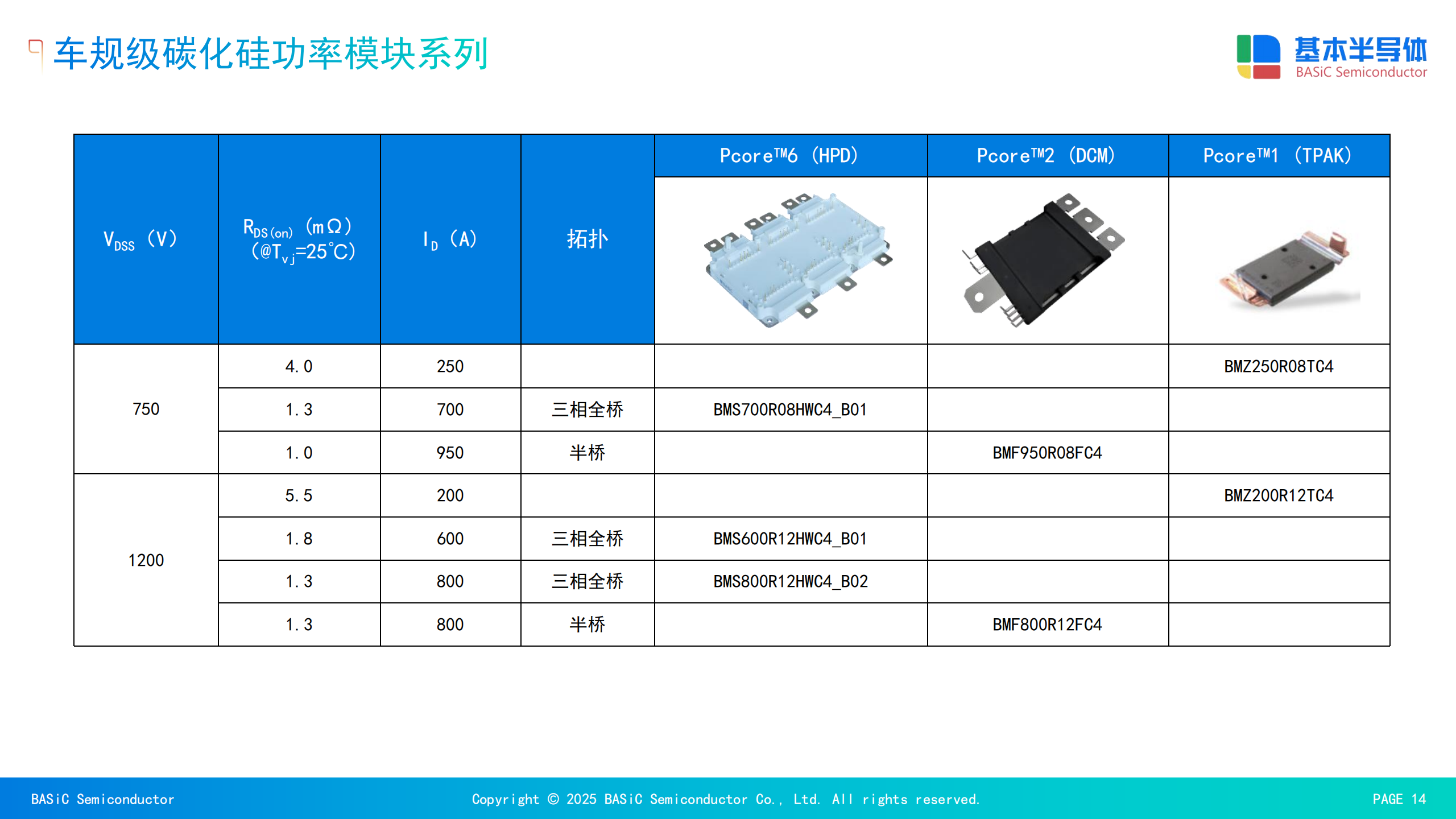

以基本半導(dǎo)體的 BMF 系列 1200V SiC MOSFET 模塊為例,這些模塊專為高頻、高功率應(yīng)用(如電動(dòng)汽車、儲(chǔ)能、DC-DC 變換器)設(shè)計(jì) 。它們具有低電感設(shè)計(jì)和優(yōu)化的熱管理結(jié)構(gòu),如銅基板和 Si3N4 陶瓷襯底,以確保高可靠性和高功率密度。例如,BMF540R12KA3 模塊在 VGS=18V 時(shí),典型 RDS(on) 僅為 2.5mΩ 。

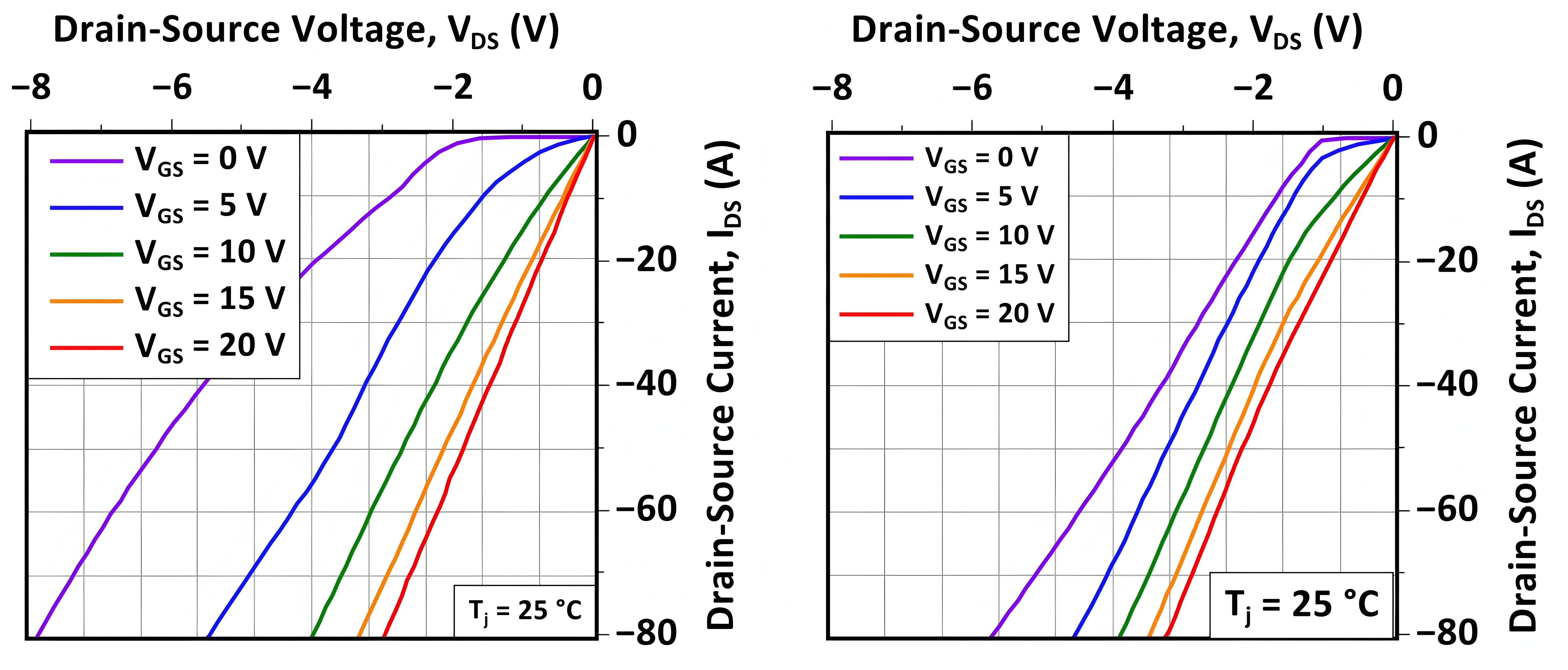

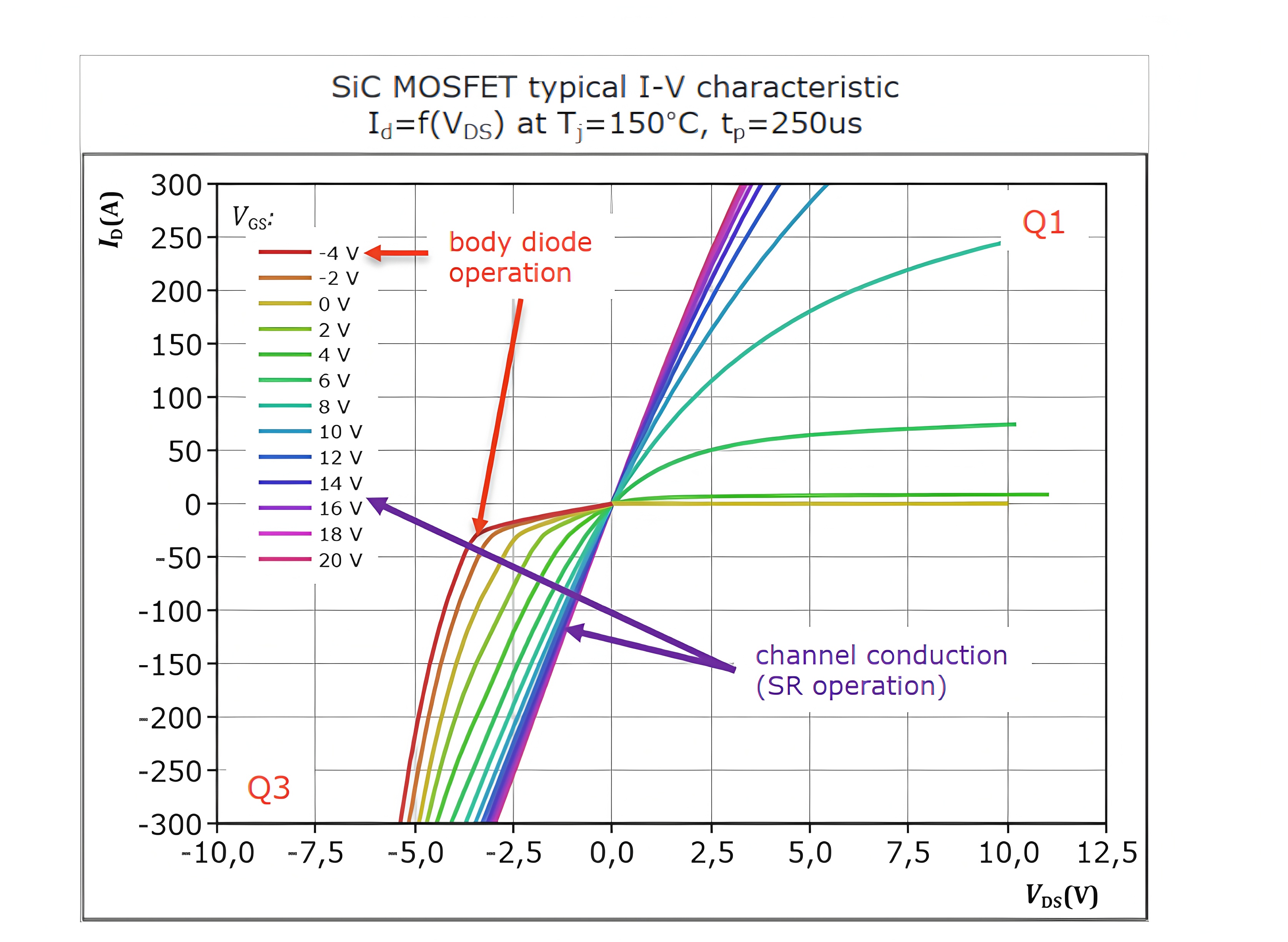

2.2. SiC MOSFET溝道導(dǎo)通特性:SR模式下的低損耗基準(zhǔn)

在同步整流模式下,MOSFET 的溝道被開(kāi)啟(通常采用 VGS=+18V),使得電流通過(guò)低阻抗的溝道流過(guò),此時(shí)導(dǎo)通損耗僅取決于 I2RDS(on)。

SiC MOSFET 的 RDS(on) 具有正溫度系數(shù),這意味著電阻隨結(jié)溫 Tvj 升高而增加,這有利于多個(gè)器件并聯(lián)時(shí)的電流均衡。例如,BMF80R12RA3 模塊在 80A 電流下,其 RDS(on) 從 25°C 時(shí)的 15.0mΩ 增加到 175°C 時(shí)的 26.7mΩ 。盡管如此,即使在高結(jié)溫和大電流下,通過(guò) SR 溝道實(shí)現(xiàn)的等效壓降仍然非常低。

2.3. SiC MOSFET體二極管的固有挑戰(zhàn):高 VSD 的量化確認(rèn)

然而,SiC MOSFET 的 PN 結(jié)體二極管在反向續(xù)流時(shí),表現(xiàn)出固有的高正向?qū)妷?VSD。如果 MOSFET 在死區(qū)時(shí)間沒(méi)有被同步開(kāi)啟(例如 VGS=0V 或負(fù)偏壓,如 ?4V),電流將被迫流經(jīng)這一 PN 結(jié),導(dǎo)致巨大的傳導(dǎo)損耗。

為了直觀展示這一挑戰(zhàn),下表對(duì)比了 SiC 模塊在體二極管模式(非 SR)和同步整流模式下的芯片級(jí)導(dǎo)通電壓 VSD。所有數(shù)據(jù)均選取結(jié)溫 Tvj=175°C,以反映實(shí)際工作環(huán)境下的最差情況。

SiC MOSFET模塊的導(dǎo)通電壓特性對(duì)比:體二極管模式 vs. 同步整流模式 (Tvj=175°C)

| 器件型號(hào) | 額定電流 ID (A) | 體二極管模式 VSD (V)(VGS=?4V/-5V) | 同步整流模式 VSD (V)(VGS=+18V) | 壓降降低百分比 (%)(近似) | 數(shù)據(jù)來(lái)源 |

|---|---|---|---|---|---|

| BMF80R12RA3 | 80 | 4.09 (chip) | 2.12 (chip) | 48% | |

| BMF120R12RB3 | 120 | 4.69 (chip) | 2.14 (chip) | 54% | |

| BMF360R12KA3 | 360 | 4.47 (chip) | 2.17 (chip) | 51% | |

| BMF540R12KA3 | 540 | 4.47 (chip) | 2.17 (chip) | 51% |

分析顯示,在所有測(cè)試模塊中,體二極管模式下的芯片級(jí) VSD 均在 4.0V 以上,而通過(guò) SR 開(kāi)啟溝道后,等效壓降可降低約 50% 以上,降至約 2.1V 左右。這一巨大的壓降差距表明,如果電流被迫流經(jīng)體二極管,將產(chǎn)生不可接受的導(dǎo)通損耗和熱量。

這一現(xiàn)象的本質(zhì)是寬禁帶材料的固有特征:SiC PN 結(jié)需要更高的啟動(dòng)電壓才能承載電流。因此,在 SiC 器件中啟用 SR 模式,是規(guī)避材料物理限制、利用其低 RDS(on) 優(yōu)勢(shì)的唯一有效途徑。

2.4. 反向恢復(fù)特性(Qrr/ Err):高頻應(yīng)用的隱形殺手

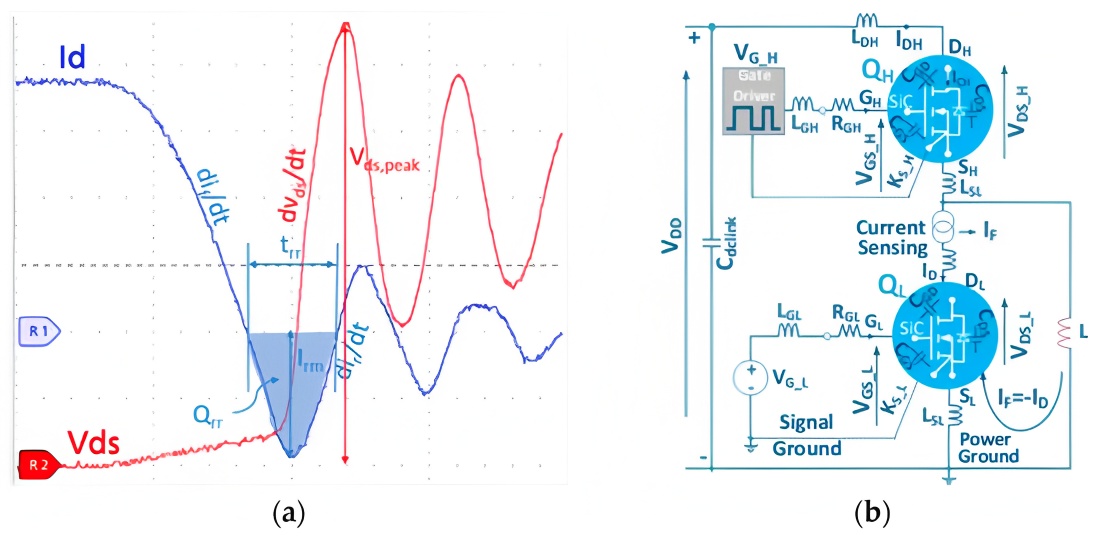

在橋式電路中,當(dāng)電流從一個(gè) MOSFET 換流到其對(duì)臂的 MOSFET 時(shí),如果前一個(gè)器件的體二極管參與續(xù)流,它會(huì)積累反向恢復(fù)電荷 Qrr。當(dāng)對(duì)臂 MOSFET 開(kāi)啟時(shí),必須先清除這些 Qrr,這個(gè)過(guò)程產(chǎn)生反向恢復(fù)電流 Irrm 和反向恢復(fù)能量 Err 。

雖然 SiC MOSFET 的 Qrr 遠(yuǎn)低于硅基 MOSFET,但在大電流和高開(kāi)關(guān)頻率下,由 Qrr 導(dǎo)致的損耗和瞬態(tài)電壓應(yīng)力依然嚴(yán)重。例如,BMF540R12KA3 模塊在 175°C 下,Qrr 達(dá)到 9.5uC, Err 達(dá)到 3.3mJ 。高 Irrm 與電路中的寄生電感相互作用,會(huì)產(chǎn)生巨大的電壓尖峰 V=L?di/dt 。SiC 器件極高的開(kāi)關(guān)速度( di/dt)使得這一問(wèn)題更加突出,可能導(dǎo)致器件過(guò)壓失效或嚴(yán)重的電磁干擾(EMI)。因此,同步整流在 SiC 高頻應(yīng)用中不僅是“節(jié)能器”,更是“保護(hù)器”,其目的是通過(guò)避免體二極管導(dǎo)通,徹底消除 Qrr 相關(guān)的損耗和應(yīng)力。

第三部分:SiC橋式電路中同步整流的必然性論證

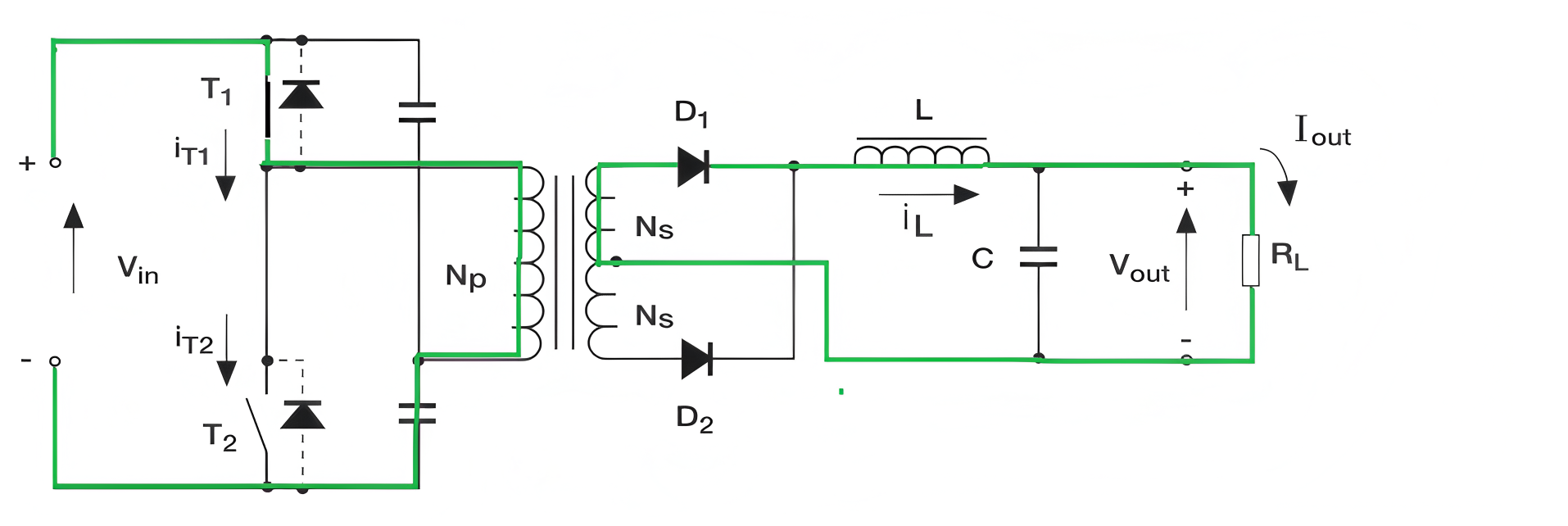

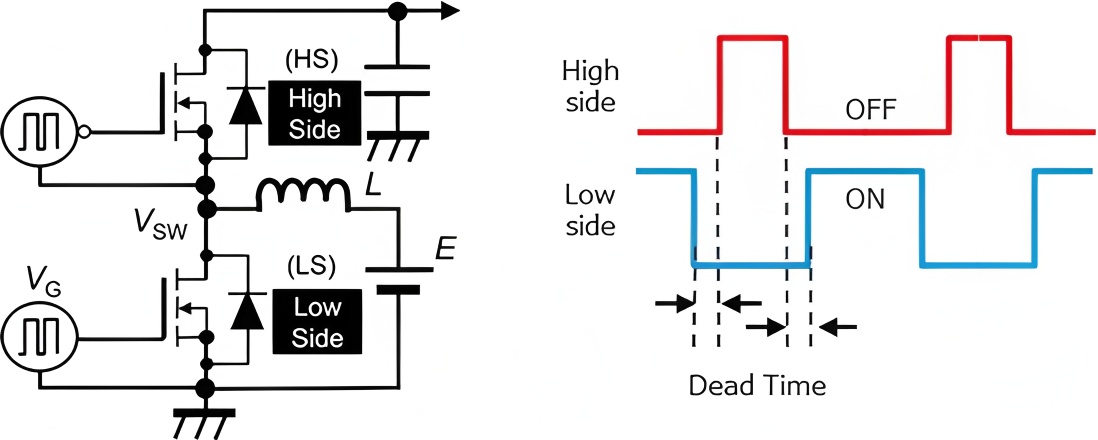

3.1. 橋式電路換流模型與死區(qū)時(shí)間分析

在半橋或全橋電路(如逆變器或雙向 DC/DC 變換器)中,為了防止上下橋臂在換流過(guò)程中發(fā)生短路(直通),必須引入一個(gè)短暫的死區(qū)時(shí)間 TDT。在 TDT 期間,上下開(kāi)關(guān)管均處于關(guān)斷狀態(tài),此時(shí)電感電流必須通過(guò)橋臂的續(xù)流器件續(xù)流。

在沒(méi)有啟用同步整流模式的 SiC 橋臂中,這意味著電流將強(qiáng)制流經(jīng) SiC MOSFET 的體二極管。如果 TDT 過(guò)長(zhǎng)或 VGS 驅(qū)動(dòng)不當(dāng),體二極管導(dǎo)通的時(shí)間占比增加,將直接導(dǎo)致效率崩潰。

3.2. 核心論據(jù):體二極管導(dǎo)通損耗的量化不可接受性

如第二部分所示,SiC 體二極管的導(dǎo)通壓降比 SR 溝道高出約 50% 以上。在追求 99% 極致效率的高功率系統(tǒng)中,任何超過(guò) 1V 的額外壓降都意味著巨大的損耗。

可以進(jìn)行如下的簡(jiǎn)化損耗對(duì)比:假設(shè)一個(gè)高功率系統(tǒng)在死區(qū)時(shí)間 TDT 期間,有 5% 的時(shí)間電流流經(jīng)續(xù)流器件,平均電流 IAVG=100A。以 120A 的 BMF120R12RB3 模塊在 175°C 下的數(shù)據(jù)為例 :

體二極管模式下(非 SR):體二極管 VSD≈4.69V。

體二極管模式下平均損耗 Pdiode≈4.69V×100A×0.05≈23.45W。

同步整流模式下(SR):SR 溝道 VSD≈2.14V。

SR 模式下平均損耗 PSR≈2.14V×100A×0.05≈10.70W。

僅僅 5% 的死區(qū)時(shí)間續(xù)流,體二極管就會(huì)帶來(lái) 12.75W 的額外損耗。在高功率、高效率的電動(dòng)汽車或儲(chǔ)能應(yīng)用中,這種級(jí)別的額外熱損耗是無(wú)法接受的,它會(huì)顯著增加散熱需求,破壞整體效率目標(biāo)。同步整流通過(guò)將高 VSD 損耗轉(zhuǎn)化為低 I2RDS(on) 損耗,實(shí)現(xiàn)了導(dǎo)通損耗的最小化。效率每提高 1%,通常可以使散熱需求減少約 10% ,從而顯著提高功率密度并降低系統(tǒng)成本 。

3.3. 核心論據(jù):Qrr 徹底消除對(duì)系統(tǒng)可靠性的決定性貢獻(xiàn)

在 SiC 高頻應(yīng)用中,SR 的最大價(jià)值在于它消除了體二極管的反向恢復(fù)。如果體二極管在 TDT 期間導(dǎo)通并積累電荷 Qrr,當(dāng)對(duì)臂 MOSFET 開(kāi)啟時(shí),這些電荷會(huì)引發(fā)尖峰電流 Irrm 和反向恢復(fù)能量 Err 。

下表量化了 SiC 模塊在體二極管模式下產(chǎn)生的反向恢復(fù)特性:

SiC MOSFET模塊的開(kāi)關(guān)損耗特性:體二極管模式下反向恢復(fù)分析 (Tvj=175°C)

| 器件型號(hào) | 測(cè)試電流 ISD (A) | 反向恢復(fù)電荷 Qrr (μC) | 反向恢復(fù)能量 Err (μJ/mJ) | 峰值反向恢復(fù)電流 Irrm (A) | SR 模式下 Qrr | 數(shù)據(jù)來(lái)源 |

|---|---|---|---|---|---|---|

| BMF80R12RA3 | 80 | 1.6 | 608.5uJ | 65.4 | ≈0 | |

| BMF120R12RB3 | 120 | 2.24 | 735uJ | 97 | ≈0 | |

| BMF540R12KA3 | 540 | 9.5 | 3.3mJ | 338 | ≈0 |

以 BMF540R12KA3 為例,其 Irrm 峰值高達(dá) 338A,即使在 175°C 下 Err 也達(dá)到 3.3mJ 。如果系統(tǒng)工作在

50kHz,由此帶來(lái)的開(kāi)關(guān)損耗 Prr=fsw?Err 將高達(dá) 165W。這種巨大的瞬態(tài)損耗不僅嚴(yán)重降低效率,更重要的是,高 Irrm 在寄生電感中產(chǎn)生的電壓尖峰,會(huì)對(duì)器件造成嚴(yán)重的過(guò)壓應(yīng)力。

精確的同步整流意味著 MOSFET 在續(xù)流期間通過(guò)溝道導(dǎo)通,完全繞過(guò)了體二極管的 PN 結(jié)。在這種模式下,Qrr 約為零,從而徹底消除了

Err 相關(guān)的開(kāi)關(guān)損耗和電壓尖峰。在 SiC 器件固有的高 di/dt 特性下,消除 Irrm 這一應(yīng)力源,是確保 SiC 模塊在高頻下具備高可靠性的決定性因素。因此,同步整流是 SiC 橋式電路中實(shí)現(xiàn)極致效率和高可靠性,并充分發(fā)揮 SiC 寬禁帶材料優(yōu)勢(shì)的唯一技術(shù)路徑。

第四部分:SiC同步整流的實(shí)現(xiàn)挑戰(zhàn)與精確定量控制策略

SiC MOSFET 啟用同步整流模式帶來(lái)了巨大的效率收益,但也對(duì)控制系統(tǒng)提出了更高的挑戰(zhàn),要求控制精度必須適應(yīng) SiC 器件的超快開(kāi)關(guān)速度和對(duì)體二極管導(dǎo)通的零容忍。

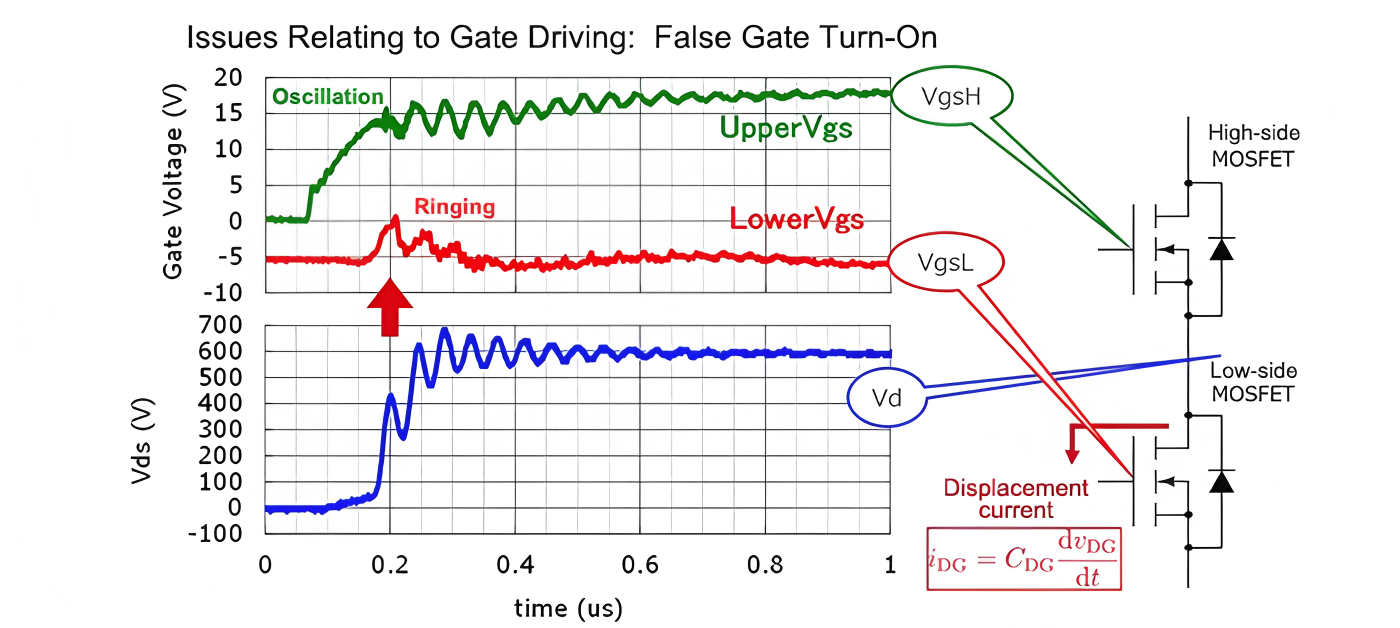

4.1. 挑戰(zhàn)一:SiC高 di/dt 對(duì)控制電路的干擾

SiC MOSFET 的極快開(kāi)關(guān)速度,其上升時(shí)間 (tr) 和下降時(shí)間 (tf) 通常在 20ns 到 60ns 范圍內(nèi) ,導(dǎo)致極高的 di/dt。高 di/dt 與功率回路的寄生電感相互作用,在 VDS 上產(chǎn)生強(qiáng)烈的電壓振蕩(Ringing)。依賴 VDS 變化的同步整流控制器極易被這些振蕩誤觸發(fā) 。此外,SiC 器件 RDS(on) 的不斷降低意味著 I2RDS(on) 損耗與體二極管高 VSD 損耗之間的差距進(jìn)一步擴(kuò)大,因此任何微小的控制失誤,導(dǎo)致體二極管短暫導(dǎo)通,都會(huì)帶來(lái)不成比例的巨大效率懲罰,對(duì)控制器的精度要求呈指數(shù)級(jí)提高。

4.2. 挑戰(zhàn)二:實(shí)現(xiàn)精確的自適應(yīng)死區(qū)時(shí)間控制

死區(qū)時(shí)間 TDT 的設(shè)置是同步整流控制的核心難點(diǎn)。如果 TDT 過(guò)長(zhǎng),電流會(huì)流經(jīng)高損耗的體二極管;如果 TDT 過(guò)短,則可能導(dǎo)致上下橋臂直通,引發(fā)災(zāi)難性故障 。理想的 TDT 并非固定值,而是必須隨輸入電壓、負(fù)載電流和工作溫度動(dòng)態(tài)變化。傳統(tǒng)的固定時(shí)間控制難以滿足 SiC 系統(tǒng)對(duì)極致效率的要求。

4.3. 關(guān)鍵控制策略:VDS 傳感器的精確零電流檢測(cè) (ZCD)

為了應(yīng)對(duì)這些挑戰(zhàn),先進(jìn)的同步整流控制器(如 NEX81801DA)采用 VDS 傳感器進(jìn)行精確的零電流檢測(cè)(Zero Current Detection, ZCD),實(shí)現(xiàn)自適應(yīng)控制 。

這些控制器通過(guò)實(shí)時(shí)監(jiān)測(cè)同步整流 MOSFET 的 VDS 極性變化來(lái)確定電流方向。當(dāng) VDS 從負(fù)值(MOSFET 導(dǎo)通)變?yōu)檎禃r(shí),表明電流方向即將反轉(zhuǎn),SR FET 必須快速關(guān)斷,以最小化體二極管的導(dǎo)通時(shí)間。

為了解決高 di/dt 振蕩導(dǎo)致的誤觸發(fā)問(wèn)題,控制器必須具備可外部調(diào)節(jié)的導(dǎo)通消隱時(shí)間(Blanking Time)。只有在 VDS 變化持續(xù)時(shí)間超過(guò)這個(gè)消隱時(shí)間后,控制信號(hào)才會(huì)被識(shí)別。此外,SR 控制器必須能夠自適應(yīng)地調(diào)節(jié) SR 導(dǎo)通時(shí)間,以優(yōu)化輕載條件下的效率,從而改善電源在整個(gè)負(fù)載范圍內(nèi)的平均效率。

4.4. 針對(duì) SiC 的數(shù)字與硬件輔助控制優(yōu)化

為了實(shí)現(xiàn) SiC 系統(tǒng)所需的極致精度,數(shù)字控制和硬件輔助控制策略被廣泛應(yīng)用:

數(shù)字自適應(yīng)控制:針對(duì)特定拓?fù)洌ㄈ珉p向 LLC 諧振變換器),研究提出了基于二階擬合模型的數(shù)字同步整流控制算法 。該算法能夠準(zhǔn)確計(jì)算并動(dòng)態(tài)調(diào)節(jié)同步整流管的導(dǎo)通時(shí)間,從而顯著降低導(dǎo)通損耗。在實(shí)驗(yàn)中,該方法在 300kHz 開(kāi)關(guān)頻率下,相比傳統(tǒng)算法可減少 27.7W 的同步整流管損耗 。

硬件輔助死區(qū)時(shí)間調(diào)整:通過(guò)脈沖產(chǎn)生單元、RC 單元和比較單元的組合,可以構(gòu)建具有死區(qū)時(shí)間調(diào)整的橋式同步整流電路 。這種方法提供了增強(qiáng)的魯棒性,適用于全橋和半橋拓?fù)洹?

下表總結(jié)了高效率同步整流控制策略的對(duì)比:

高效率同步整流控制策略對(duì)比與 SiC 適應(yīng)性

| 控制策略 | 實(shí)現(xiàn)機(jī)制 | 對(duì)SiC應(yīng)用的益處 | 主要挑戰(zhàn) | 數(shù)據(jù)來(lái)源 |

|---|---|---|---|---|

| 傳統(tǒng)定時(shí)控制 | 固定開(kāi)關(guān)周期或死區(qū)時(shí)間 | 實(shí)現(xiàn)簡(jiǎn)單,成本低 | 無(wú)法適應(yīng)動(dòng)態(tài)工況,極易導(dǎo)致體二極管損耗 | |

| VDS 傳感 ZCD | 實(shí)時(shí)監(jiān)測(cè) VDS 極性變化 | 實(shí)時(shí)性高,提高了輕載和變頻效率 | 寄生電感振蕩干擾,需要精確消隱時(shí)間 TBLANK | |

| 數(shù)字自適應(yīng)控制 | 基于二階擬合模型動(dòng)態(tài)計(jì)算 TDT | 精確最小化體二極管導(dǎo)通時(shí)間,顯著降低導(dǎo)通損耗 | 算法和計(jì)算資源要求高,動(dòng)態(tài)響應(yīng)速度是關(guān)鍵 |

值得注意的是,先進(jìn)的 SR 控制器(如 NEX81801DA)即使是低功耗芯片,也采用低熱阻的 TSOT23-6 封裝 。這從側(cè)面反映了 SiC 高頻應(yīng)用環(huán)境的熱密度極高,對(duì)包括控制芯片在內(nèi)的所有元件的熱性能提出了嚴(yán)苛的要求。這證實(shí)了在 SiC 系統(tǒng)中,熱管理策略必須從功率器件擴(kuò)展到整個(gè)控制鏈,實(shí)現(xiàn)熱量的“源頭抑制”而非僅僅依賴“散熱處理”。

第五部分:SiC同步整流技術(shù)的未來(lái)發(fā)展趨勢(shì)與應(yīng)用前景

5.1. 拓?fù)鋭?chuàng)新與效率提升

SiC 同步整流技術(shù)正在推動(dòng)電力電子拓?fù)湎蚋哳l率和雙向功率流發(fā)展。在諧振變換器(如 LLC)中,SiC SR 是實(shí)現(xiàn)高頻和雙向性的核心 。通過(guò)數(shù)字控制和 SiC 器件的超低 RDS(on) 及近零 Qrr 特性,LLC 拓?fù)淠軌蛟?300kHz 甚至更高的頻率下維持 98% 以上的效率 。

未來(lái)的發(fā)展趨勢(shì)是將損耗最小化控制從單向系統(tǒng)擴(kuò)展到雙向系統(tǒng),例如在模塊化多電平變換器(MMC)子模塊中,利用 SiC MOSFET 溝道的雙向?qū)ㄌ匦裕ㄟ^(guò)調(diào)整同步整流和非同步整流模式的占比,實(shí)現(xiàn)器件損耗的自適應(yīng)均衡 。

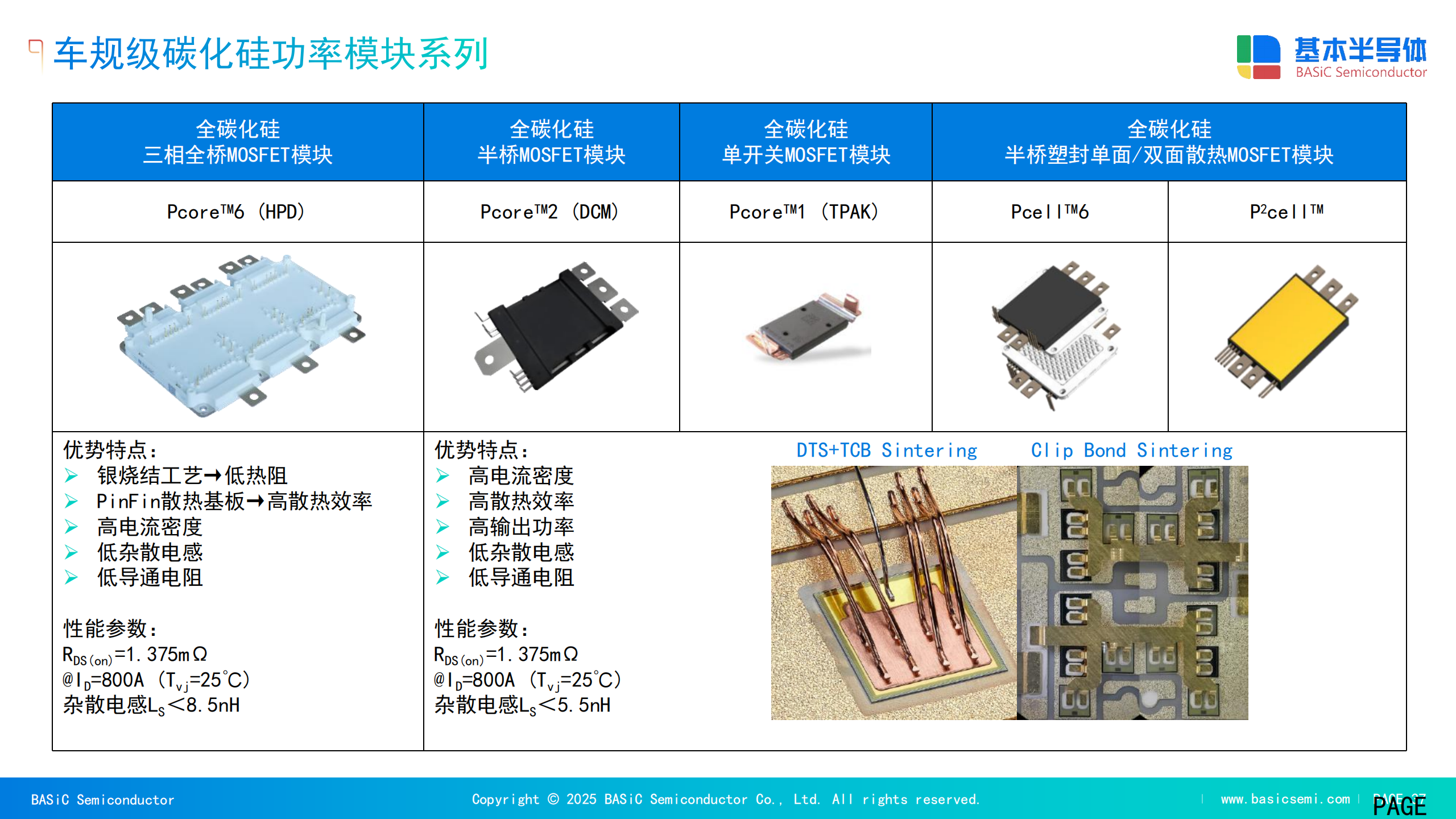

5.2. 系統(tǒng)集成度提升與封裝優(yōu)化

SiC 功率模塊正朝著標(biāo)準(zhǔn)化和 SiC 優(yōu)化封裝方向發(fā)展,以提高系統(tǒng)級(jí)效率和功率密度 。基本半導(dǎo)體提供的 BMF 系列 34mm 和 62mm 半橋模塊是這一趨勢(shì)的代表 。這種模塊化設(shè)計(jì)有助于降低系統(tǒng)寄生電感,從而在超高頻下實(shí)現(xiàn)更可靠的同步整流控制。

同時(shí),SiC 材料制造工藝的成熟,特別是晶圓尺寸從 6” 向8” 的邁進(jìn),預(yù)計(jì)將顯著降低 SiC 器件的制造成本 ,加速 SiC 同步整流技術(shù)在電動(dòng)汽車、能源存儲(chǔ)和工業(yè)電源中的普及。

5.3. 邁向更高的開(kāi)關(guān)頻率與極致效率

SiC 同步整流技術(shù)支持系統(tǒng)工作在更高的開(kāi)關(guān)頻率,從而能夠減小無(wú)源元件(如變壓器和電感)的體積和重量,實(shí)現(xiàn)更高的功率密度 。在現(xiàn)代世界,減少電力轉(zhuǎn)換過(guò)程中的損耗至關(guān)重要,因?yàn)樵诿總€(gè)轉(zhuǎn)換階段,總功率中約有 2% 至 15% 會(huì)以熱量的形式浪費(fèi) 。同步整流是實(shí)現(xiàn)下一代電力系統(tǒng)(如電動(dòng)汽車逆變器和高密度 DC-DC 轉(zhuǎn)換器)超過(guò) 99% 效率目標(biāo)的核心技術(shù)。

當(dāng) SiC SR 技術(shù)將半導(dǎo)體開(kāi)關(guān)和導(dǎo)通損耗最小化后,未來(lái)的效率瓶頸將轉(zhuǎn)向無(wú)源元件(如磁性元件和電容)和拓?fù)浣Y(jié)構(gòu)的固有損耗。這要求設(shè)計(jì)人員將精力集中在新型材料科學(xué)和拓?fù)浣Y(jié)構(gòu)創(chuàng)新上,以充分利用 SiC SR 所實(shí)現(xiàn)的超高開(kāi)關(guān)頻率。

5.4. 重點(diǎn)應(yīng)用領(lǐng)域與市場(chǎng)影響

SiC 同步整流技術(shù)在多個(gè)高增長(zhǎng)領(lǐng)域具有決定性影響:

電動(dòng)汽車(eMobility):應(yīng)用于高效車載充電器和主逆變器,利用 SiC 的高效率和高功率密度特性 。

工業(yè)應(yīng)用:包括新能源逆變器和高密度 DC-DC 轉(zhuǎn)換器 。

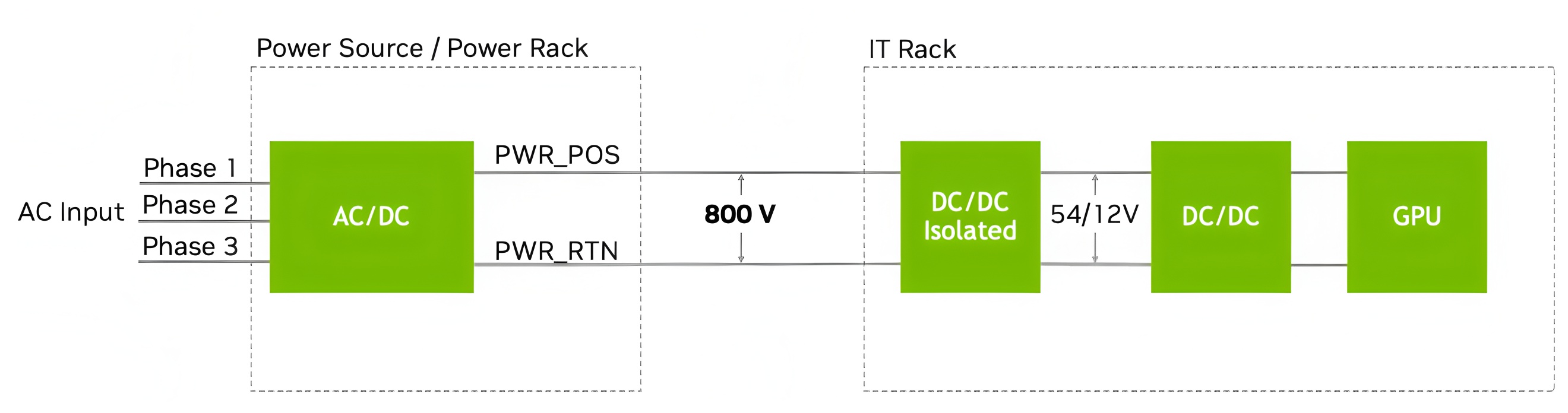

電網(wǎng)和能源:UPS 系統(tǒng)、數(shù)據(jù)中心電源、SST固態(tài)變壓器,大型能源存儲(chǔ)系統(tǒng),這些領(lǐng)域?qū)煽啃院蜆O致效率有最高要求 。

SiC SR 技術(shù)的普及和成熟正在重新定義電力電子系統(tǒng)的設(shè)計(jì)原則。過(guò)去的設(shè)計(jì)通常需要在開(kāi)關(guān)損耗和導(dǎo)通損耗之間進(jìn)行性能妥協(xié),并容忍二極管的固有缺陷。現(xiàn)在,SiC SR 使得設(shè)計(jì)者能夠同時(shí)最小化這兩種關(guān)鍵損耗,從而推動(dòng)電力電子設(shè)計(jì)從“妥協(xié)”轉(zhuǎn)向“性能驅(qū)動(dòng)”,加速實(shí)現(xiàn)更高電壓、更高頻率、更高功率密度的系統(tǒng)目標(biāo) 。

深圳市傾佳電子有限公司(簡(jiǎn)稱“傾佳電子”)是聚焦新能源與電力電子變革的核心推動(dòng)者:

傾佳電子成立于2018年,總部位于深圳福田區(qū),定位于功率半導(dǎo)體與新能源汽車連接器的專業(yè)分銷商,業(yè)務(wù)聚焦三大方向:

新能源:覆蓋光伏、儲(chǔ)能、充電基礎(chǔ)設(shè)施;

交通電動(dòng)化:服務(wù)新能源汽車三電系統(tǒng)(電控、電池、電機(jī))及高壓平臺(tái)升級(jí);

數(shù)字化轉(zhuǎn)型:支持AI算力電源、數(shù)據(jù)中心等新型電力電子應(yīng)用。

公司以“推動(dòng)國(guó)產(chǎn)SiC替代進(jìn)口、加速能源低碳轉(zhuǎn)型”為使命,響應(yīng)國(guó)家“雙碳”政策(碳達(dá)峰、碳中和),致力于降低電力電子系統(tǒng)能耗。

需求SiC碳化硅MOSFET單管及功率模塊,配套驅(qū)動(dòng)板及驅(qū)動(dòng)IC,請(qǐng)搜索傾佳電子楊茜

結(jié)論

在 1200V SiC MOSFET 橋式拓?fù)渲校瑔⒂猛秸鳎⊿R)模式并非僅是效率提升的優(yōu)化手段,而是基于 SiC 器件電學(xué)特性和高頻高功率系統(tǒng)性能要求的技術(shù)必然性。

1. 導(dǎo)通損耗危機(jī)是主要驅(qū)動(dòng)力:SiC MOSFET 固有的 PN 結(jié)體二極管在高工作結(jié)溫 (175°C) 下會(huì)產(chǎn)生高達(dá) 4.1V 至 5.1V 的導(dǎo)通壓降 VSD。在橋式電路的死區(qū)時(shí)間,若電流流經(jīng)體二極管,會(huì)造成巨大的傳導(dǎo)損耗,這在高功率、追求 99% 效率的系統(tǒng)中是不可接受的。啟用 SR 模式,利用低 RDS(on) 的溝道導(dǎo)通,可將等效導(dǎo)通壓降降低 50% 以上(至約 2.1V),從而實(shí)現(xiàn)導(dǎo)通損耗的最小化。

2. Qrr 消除是高頻可靠性的前提:盡管 SiC 器件的體二極管 Qrr 較低,但它在大電流下的反向恢復(fù)能量 Err 和峰值電流 Irrm(如 BMF540R12KA3 的 Irrm 高達(dá) 338A)仍然巨大,足以在高 di/dt 環(huán)境下引發(fā)嚴(yán)重的開(kāi)關(guān)損耗和過(guò)電壓尖峰。精確的同步整流控制通過(guò)完全避免體二極管導(dǎo)通,使得 Qrr≈0,徹底消除了反向恢復(fù)相關(guān)的開(kāi)關(guān)應(yīng)力和損耗。這是確保 SiC 器件能夠在 100kHz 甚至更高頻率下高效、安全運(yùn)行的絕對(duì)先決條件。

綜上所述,SiC 功率器件只有通過(guò)精密的同步整流控制,才能最大化其寬禁帶材料帶來(lái)的高速度和低電阻優(yōu)勢(shì)。同步整流不僅優(yōu)化了導(dǎo)通損耗,更保障了高頻開(kāi)關(guān)的可靠性,是實(shí)現(xiàn)下一代高功率密度和極致效率電力電子系統(tǒng)的核心技術(shù)支柱。

審核編輯 黃宇

-

同步整流

+關(guān)注

關(guān)注

11文章

309瀏覽量

52105 -

SiC MOSFET

+關(guān)注

關(guān)注

1文章

168瀏覽量

6812

發(fā)布評(píng)論請(qǐng)先 登錄

傾佳電子高速風(fēng)機(jī)變頻器從IGBT向SiC模塊全面轉(zhuǎn)型的深度技術(shù)動(dòng)因分析報(bào)告

傾佳電子基于SiC MOSFET 的 3kW 高頻 (100kHz) CCM 圖騰柱 PFC 設(shè)計(jì)、分析與效率建模

傾佳電子壁掛式直流充電樁的架構(gòu)演進(jìn)與半導(dǎo)體技術(shù)前沿:拓?fù)?/b>、趨勢(shì)及SiC MOSFET應(yīng)用價(jià)值深度解析

傾佳電子碳化硅MOSFET高級(jí)柵極驅(qū)動(dòng)設(shè)計(jì):核心原理與未來(lái)趨勢(shì)綜合技術(shù)評(píng)述

傾佳電子單相戶用儲(chǔ)能逆變器中Heric拓?fù)?/b>的綜合分析及其SiC MOSFET應(yīng)用價(jià)值

傾佳電力電子設(shè)備高壓輔助電源拓?fù)?/b>、器件選型與1700V SiC MOSFET技術(shù)分析報(bào)告

傾佳電子商用電磁加熱技術(shù)革命:基本半導(dǎo)體34mm SiC MOSFET模塊加速取代傳統(tǒng)IGBT模塊

傾佳電子SiC廚房革命:B3M042140Z MOSFET取代RC-IGBT在電磁爐應(yīng)用中的技術(shù)與商業(yè)分析

傾佳電子碳化硅在電網(wǎng)穩(wěn)定技術(shù)中的崛起:SVG拓?fù)?/b>趨勢(shì)及SiC功率器件變革性價(jià)值的技術(shù)分析

傾佳電子SiC碳化硅MOSFET串?dāng)_抑制技術(shù):機(jī)理深度解析與基本半導(dǎo)體系級(jí)解決方案

傾佳電子碳化硅(SiC)技術(shù)賦能下的工業(yè)逆變焊機(jī):拓?fù)?/b>重構(gòu)、效能飛躍及系統(tǒng)級(jí)設(shè)計(jì)深度分析

傾佳電子深度洞察AIDC電源系統(tǒng)技術(shù)演進(jìn)與SiC MOSFET應(yīng)用價(jià)值分析

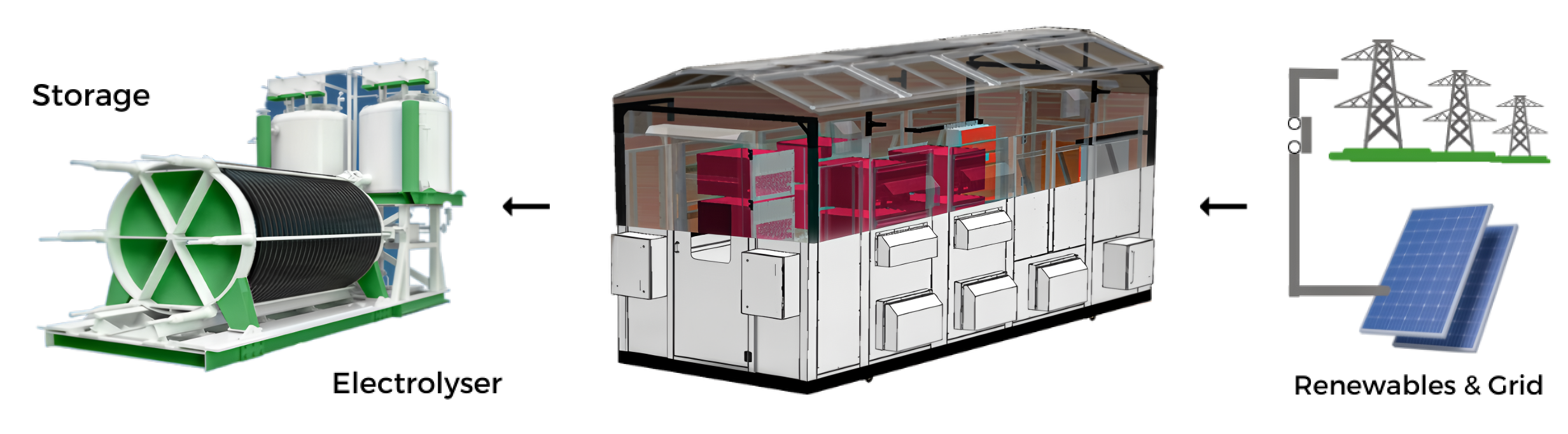

傾佳電子Hydrogen Rectifier制氫電源拓?fù)?/b>、技術(shù)演進(jìn)與SiC功率模塊的顛覆性作用

國(guó)產(chǎn)SiC碳化硅功率模塊全面取代進(jìn)口IGBT模塊的必然性

傾佳電子寬禁帶時(shí)代下的效率優(yōu)化:SiC MOSFET橋式拓?fù)渲型秸骷夹g(shù)的必然性與精確定量分析

傾佳電子寬禁帶時(shí)代下的效率優(yōu)化:SiC MOSFET橋式拓?fù)渲型秸骷夹g(shù)的必然性與精確定量分析

評(píng)論